特征

●500MHz單位增益帶寬

●低輸入偏置電流:2pA

●低偏移和漂移:±0.25mV,±2μV/°C

●低失真:在5MHz時為74dB SFDR

●高輸出電流:70mA

●低輸入電壓噪聲:7nV/√Hz

應(yīng)用

●寬帶光電二極管放大器

●采樣保持緩沖器

●CCD輸出緩沖器

●ADC輸入緩沖器

●寬帶精密放大器

●測量和測試

描述

OPA656結(jié)合了非常寬頻帶、統(tǒng)一增益穩(wěn)定、電壓反饋運(yùn)算放大器和FET輸入級,為ADC(模數(shù)轉(zhuǎn)換器)緩沖和瞬態(tài)應(yīng)用提供了超高動態(tài)范圍放大器。極低的直流誤差在光學(xué)應(yīng)用中具有很好的精度。

高單位增益穩(wěn)定帶寬和JFET輸入允許在高速低噪聲積分器中的卓越性能。

高輸入阻抗和低偏置電流由FET輸入由超低7nV/√Hz輸入電壓噪聲支持,以實現(xiàn)寬帶光電二極管瞬態(tài)應(yīng)用中非常低的集成噪聲。

鑒于OPA656的高230MHz增益帶寬產(chǎn)品,可以實現(xiàn)寬的瞬態(tài)帶寬。如下圖所示,即使47pF源電容的高1MΩ瞬態(tài)增益,也提供1MHz的a–3dB帶寬。

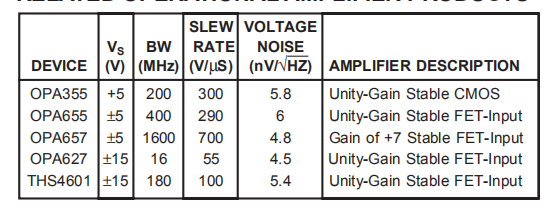

相關(guān)運(yùn)算放大器產(chǎn)品

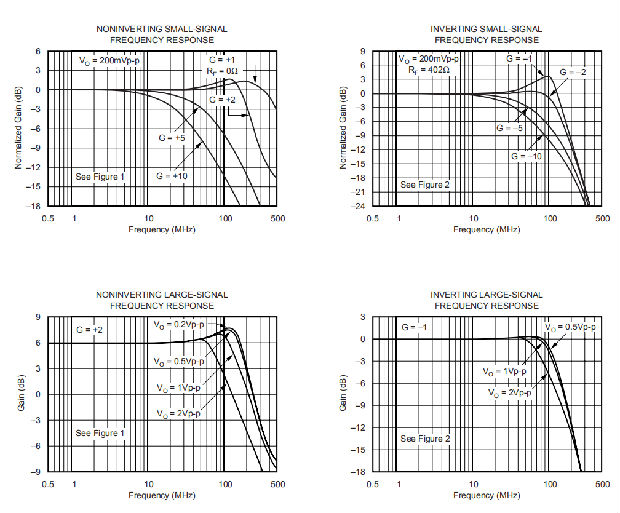

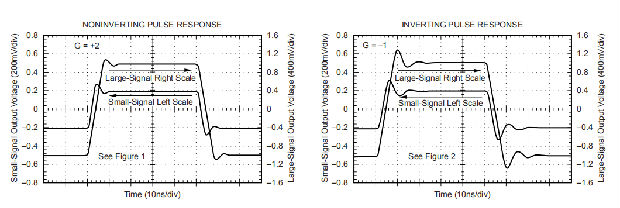

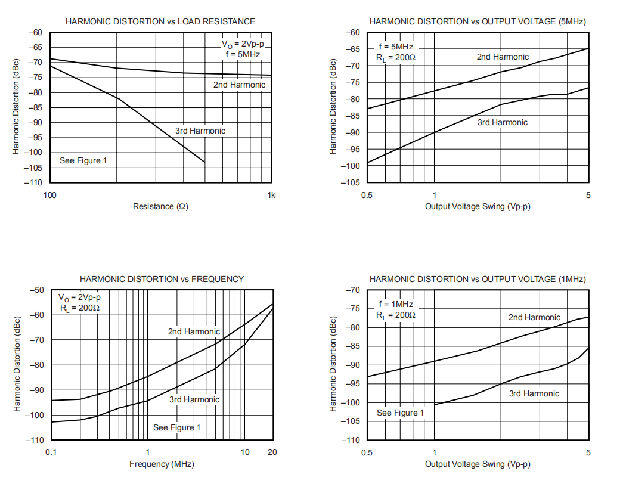

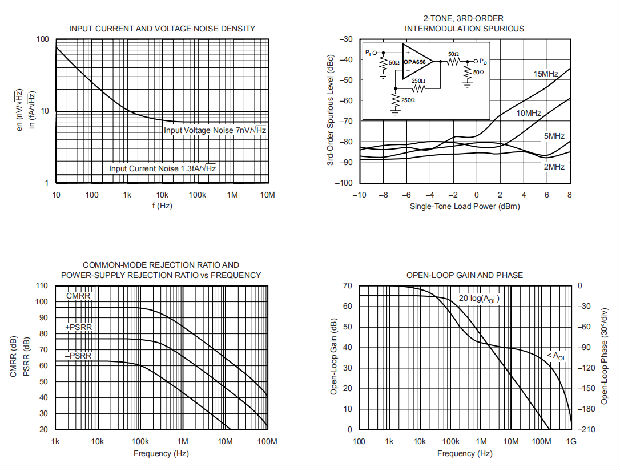

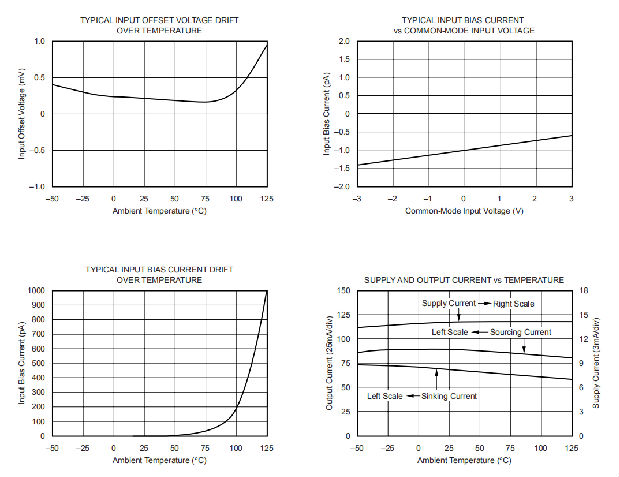

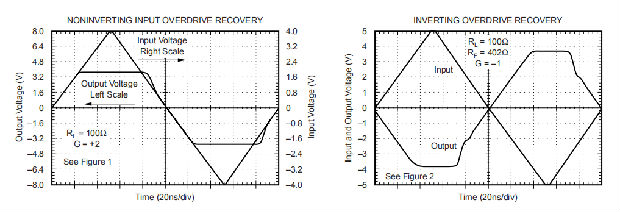

典型特性:VS=±5V

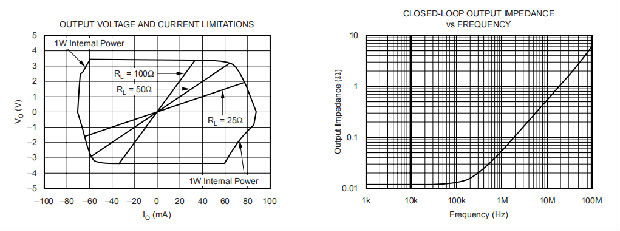

TA=+25°C,G=+2,RF=250Ω,RL=100Ω,除非另有說明。

應(yīng)用程序信息

寬帶、無眩操作

OPA656提供了一個獨特的組合寬帶,統(tǒng)一增益穩(wěn)定,電壓反饋放大器的直流精度的修剪JFET輸入階段。它的230MHz的高增益帶寬積(GBP)可用于為低增益緩沖器提供高信號帶寬,或向光電二極管檢測器應(yīng)用提供寬帶、低噪聲的瞬態(tài)帶寬。為了實現(xiàn)OPA656的全部性能,需要仔細(xì)注意印刷電路板(PCB)布局和部件選擇,如本數(shù)據(jù)表的其余部分所述。

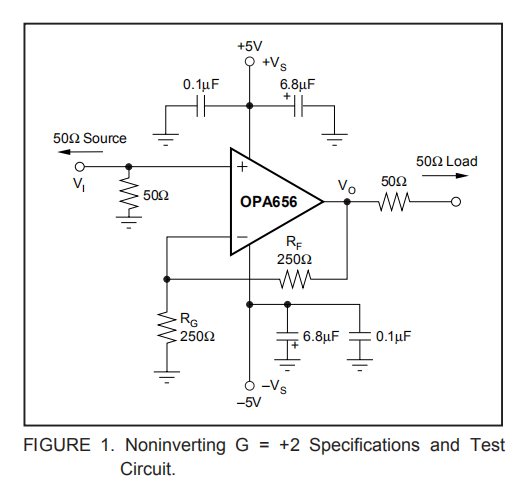

圖1顯示了+2電路的非侵入增益,該增益用作大多數(shù)典型特性的基礎(chǔ)。大多數(shù)曲線采用50Ω驅(qū)動阻抗的信號源進(jìn)行表征,測量設(shè)備顯示50Ω負(fù)載阻抗。圖1中,VI端子處的50Ω并聯(lián)電阻器與測試發(fā)電機(jī)的源阻抗匹配,而VO端子處的50Ω串聯(lián)電阻器為測量設(shè)備負(fù)載提供了匹配的電阻器。通常,數(shù)據(jù)表電壓擺動規(guī)格位于輸出引腳(圖1中的VO),而輸出功率規(guī)格在匹配的50Ω負(fù)載下。輸出處的總100Ω負(fù)載與500Ω總反饋網(wǎng)絡(luò)負(fù)載相結(jié)合,表示圖1電路的OPA656有效輸出負(fù)載為83Ω。

電壓反饋運(yùn)算放大器不同于電流反饋產(chǎn)品,可以使用廣泛的電阻值來設(shè)置其增益。為了保持圖1中非垂直電壓放大器的受控頻率響應(yīng),RF | RG的并行組合應(yīng)始終<200Ω。在非垂直配置中,RF | RG的并行組合將在OPA656的反轉(zhuǎn)節(jié)點(包括布局寄生)處形成具有寄生輸入電容的極。為了獲得最佳性能,該極點的頻率應(yīng)大于OPA656的閉環(huán)帶寬。因此,對于單位增益跟隨器應(yīng)用,建議直接從輸出到反向輸入短路。

寬帶、反轉(zhuǎn)增益運(yùn)算

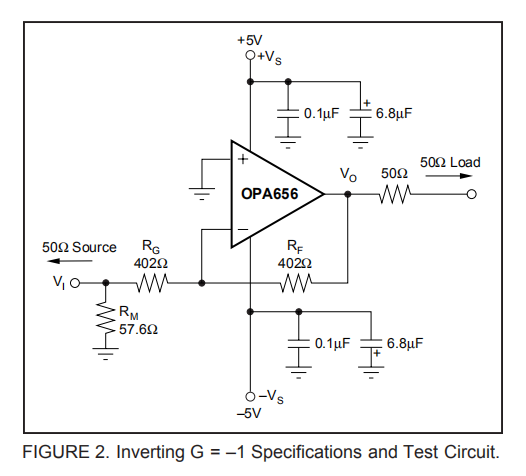

圖2的電路顯示了用于大多數(shù)逆變典型特性的–1測試電路的逆變增益。在這種情況下,使用附加電阻器RM來實現(xiàn)在表征中使用的測試設(shè)備所需的50Ω輸入阻抗。在電路板環(huán)境中,在電路板環(huán)境中,在前一級的輸出處,OPA656用作逆變放大器,該輸入阻抗匹配是可選的。

在這種配置中,輸出將反饋電阻器視為與用于測試的100Ω負(fù)載平行的附加負(fù)載。在限制RF | RG<200Ω并行組合的情況下,增加射頻值以減小輸出負(fù)載(改善諧波失真)通常是有用的。對于FET輸入OPA656提供的直流精度較高的反轉(zhuǎn)增益,請考慮更高的增益帶寬乘積OPA157。

圖2還顯示了直接連接到地面的非垂直輸入。通常,這里包括偏置電流對地電阻,以消除輸入偏置電流效應(yīng)引起的直流誤差。這僅在輸入偏置電流匹配時才有用。對于像OPA656這樣的JFET部件,輸入偏置電流不匹配,但其低到以(<5pA)開始,因此由于輸入偏置電流引起的直流誤差可以忽略不計。因此,對于逆變信號路徑條件,不建議在非轉(zhuǎn)動輸入處使用電阻器。

寬帶、高靈敏度、瞬態(tài)設(shè)計

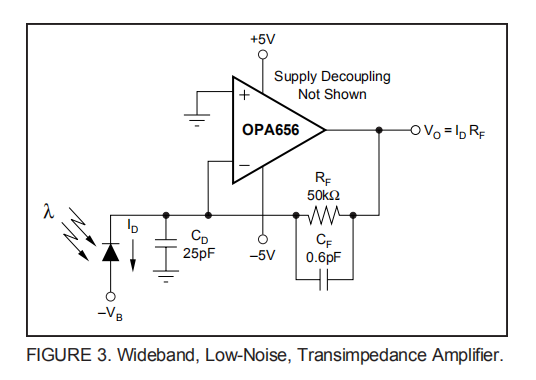

OPA656的高GBP低輸入電壓和電流噪聲使其成為低到中度瞬態(tài)增益的理想寬帶瞬態(tài)放大器。更高的瞬態(tài)增益(>100kΩ)將受益于諸如OPA656等FET輸入運(yùn)算放大器的低輸入噪聲電流。數(shù)據(jù)表首頁顯示了一個瞬態(tài)設(shè)計示例。大面積探測器需要高帶寬的設(shè)計將受益于OPA656的低輸入電壓噪聲。此輸入電壓噪聲二極管源電容使其在頻率上達(dá)到峰值,在許多情況下,它可以成為輸入靈敏度的限制因素。設(shè)計的關(guān)鍵要素是應(yīng)用反向偏置電壓(–VB)的預(yù)期二極管電容(CD)、所需的瞬態(tài)增益、RF和OPA656(230MHz)的GBP。圖3顯示了一個由25pF源電容二極管通過50kΩ瞬態(tài)增益進(jìn)行的設(shè)計。在設(shè)置這3個變量(包括將OPA656的寄生輸入電容添加到CD)的情況下,可以設(shè)置反饋電容值(CF)來控制頻率響應(yīng)。

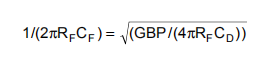

為了獲得最大平坦的二階巴特沃斯頻率響應(yīng),反饋極點應(yīng)設(shè)置為:

將共模和差分模式輸入電容(0.7+2.8)pF添加到圖3中的25pF二極管源電容中,并使用OPA156的230MHz GBP瞄準(zhǔn)50kΩ瞬態(tài)增益,則需要將反饋極設(shè)置為3.8MHz。這將需要總反饋電容為0.8pF。典型的表面安裝電阻器的寄生電容為0.2pF,留下圖3所需的0.6pF值,以獲得所需的反饋極。

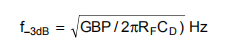

這將給出一個大約的–3dB帶寬設(shè)置為:

圖3的例子將給出使用0.6pF反饋補(bǔ)償?shù)拇蠹s5.7MHz平坦帶寬。

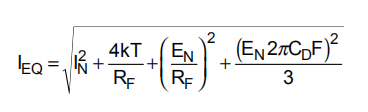

如果總輸出噪聲的頻帶限制為小于反饋極頻率(1/RFCF)的頻率,則等效輸入噪聲電流的一個非常簡單的表達(dá)式可以導(dǎo)出為:

式中:

iEQ=輸出噪聲帶寬限制為F<1/(2πRFCD)時的等效輸入噪聲電流。

iN=運(yùn)算放大器逆變輸入的輸入電流噪聲。

eN=運(yùn)算放大器的輸入電壓噪聲。

CD=二極管電容。

F=頻帶限制頻率,以赫茲為單位(通常在進(jìn)一步信號處理之前進(jìn)行后濾波)。

4kT=290°K時為1.6E–20J。

對于圖3電路,將此表達(dá)式計算為3.8MHz的反饋極頻率,給出了2.7pA/Hz的等效輸入噪聲電流。這遠(yuǎn)遠(yuǎn)高于1.3fA/HZOR,僅是運(yùn)算放大器本身。該結(jié)果主要由等效輸入噪聲電流表達(dá)式中的最后一項所支配。在這種情況下,使用低壓噪聲運(yùn)算放大器是非常必要的。

設(shè)計工具

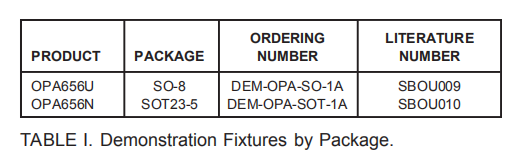

示范裝置

兩個印刷電路板(PCBs)可用于使用OPA656在其兩個封裝選項中協(xié)助初步評估電路性能。這兩種產(chǎn)品都是免費提供的,作為未受歡迎的多氯聯(lián)苯,并隨用戶指南交付。這些固定裝置的摘要信息如表I所示。

演示裝置可在德克薩斯儀器網(wǎng)站上申請(www.ti.com)通過OPA656產(chǎn)品文件夾。

操作建議

設(shè)置電阻器值以最小化噪音

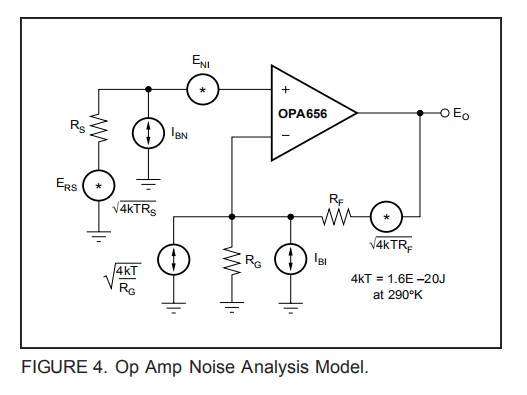

OPA656提供非常低的輸入噪聲電壓,同時需要低的14mA靜態(tài)電源電流。為了充分利用這種低輸入噪聲,需要仔細(xì)注意其他可能的噪聲因素。圖4顯示了包含所有噪聲項的運(yùn)算放大器噪聲分析模型。在該模型中,所有的噪聲項都被認(rèn)為是nV/Hz或pA/Hz的噪聲電壓或電流密度項。

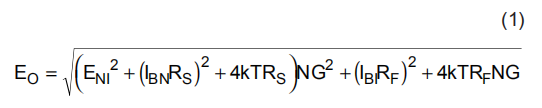

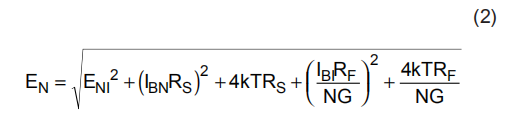

輸出點噪聲電壓的總值可以作為輸出噪聲電壓的平方根來計算。該計算通過疊加的方法,將輸出的所有噪聲功率相加,然后取平方根,恢復(fù)到點噪聲電壓。公式1顯示了使用圖4所示術(shù)語的輸出噪聲電壓的一般形式。

將該表達(dá)式除以噪聲增益(GN=1+RF/RG)將給出非垂直輸入處的等效輸入?yún)⒖键c噪聲電壓,如公式2所示。

將高電阻值放入公式2可以快速控制總等效輸入?yún)⒖荚肼暋7寝D(zhuǎn)動輸入3kΩ上的源阻抗將添加一個約翰遜電壓噪聲項,等于放大器本身的電壓噪聲項(7nV/Hz)。雖然OPA656的JFET輸入是高源阻抗應(yīng)用的理想選擇,但總體帶寬和噪聲都將受到圖1中非垂直配置中較高源阻抗的限制。

頻率響應(yīng)控制

電壓反饋運(yùn)算放大器,如OPA656顯示出隨著信號增益的增加信號帶寬的減小。理論上,這種關(guān)系由電特性中所示的GBP來描述。理想情況下,將GBP除以非轉(zhuǎn)動信號增益(也稱為噪聲增益,或NG)將預(yù)測閉環(huán)帶寬。實際上,這僅在相位裕度接近90°時才成立,就像在高增益配置中一樣。在低增益(增加反饋因子)時,大多數(shù)高速放大器將顯示出較復(fù)雜的響應(yīng),相位裕度較低。補(bǔ)償OPA156,以在+2的非轉(zhuǎn)動增益下給出最大平坦的2階巴特沃斯閉環(huán)響應(yīng)(圖1)。這導(dǎo)致了典型的+2帶寬200MHz的增益,遠(yuǎn)遠(yuǎn)超過了230MHz GBP除以2的預(yù)測。增加增益將導(dǎo)致相位裕度接近90°,帶寬將更接近(GBP/NG)的預(yù)測值。在+10的增益下,OPA656將顯示使用簡單公式預(yù)測的23MHz帶寬和230MHz的典型GBP。

單位增益穩(wěn)定的運(yùn)算放大器,如OPA656也可以使用電容器限制在反饋電阻器。對于圖1中的非垂直配置,通過反饋電阻器的電容器將隨著頻率降低到+1的增益而減小增益。例如,為了將+2設(shè)計的增益限制為20MHz,可以將32pF電容器與250Ω反饋電阻器并聯(lián)放置。然而,這只會將增益從2減少到1。在圖2的反轉(zhuǎn)配置中,使用反饋電容來限制信號帶寬更有效。在圖2的反饋中添加相同的電容器將在20MHz的信號頻率響應(yīng)中設(shè)置一個極點,但在這種情況下,它將繼續(xù)將信號增益衰減到1以下。然而,由于OPA656的輸入電壓噪聲而產(chǎn)生的輸出噪聲貢獻(xiàn)仍然只會隨著反饋電容器的添加而減小到1的增益。

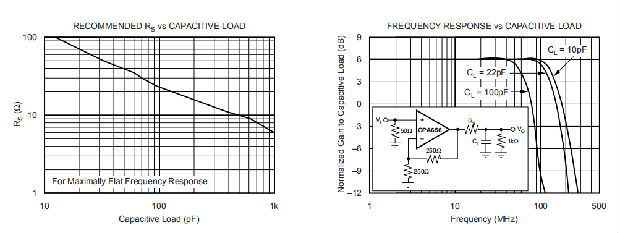

驅(qū)動電容負(fù)載

電容負(fù)載是運(yùn)算放大器最苛刻、但最常見的負(fù)載條件之一。通常,電容負(fù)載是ADC的輸入,包括可建議用于改善ADC線性度的附加外部電容。高速高開環(huán)增益放大器,如OPA656,當(dāng)電容負(fù)載直接放置在輸出引腳上時,很容易受到穩(wěn)定性下降和閉環(huán)響應(yīng)峰值的影響。當(dāng)考慮放大器的開環(huán)輸出電阻時,這種電容負(fù)載在信號路徑中引入了一個附加的極點,從而降低相位裕度。對這個問題提出了一些外部解決辦法。當(dāng)主要考慮頻率響應(yīng)平坦度、脈沖響應(yīng)保真度和/或失真時,最簡單和最有效的解決方案是在放大器輸出和電容負(fù)載之間插入串聯(lián)隔離電阻器,將電容負(fù)載與反饋回路隔離。這不會消除環(huán)響應(yīng)中的極點,而是將其移位,并在更高頻率處添加零。附加零起到消除電容負(fù)載極相位滯后的作用,從而提高相位裕度,提高穩(wěn)定性。

典型特性顯示了推薦的RS與電容負(fù)載以及由此產(chǎn)生的負(fù)載頻率響應(yīng)。在這種情況下,使用了最大平坦頻率響應(yīng)的設(shè)計目標(biāo)。如果可以容忍某些峰值,則可以使用較低的RS值。此外,在較高增益(比典型特性中使用的+2)運(yùn)行時,對于最小峰值頻率響應(yīng),需要更低的RS值。寄生電容負(fù)載大于2pF可開始降低OPA656的性能。長PC板跟蹤、不匹配電纜和多個設(shè)備的連接很容易導(dǎo)致超出此值。始終仔細(xì)考慮此效果,并盡可能將推薦的串聯(lián)電阻器添加到OPA656輸出引腳(參見板布局部分)。

失真性能

OPA656能夠在廣泛增益范圍內(nèi)以高頻方式傳送低失真信號。典型特征的畸變圖顯示了在各種條件下的典型畸變。

一般來說,在基波達(dá)到非常高的頻率或功率之前,第二次諧波將以可忽略的三次諧波分量來控制失真。然后,將重點放在二次諧波上,增加負(fù)載阻抗直接改善畸變。請記住,總負(fù)載包括非侵入配置中的反饋網(wǎng)絡(luò),這是RF+RG的總和,而在反轉(zhuǎn)配置中,這只是RF(見圖1)。輸出電壓擺動的增加直接增加諧波失真。輸出擺幅增加6dB通常會增加2次諧波12dB和3次諧波18dB。增加信號增益也會增加二次諧波失真。增益增加6dB,即使輸出功率和頻率恒定,也會使2、3次諧波增加約6dB。最后,由于環(huán)路增益隨頻率的衰減,隨著基頻的增加,失真增大。相反,失真將在大約100kHz時改善到較低頻率下的主開環(huán)極。從-70dBc 2次諧波(5MHz)開始,2VPP基波在G=+2(從典型特性)下變成200Ω負(fù)載,低于100kHz的頻率的第2次諧波失真將小于–105dBc。

OPA656具有極低的三階諧波失真。這也顯示在2色調(diào)三階互調(diào)假調(diào)(IM3)響應(yīng)曲線中。在低輸出功率水平下,三階假電平極低(<-80dBc)。即使基本功率達(dá)到更高水平,輸出階段仍保持低水平。典型的特征表明,假互調(diào)功率沒有傳統(tǒng)截獲模型預(yù)測的那樣增加。隨著基本功率水平的增加,動態(tài)范圍沒有顯著減小。對于以10MHz為中心的2個音調(diào),4dBm/音調(diào)至匹配的50Ω負(fù)載(即,負(fù)載時每個音調(diào)1VPP,輸出引腳處的整個2音包絡(luò)要求4VPP),典型特性顯示測試音調(diào)與3階互調(diào)假電平之間的78dBc差。在低頻和/或更高負(fù)載阻抗下工作時,這種特殊性能進(jìn)一步提高。

直流精度和偏移控制

OPA656具有開環(huán)增益高、共模抑制高、電源抑制高、輸入偏置電壓(漂移)小、輸入偏置電流小而可忽略的誤差等優(yōu)點,可提供優(yōu)良的直流精度。為了獲得最佳直流精度,高等級版本(OPA65UB或OPA656NB)將關(guān)鍵直流參數(shù)篩選到更嚴(yán)格的限制。標(biāo)準(zhǔn)和高等級版本都利用了新的最終測試技術(shù),100%測試輸入偏置電壓漂移超過溫度。本討論將使用高級典型和最小/最大電氣特性進(jìn)行說明;但是,標(biāo)準(zhǔn)等級版本適用相同的分析。

任何配置和溫度下的總輸出直流偏置電壓將是多種可能的誤差項的組合。在像OPA656這樣的JFET部分,輸入偏置電流項通常很低,但是不匹配的。采用偏置電流抵消技術(shù),在雙極輸入放大器中更為典型,不會改善輸出直流偏置誤差。由于輸入偏置電流引起的誤差僅在高溫下才成為主導(dǎo)。OPA656顯示出JFET輸入級放大器每10°C的典型2x增加。使用25°C時的5pA最大測試值和20°C內(nèi)部自加熱(參見熱分析),85°C環(huán)境下的最大輸入偏置電流將為5pA•2(105–25)/10=1280pA。對于非垂直配置,此術(shù)語僅開始是源阻抗>750kΩ的輸入偏置電壓的有效項。這也將是瞬態(tài)應(yīng)用的反饋電阻值(見圖3),其中,由于逆變輸入偏置電流產(chǎn)生的輸出直流誤差按輸入偏置電壓的貢獻(xiàn)順序。一般來說,除了這些極高的阻抗值外,輸入偏置電流引起的輸出直流誤差可以忽略。

輸入偏置電壓本身之后,對輸出偏置電壓的影響最大的項是負(fù)電源的PSRR。該術(shù)語被建模為由于負(fù)電源電壓(以及+PSRR)變化而引起的輸入偏置電壓偏移。–PSRR的高等級測試限值為62dB。這轉(zhuǎn)換為1.59mV/V輸入偏置電壓移位=10(–62/20)。在最壞情況下,負(fù)電源電壓的±0.38V(±7.6%)偏移將產(chǎn)生±0.6mV的視輸入偏置電壓偏移。由于這與±0.6mV輸入偏置電壓的測試限值相當(dāng),因此需要仔細(xì)控制負(fù)電源電壓。+PSRR測試至最小值74dB。這轉(zhuǎn)化為輸入偏置電壓對正電源變化的10(–74/20)=0.2mV/V靈敏度。

例如,計算圖1中25°C下的瞬態(tài)電路的最壞輸出直流誤差,然后在0°C至70°C范圍內(nèi)的偏移給出以下假設(shè)。

負(fù)電源

=-5V±0.2V,帶±5mV/°C最壞換檔正極電源

=+5V±0.2V,帶±5mV/°C最壞情況換檔初始25°C輸出直流誤差帶

=±0.3mV(由于–PSRR=1.59mV/V•±0.2V)

±0.04mV(由于+PSRR=0.2mV/V•±0.2V)

±0.6mV輸入偏置電壓

總計=±0.94mV

這將是在25°C驗收試驗條件下,批量生產(chǎn)中最壞的誤差帶。

在0°C至70°C的溫度范圍內(nèi),我們可以預(yù)期以下最壞情況從初始值轉(zhuǎn)移。此處假定為20°C內(nèi)部結(jié)自加熱。

±0.36mV(OPA656高級輸入偏移漂移)=±6μV/°C•(70°C+20°C–25°C))

±0.23mV(–60dB的PSRR,5mV•(70°C–25°C)電源切換)

±0.06mV(+PSRR為72dB,5mV•(70°C–25°C)電源切換)

總計=±0.65mV

這將是在規(guī)定條件下,從初始偏移超過0°C到70°C環(huán)境的最壞情況。典型的初始輸出直流誤差帶和溫度漂移將大大低于這些最壞情況估計。

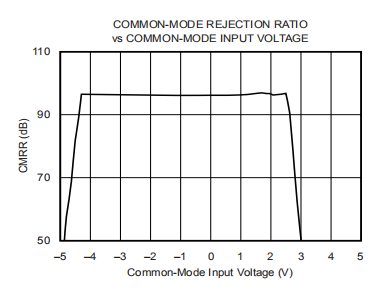

在瞬態(tài)配置中,由于輸入共模電壓保持在地面,因此可以忽略CMRR誤差。對于非垂直增益配置(見圖1),需要考慮CMRR項,但通常會遠(yuǎn)低于輸入偏置電壓項。在測試最小80dB(100μV/V)的情況下,圖1電路±2V輸入擺動增加的視在直流誤差不超過±0.2mV。

電源注意事項

OPA656用于±5V電源上的操作。允許單電源操作,從規(guī)定的規(guī)格和性能從單一+8V到+12V最大值變化最小。降低電源電壓操作的限制是JFET輸入級可用的輸入電壓范圍。從+12V的單一電源操作可以有許多優(yōu)點。在地面負(fù)電源的情況下,可將–PSRR項引起的直流誤差降至最低。通常,在+12V操作時,交流性能略有改善,電源電流的增加最小。

熱分析

OPA656在大多數(shù)應(yīng)用中不需要散熱或氣流。最大允許的結(jié)溫將設(shè)置允許的最大內(nèi)部功耗,如下所述。在任何情況下,最大連接溫度不得超過150°C。

工作結(jié)溫度(TJ)由TA+PD•θJA給出。總內(nèi)部功耗(PD)是靜態(tài)功率(PDQ)和輸出階段(PDL)中為提供負(fù)載功率而消耗的附加功率之和。靜態(tài)電源只是指定的空載供電電流乘以整個部件的總電源電壓。PDL將取決于所需的輸出信號和負(fù)載,但對于接地電阻負(fù)載,當(dāng)輸出固定在等于任一電源電壓的1/2的電壓(對于相等雙極電源)的電壓下時,PDL將處于最大值。在此條件下,PDL=VS2/(4•RL),其中RL包括反饋網(wǎng)絡(luò)加載。

注意,是輸出階段的功率而不是負(fù)載決定內(nèi)部功耗。

作為最壞的例子,使用圖1電路中OPA65N(SOT3-5包)計算最大TJ,該電路在+85°C的最大指定環(huán)境溫度下運(yùn)行,并驅(qū)動接地100Ω負(fù)載。

PD=10V•16.1mA+52/(4•(100Ω| 800Ω))=231mW

最大TJ=+85°C+(0.23W•150°C/W)=120°C。

所有實際應(yīng)用將在較低的內(nèi)部功率和結(jié)溫下運(yùn)行。

板布局

要想獲得最佳性能,使用像OPA656這樣的高頻放大器,需要仔細(xì)注意板布局寄生和外部組件類型。將優(yōu)化業(yè)績的建議包括:

a)最小化寄生電容至所有信號I/O引腳的任何交流接地。輸出端和逆變輸入引腳上的寄生電容會導(dǎo)致非轉(zhuǎn)動輸入不穩(wěn)定,它會與源阻抗發(fā)生反應(yīng),造成無意的帶限。為了減少不需要的電容,應(yīng)在所有接地和電源平面上打開信號I/O引腳周圍的窗口。否則,地面和動力飛機(jī)應(yīng)在船上的其他地方不間斷。

b)最小化距離(<0.25”)從電源引腳到高頻0.1U F解耦電容器。在設(shè)備引腳處,接地和電源平面布局不應(yīng)靠近信號I/O引腳。避免窄功率和接地痕跡,以最小化引腳和解耦電容器之間的電感。電源連接應(yīng)始終與這些電容器解耦。更大(2.2μF至6.8μF)的去耦電容器,在低頻有效,也應(yīng)用于電源引腳上。這些可以放置在離設(shè)備稍遠(yuǎn)的地方,并且可以在PC板的同一區(qū)域的多個設(shè)備之間共享。

c)仔細(xì)選擇和放置外部部件將保持OPA156的高頻性能。電阻器應(yīng)為極低電抗類型。表面安裝電阻器工作最好,并允許更緊密的整體布局。金屬薄膜和碳組分軸向引線電阻也能提供良好的高頻性能。同樣,盡可能短地保持導(dǎo)線和PCB跟蹤長度。在高頻應(yīng)用中,切勿使用線繞式電阻器。由于輸出引腳和逆變輸入引腳對寄生電容最敏感,因此始終將反饋和串聯(lián)輸出電阻器(如果有的話)盡可能靠近輸出引腳。其他網(wǎng)絡(luò)組件,例如無轉(zhuǎn)動輸入端接電阻器,也應(yīng)放置在靠近封裝的位置。如果允許雙面組件安裝,則將反饋電阻器直接置于板另一側(cè)的封裝下方,位于輸出端和反轉(zhuǎn)輸入引腳之間。即使在低寄生電容分流外部電阻器時,過高的電阻值也會產(chǎn)生顯著的時間常數(shù),從而降低性能。良好的軸向金屬薄膜或表面卸荷電阻器與電阻器并聯(lián)時的并聯(lián)電阻約為0.2pF。對于電阻值>1.5kΩ,該寄生電容可在500 MHz以下添加一個極和/或零,從而影響電路操作。保持電阻值盡可能低,以符合負(fù)載驅(qū)動考慮。這里建議,設(shè)計的一個好起點是保持射頻| RG<250Ω,用于電壓放大器應(yīng)用。這樣做將自動保持電阻噪聲項低,并最小化其寄生電容的影響。只要考慮到逆變節(jié)點上的所有寄生電容項設(shè)置反饋補(bǔ)償電容,則瞬態(tài)應(yīng)用程序(見圖3)可以使用應(yīng)用程序所需的任何反饋電阻器。

d)與其他寬帶設(shè)備的連接在板上可采用短直接跟蹤或通過車載傳輸線。對于短連接,將跟蹤和下一個設(shè)備的輸入視為集總電容負(fù)載。應(yīng)使用相對較寬的痕跡(50mils至100mils),最好在周圍打開地面和電源平面。從推薦RS與電容負(fù)載的圖中估計總電容負(fù)載和設(shè)置RS。低寄生電容負(fù)載(<5pF)可能不需要RS,因為OPA656名義上被補(bǔ)償為使用2pF寄生負(fù)載運(yùn)行。如果需要長跟蹤,則允許在信號增益增加(增加空載相位裕度)的情況下,允許無RS的更高寄生電容負(fù)載,且雙端傳輸線固有的6dB信號損耗是可接受的,使用微帶或帶狀線技術(shù)實現(xiàn)匹配阻抗傳輸線(請參閱ECL微帶和帶狀線布局技術(shù)設(shè)計手冊)。通常,船上不需要50Ω環(huán)境,事實上,高阻抗環(huán)境將改善失真,如畸變與負(fù)載圖所示。根據(jù)板料和跟蹤尺寸定義的特征板跟蹤阻抗,使用從OPA656的輸出進(jìn)入跟蹤的匹配串聯(lián)電阻器以及目的裝置輸入端接并聯(lián)電阻器。同時,端接阻抗將是并聯(lián)電阻和目標(biāo)設(shè)備輸入阻抗的并聯(lián)組合-應(yīng)設(shè)置此總有效阻抗以匹配跟蹤阻抗。如果雙端傳輸線的6dB衰減不可接受,則只能在源端串聯(lián)終止長跟蹤。在這種情況下,將跟蹤視為電容負(fù)載,并設(shè)置串聯(lián)電阻值,如建議RS與電容負(fù)載的圖所示。這將不會保持信號完整性以及雙端接線路。如果目標(biāo)設(shè)備的輸入阻抗低,則由于串聯(lián)輸出形成的分壓器形成的分壓器,將產(chǎn)生信號衰減,從而進(jìn)入終端阻抗。

e)不建議插入OPA656這樣的高速零件。插座引入的附加引線長度和針對腳電容,可以產(chǎn)生一個極其麻煩的寄生網(wǎng)絡(luò),這幾乎不可能實現(xiàn)平穩(wěn)、穩(wěn)定的頻率響應(yīng)。將OPA656焊接到板上,可獲得最佳結(jié)果。

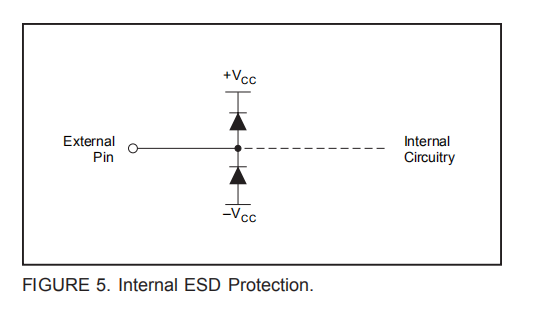

輸入和ESD保護(hù)

OPA656是建立在一個非常高速互補(bǔ)雙極工藝。對于這些非常小的幾何器件,內(nèi)部結(jié)擊穿電壓相對較低。這些細(xì)分反映在絕對最大評級表中。如圖5所示,所有設(shè)備引腳都由內(nèi)部ESD保護(hù)二極管保護(hù)電源。

這些二極管提供適度的保護(hù),以輸入高于電源的過驅(qū)動電壓。保護(hù)二極管通常可支持30mA連續(xù)電流。如果可能有更高的電流(例如,在帶有±12V電源部件驅(qū)動至OPA656的系統(tǒng)中),應(yīng)在兩個輸入端添加限流串聯(lián)電阻器。保持這些電阻值盡可能低,因為高值會降低噪聲性能和頻率響應(yīng)。

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國產(chǎn)降成本等解決方案,可承接項目開發(fā),以及元器件一站式采購服務(wù),類型有運(yùn)放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1