特征

•極低偏移漂移:最大1μV/°C

•極低偏移:120μV

•低輸入偏置電流:最大10 pA

•非常低的1/f噪聲:250 nVPP,0.1 Hz至10 Hz

•低噪聲:5.1 nV/√Hz

•轉(zhuǎn)換速率:20 V/μs

•低電源電流:最大2 mA

•輸入電壓范圍包括V電源

•單電源操作:4.5 V至36 V

•雙電源操作:±2.25 V至±18 V

•無相位反轉(zhuǎn)

•行業(yè)標準SOIC封裝

•VSSOP、TSSOP和SOT-23包

應(yīng)用

•電池供電儀器

•工業(yè)控制

•醫(yī)療器械

•光電二極管放大器

•有源濾波器

•數(shù)據(jù)采集系統(tǒng)

•自動測試系統(tǒng)

說明

OPA140、OPA2140和OPA4140運算放大器(op-amp)系列是一系列低功耗JFET輸入放大器,具有良好的漂移和低輸入偏置電流。軌道到軌道的輸出擺幅和輸入范圍,包括V-允許設(shè)計師利用JFET放大器的低噪聲特性,同時也與現(xiàn)代的單電源精密模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)接口。

OPA140實現(xiàn)了11mhz單位增益帶寬和20v/μs的轉(zhuǎn)換速率,而靜態(tài)電流僅消耗1.8ma(典型值)。它使用單個4.5-V至36-V電源或雙路±2.25-V至±18-V電源。

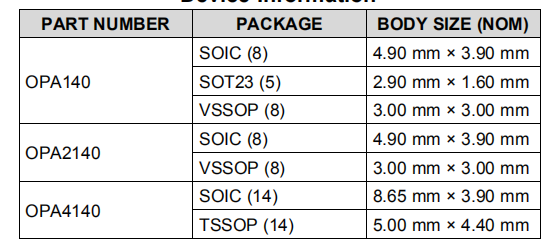

所有版本的溫度均為-40°C至125°C,適用于最具挑戰(zhàn)性的環(huán)境。OPA140(單)有5針SOT-23、8針VSSOP和8針SOIC封裝;OPA2140(雙)有8針VSSOP和8針SOIC封裝;OPA4140(四芯)有14針SOIC和14針TSSOP封裝。

設(shè)備信息

(1)、有關(guān)所有可用的軟件包,請參閱數(shù)據(jù)表末尾的訂購附錄。

典型特征

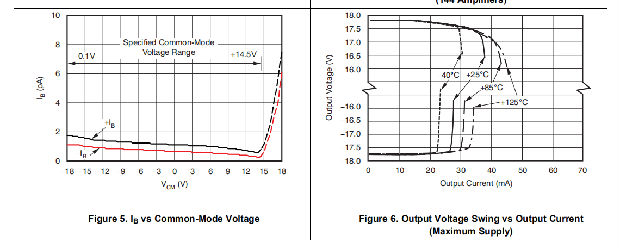

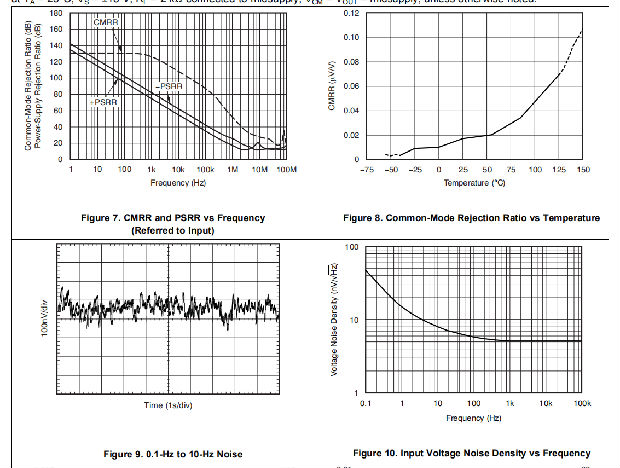

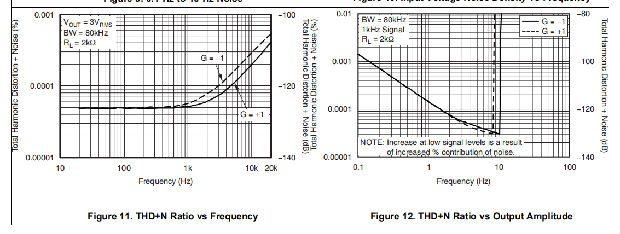

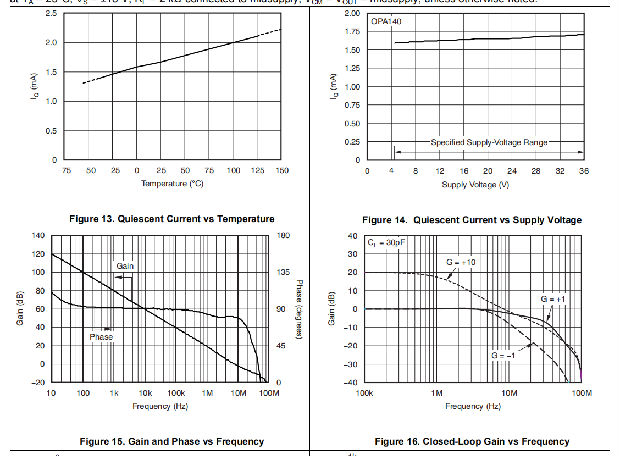

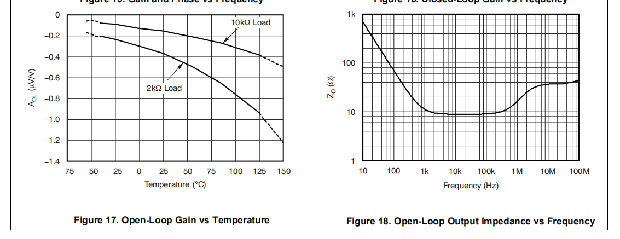

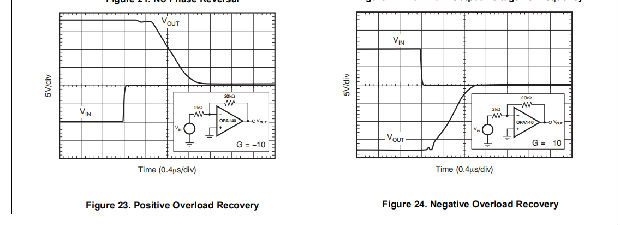

除非另有說明,否則在TA=25°C,VS=±18 V,RL=2 kΩ,連接到中間電源,VCM=VOUT=MID SUPPLY。

詳細說明

概述

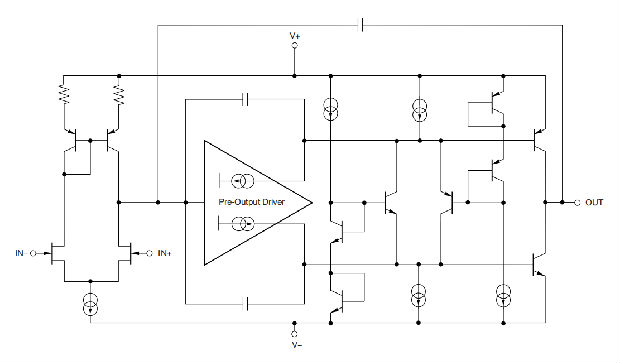

OPAx140系列運算放大器是一系列低功耗JFET輸入放大器,具有優(yōu)異的漂移性能和低輸入偏置電流。軌道到軌道的輸出擺幅和輸入范圍,包括V-允許設(shè)計人員使用JFET放大器的低噪聲特性,同時也與現(xiàn)代的單電源精密模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)接口。OPAx140系列達到11MHz單位增益帶寬和20V/μs轉(zhuǎn)換率,僅消耗1.8mA(典型)的靜態(tài)電流。這些裝置在單個4.5-V至36-V電源或雙路±2.25-V至±18-V電源上運行。

功能框圖部分顯示了OPAx140的簡化圖。

功能框圖

功能描述

工作電壓

OPA140、OPA2140和OPA4140系列運算放大器可在VS=4.5V(±2.25V)和VS=36V(±18V)的工作范圍內(nèi)使用單電源或雙電源。這些設(shè)備不需要對稱供電;它們只需要4.5V(±2.25V)的最小供電電壓。對于VS小于±3.5 V,共模輸入范圍不包括中間電源。高于40 V的電源電壓會永久損壞設(shè)備;請參閱絕對最大額定值表。關(guān)鍵參數(shù)在工作溫度范圍內(nèi)規(guī)定,TA=–40°C至125°C。隨電源電壓或溫度范圍變化的關(guān)鍵參數(shù)見本數(shù)據(jù)表的典型特性部分。

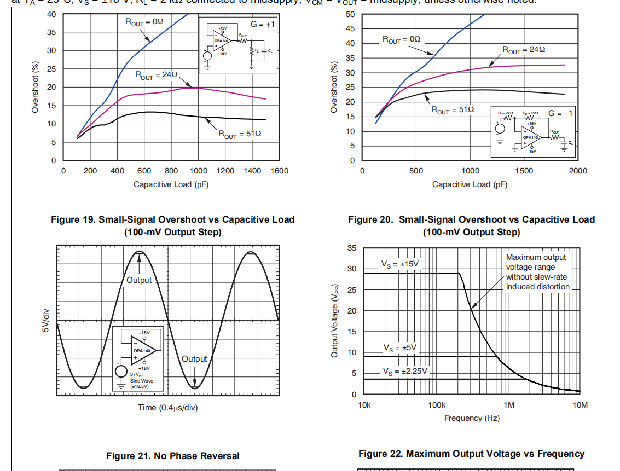

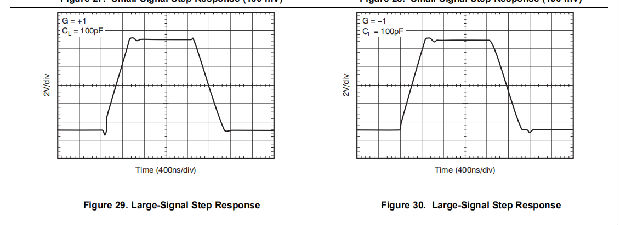

電容性負載與穩(wěn)定性

OPAx140的動態(tài)特性已經(jīng)針對常見的增益、負載和操作條件進行了優(yōu)化。低閉環(huán)增益和高容性負載的結(jié)合降低了放大器的相位裕度,并可能導(dǎo)致增益峰值或振蕩。因此,較重的電容性負載必須與輸出隔離。實現(xiàn)這種隔離的最簡單方法是在輸出端串聯(lián)一個小電阻(例如,ROUT等于50Ω)。

圖19和圖20顯示了幾個ROUT值的小信號超調(diào)與電容性負載的關(guān)系圖。此外,有關(guān)分析技術(shù)和應(yīng)用電路的詳細信息,請參閱應(yīng)用注釋“反饋圖定義運算放大器交流性能”(SBOA015,可從TI網(wǎng)站下載)。

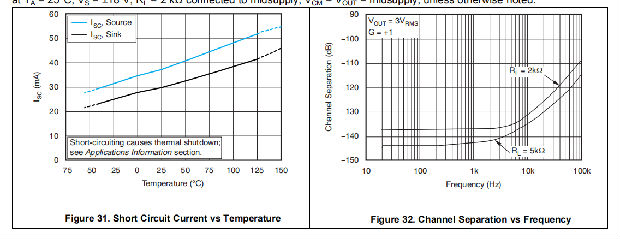

輸出電流限制

OPAx140系列的輸出電流被內(nèi)部電路限制在36毫安/–30毫安(源/陷),以便在輸出意外短路時保護設(shè)備。短路電流取決于溫度,如圖31所示。

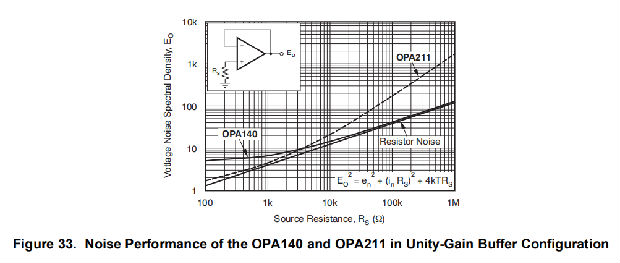

噪聲性能

圖33顯示了在單位增益配置(沒有反饋電阻網(wǎng)絡(luò),因此沒有額外的噪聲貢獻)的運算放大器的源阻抗變化的總電路噪聲。圖中顯示了OPA140和OPA211,并計算了總電路噪聲。運算放大器本身提供電壓噪聲分量和電流噪聲分量。電壓噪聲通常被建模為偏置電壓的時變分量。電流噪聲被建模為輸入偏置電流的時變分量,并與源電阻反應(yīng)產(chǎn)生噪聲的電壓分量。因此,給定應(yīng)用的最低噪聲運算放大器取決于源阻抗。對于低源阻抗,電流噪聲可以忽略不計,而電壓噪聲通常占主導(dǎo)地位。由于運算放大器的FET輸入,OPA140、OPA2140和OPA4140系列具有低電壓噪聲和極低電流噪聲。因此,對于任何實際的源阻抗,OPAx140系列的電流噪聲貢獻可以忽略不計,這使得它成為高源阻抗應(yīng)用的更好選擇。

圖33中的方程式顯示了總電路噪聲的計算,這些參數(shù)如下:

•en=電壓噪聲

•In=電流噪聲

•RS=源阻抗

•k=玻爾茲曼常數(shù)=1.38×10–23 J/k

•T=溫度,單位:開氏度(K)

有關(guān)計算噪波的詳細信息,請參見基本噪波計算。

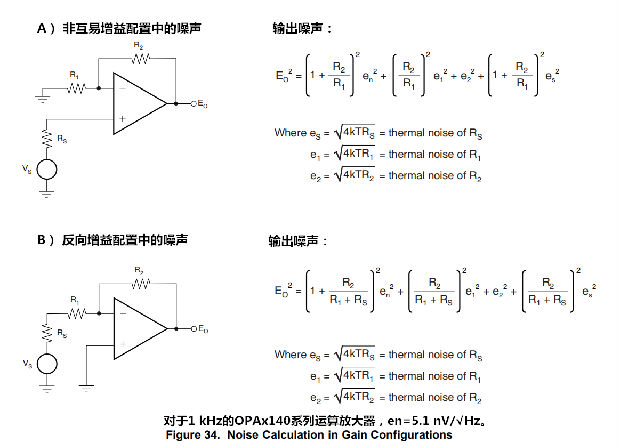

基本噪聲計算

低噪聲電路的設(shè)計需要仔細分析所有的噪聲源。在許多情況下,外部噪聲源占主導(dǎo)地位;考慮源電阻對運算放大器整體噪聲性能的影響。電路的總噪聲是所有噪聲分量的平方根和組合。

源阻抗的電阻部分產(chǎn)生與電阻平方根成比例的熱噪聲。該函數(shù)如圖33所示。源阻抗通常是固定的;因此,選擇運放和反饋電阻,以盡量減少各自對總噪聲的貢獻。

圖34說明了無反轉(zhuǎn)(A)和反轉(zhuǎn)(B)運算放大器電路的增益配置。在有增益的電路配置中,反饋網(wǎng)絡(luò)電阻也會產(chǎn)生噪聲。一般來說,運算放大器的電流噪聲與反饋電阻反應(yīng),產(chǎn)生額外的噪聲分量。然而,OPAx140的極低電流噪聲意味著其電流噪聲貢獻可以忽略不計。

通常可以選擇反饋電阻值,使這些噪聲源可以忽略不計。低阻抗反饋電阻負載放大器的輸出。給出了兩種結(jié)構(gòu)的總噪聲方程。

倒相保護

OPA140、OPA2140和OPA4140系列具有內(nèi)部相位反轉(zhuǎn)保護。許多FET和雙極性輸入運算放大器在輸入被驅(qū)動超過其線性共模范圍時會出現(xiàn)相位反轉(zhuǎn)。這種情況在非換向電路中最常見,當輸入被驅(qū)動到超過規(guī)定的共模電壓范圍時,導(dǎo)致輸出反向進入相反的軌道。OPA140、OPA2140和OPA4140的輸入電路可防止共模電壓過高時的相位反轉(zhuǎn);相反,輸入到相應(yīng)軌道的輸出限制(見圖21)。

熱防護

OPAx140系列運算放大器能夠在規(guī)定溫度范圍內(nèi)驅(qū)動2-kΩ負載,電源電壓高達±18 V。在單電源配置中,當負載連接到負電源電壓時,36 V電源電壓下的最小負載電阻為2.8 kΩ。對于較低的電源電壓(單電源或?qū)ΨQ電源),只要輸出電流不超過13 mA,就可以使用較低的負載電阻;否則,裝置短路電流保護電路可能激活。

在高電源電壓下工作時,內(nèi)部功耗增加。與傳統(tǒng)材料相比,OPA140、OPA2140和OPA4140系列設(shè)備中使用的銅引線框架結(jié)構(gòu)提高了散熱性。印刷電路板(PCB)布局也有助于降低結(jié)溫的可能增加。寬大的銅痕跡作為一個額外的散熱片有助于散熱。通過將設(shè)備直接焊接到PCB上而不是使用插座,可以進一步將溫升降到最低。

雖然輸出電流受到內(nèi)部保護電路的限制,但設(shè)備的一個或多個輸出通道意外短路會導(dǎo)致過熱。例如,當一個輸出對中間電源短路時,36毫安的典型短路電流導(dǎo)致在±18伏的電源下內(nèi)部功耗超過600毫瓦。

對于8針VSSOP封裝中的雙OPA2140(熱阻θJA=180°C/W),當兩個通道短路時,這種功耗將導(dǎo)致模具溫度高于環(huán)境溫度220°C。這種溫度升高會顯著降低設(shè)備的使用壽命。

為了防止過熱,OPAx140系列有一個內(nèi)部熱關(guān)機電路,當模具溫度超過大約180°C時,該電路會關(guān)閉設(shè)備。當該熱關(guān)機電路啟動時,15°C的內(nèi)置磁滯確保在設(shè)備再次開啟之前,模具溫度必須下降到大約165°C。

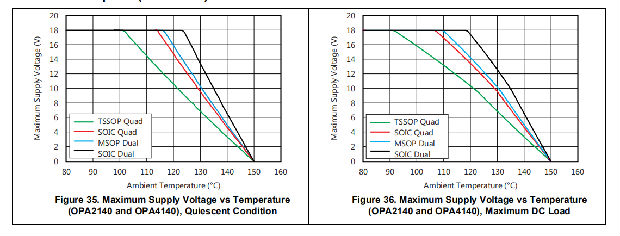

應(yīng)額外考慮最大工作電壓、最高工作溫度、負載和包裝類型的組合。圖35和圖36顯示了評估OPA2140(雙版本)和OPA4140(四版本)時的一些實際考慮。

例如,OPA4140的最大總靜態(tài)電流為10.8 mA(2.7 mA/通道)。14針TSSOP封裝的典型熱阻為135°C/W。此參數(shù)意味著,由于結(jié)溫不應(yīng)超過150°C,以確保可靠運行,必須降低電源電壓,或者環(huán)境溫度應(yīng)保持足夠低,以使結(jié)溫不超過150℃。圖35對各種封裝類型說明了這種情況。此外,輸出端的電阻負載會導(dǎo)致額外的功率損耗,從而產(chǎn)生自熱,在確定最大電源電壓或工作溫度時,也必須考慮到這一點。為此,圖36顯示了當直流負載電阻為2kΩ時,最大電源電壓與溫度的關(guān)系。

電氣過應(yīng)力

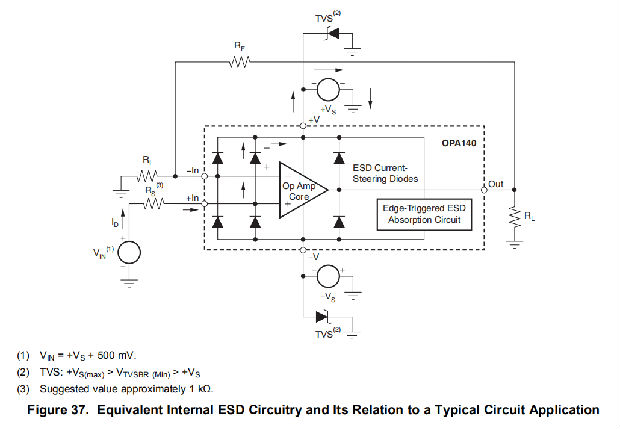

設(shè)計者經(jīng)常問運算放大器承受過大電應(yīng)力的能力。這些問題往往集中在設(shè)備輸入上,但可能涉及電源電壓引腳,甚至輸出引腳。每一種不同的引腳功能都具有由特定半導(dǎo)體制造工藝和連接到引腳的特定電路的電壓擊穿特性決定的電應(yīng)力極限。此外,內(nèi)部靜電放電(ESD)保護內(nèi)置在這些電路中,以防止在產(chǎn)品裝配之前和過程中發(fā)生意外的ESD事件。

有助于更好地理解這一基本的ESD電路及其與電氣過應(yīng)力事件的相關(guān)性。有關(guān)OPAx140系列中包含的ESD電路的圖示,請參見圖37(虛線區(qū)域表示)。ESD保護電路包括幾個電流控制二極管,這些二極管從輸入和輸出引腳連接,并返回內(nèi)部電源線,在那里它們在運算放大器內(nèi)部的吸收裝置處會合。該保護電路旨在在正常電路操作期間保持非活動狀態(tài)。

ESD事件產(chǎn)生一個持續(xù)時間短的高壓脈沖,當它通過半導(dǎo)體器件放電時,該脈沖被轉(zhuǎn)換成短時間的大電流脈沖。ESD保護電路設(shè)計用于在運算放大器核心周圍提供電流通路,以防止其損壞。保護電路吸收的能量隨后以熱量的形式散失。

當一個ESD電壓在兩個或多個放大器器件引腳上形成時,電流流過一個或多個轉(zhuǎn)向二極管。根據(jù)電流的路徑,吸收裝置可能會被激活。吸收裝置的觸發(fā)電壓或閾值電壓高于OPAx140的正常工作電壓,但低于器件擊穿電壓水平。一旦超過這個閾值,吸收裝置會迅速啟動,并將電源軌上的電壓保持在安全水平。

當運算放大器連接到如圖37所示的電路中時,ESD保護組件將保持不活動狀態(tài),而不會參與應(yīng)用電路的操作。然而,當外加電壓超過給定引腳的工作電壓范圍時,可能會出現(xiàn)這種情況。如果出現(xiàn)這種情況,則存在一些內(nèi)部ESD保護電路可能偏壓并傳導(dǎo)電流的風險。任何這樣的電流都是通過導(dǎo)向二極管路徑產(chǎn)生的,很少涉及吸收裝置。

圖37描述了一個具體的例子,其中輸入電壓(VIN)超過正電源電壓(+VS)500 mV或更多。電路中發(fā)生的大部分情況取決于電源特性。如果+VS可以吸收電流,則上部輸入轉(zhuǎn)向二極管中的一個將電流傳導(dǎo)并引導(dǎo)至+VS。過高的電流水平會隨著VIN的升高而流動。因此,數(shù)據(jù)表規(guī)格建議應(yīng)用程序?qū)⑤斎腚娏飨拗圃?0毫安。

如果電源不能吸收電流,VIN可以開始向運算放大器提供電流,然后作為正電源電壓源接管。這種情況下的危險是電壓可能上升到超過運算放大器絕對最大額定值的水平。

另一個常見的問題是,如果在電源+VS或–VS為0v時,輸入信號被應(yīng)用到輸入端,放大器會發(fā)生什么情況。

同樣,它取決于在0伏或低于輸入信號幅度的電平下的電源特性。如果電源顯示為高阻抗,則運算放大器電源電流可由輸入源通過電流控制二極管提供。這種狀態(tài)不是正常的偏壓狀態(tài);放大器很可能不會正常工作。如果電源阻抗低,則通過轉(zhuǎn)向二極管的電流可能會變得相當高。電流水平取決于輸入源傳輸電流的能力,以及輸入路徑中的任何電阻。

如果電源吸收電流的能力存在不確定性,可以在電源引腳上添加外部齊納二極管,如圖37所示。必須選擇齊納電壓,使二極管在正常運行期間不會打開。

然而,它的齊納電壓應(yīng)該足夠低,以便齊納二極管在電源引腳開始上升到高于安全工作電源電壓水平時導(dǎo)通。

電磁干擾抑制

電磁干擾抑制比(EMI)描述了運算放大器的EMI抗擾度。對許多運算放大器來說,一個常見的不利影響是射頻信號整流后偏移電壓的變化。一個運算放大器,如果能夠更有效地抑制EMI引起的偏移量變化,則它具有更高的EMIRR,并通過分貝值量化。測量EMIRR的方法有很多種,但本節(jié)提供EMIRR in+,它專門描述了當RF信號被應(yīng)用到運算放大器的非反轉(zhuǎn)輸入管腳時的EMIRR性能。一般來說,由于以下三個原因,僅對非轉(zhuǎn)換輸入進行EMIRR測試:

•眾所周知,運算放大器輸入引腳對EMI最敏感,通常比電源或輸出引腳更能校正射頻信號。

•無換向和逆變運算放大器輸入具有對稱的物理布局,并顯示出幾乎匹配的EMIRR性能。

•EMIRR在非轉(zhuǎn)換引腳上比在其他引腳上更容易測量,因為非轉(zhuǎn)換輸入端子可以在PCB上隔離。這種隔離使得射頻信號可以直接應(yīng)用到不轉(zhuǎn)換的輸入終端,而不需要來自其他組件的復(fù)雜交互或連接PCB線路。(圖38)

OPA2140的EMIRR IN+與頻率的關(guān)系如中所示。如果可用,任何雙和四個運算放大器設(shè)備版本具有幾乎相似的EMIRR IN+性能。OPA2140單位增益帶寬為11MHz。低于此頻率的EMIRR性能表示屬于運算放大器帶寬內(nèi)的干擾信號。

參見應(yīng)用報告,運算放大器的EMI抑制比(SBOA128)。

表2列出了OPA2140在實際應(yīng)用中常見的特定頻率下的EMIRR IN+值。表2中列出的應(yīng)用可以集中在所示的特定頻率上或在其附近運行。這些信息可能對從事此類應(yīng)用的設(shè)計師特別感興趣,或者在其他領(lǐng)域工作的設(shè)計師可能會特別感興趣,比如工業(yè)、科學(xué)和醫(yī)療(ISM)無線電波段。

EMIRR+測試配置

圖39顯示了測試EMIRR IN+的電路配置。射頻源通過傳輸線連接到運算放大器非轉(zhuǎn)換輸入端。運算放大器配置為單位增益緩沖拓撲,輸出連接低通濾波器(LPF)和數(shù)字萬用表(DMM)。運算放大器輸入端的大阻抗失配會導(dǎo)致電壓反射;然而,當確定EMIRR IN+時,會對這種效應(yīng)進行表征和說明。由此產(chǎn)生的直流偏移電壓由萬用表進行采樣和測量。LPF將萬用表與可能干擾萬用表精度的殘余射頻信號隔離。

設(shè)備功能模式

OPAx140具有單一功能模式,當電源電壓大于4.5 V(±2.25 V)時,它可以工作。OPAx140的最大電源電壓為36 V(±18 V)。

應(yīng)用與實施

注意:以下應(yīng)用章節(jié)中的信息不是TI組件規(guī)范的一部分,TI不保證其準確性或完整性。TI的客戶負責確定組件的適用性。客戶應(yīng)驗證和測試其設(shè)計實現(xiàn),以確認系統(tǒng)功能。

申請信息

OPA140、OPA2140和OPA4140是單位增益穩(wěn)定的運算放大器,具有非常低的噪聲、輸入偏置電流和輸入偏移電壓。噪聲或高阻抗電源的應(yīng)用要求去耦電容器靠近器件引腳。在大多數(shù)情況下,0.1-μF電容器就足夠了。設(shè)計人員可以很容易地使用軌道到軌道的輸出擺動和輸入范圍,包括V-利用JFET放大器的低噪聲特性,同時也接口到現(xiàn)代,單電源,精密數(shù)據(jù)轉(zhuǎn)換器。

典型應(yīng)用

設(shè)計要求

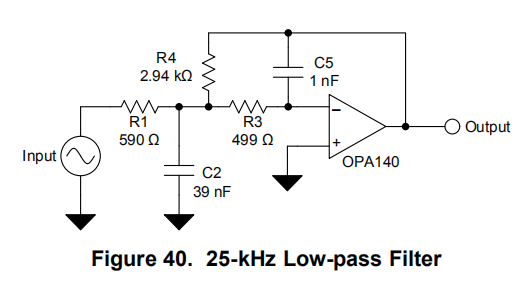

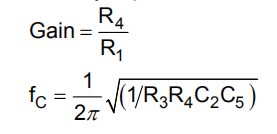

低通濾波器通常用于信號處理應(yīng)用,以減少噪聲和防止混疊。OPAx140是高精度有源濾波器的理想選擇。圖40顯示了信號處理應(yīng)用中常見的二階低通濾波器。

在本設(shè)計示例中使用以下參數(shù):

•增益=5 V/V(反轉(zhuǎn)增益)

•低通截止頻率=25 kHz

•二階切比雪夫濾波器響應(yīng),通帶內(nèi)增益峰值為3-dB

詳細設(shè)計程序

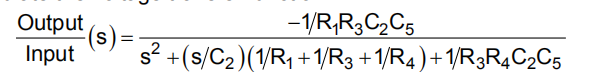

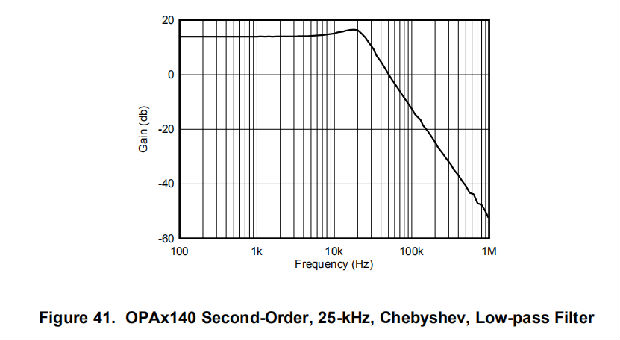

低通網(wǎng)絡(luò)函數(shù)的無限增益多重反饋電路如所示。使用方程式1計算電壓傳遞函數(shù)。

這個電路產(chǎn)生信號反轉(zhuǎn)。對于該電路,直流增益和低通截止頻率由方程式2計算:

軟件工具可以方便地簡化濾波器的設(shè)計。WEBENCH®Filter Designer是一個簡單、功能強大、易于使用的有源濾波器設(shè)計程序。WEBENCH®過濾器設(shè)計器允許您使用TI供應(yīng)商合作伙伴的TI運算放大器和無源元件來創(chuàng)建優(yōu)化的濾波器設(shè)計。

WEBENCH Filter Designer是WEBENCH設(shè)計中心提供的基于web的工具,允許您在幾分鐘內(nèi)設(shè)計、優(yōu)化和模擬完整的多級有源濾波器解決方案。

應(yīng)用曲線

電源建議

OPAx140規(guī)定在4.5 V至36 V(±2.25 V至±18 V)下工作;許多規(guī)范適用于-40°C至125°C。典型特性中給出了與工作電壓或溫度有關(guān)的顯著變化的參數(shù)。

注意安全

大于40 V的電源電壓會永久損壞設(shè)備;請參閱絕對最大額定值。

將0.1-μF旁路電容器靠近電源引腳,以減少噪聲或高阻抗電源的耦合誤差。有關(guān)旁路電容器放置的更多詳細信息,請參閱布局一節(jié)。

布局

布局指南

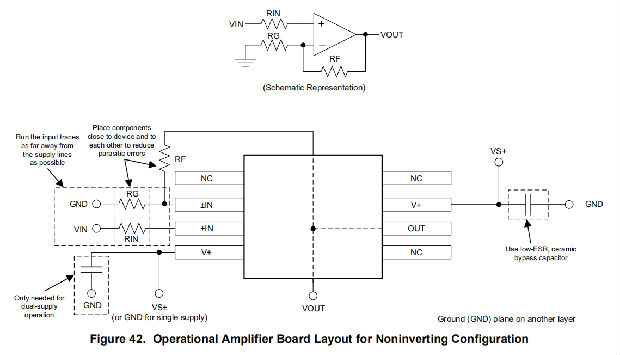

為獲得設(shè)備的最佳操作性能,請使用良好的PCB布局實踐,包括:

•噪聲可以通過整個電路的電源引腳和運放本身傳播到模擬電路中。旁路電容器用于通過提供模擬電路局部的低阻抗電源來降低耦合噪聲。

–將低ESR、0.1-μF陶瓷旁路電容器連接在每個電源引腳和接地之間,并盡可能靠近設(shè)備。從V+到地的單旁路電容器適用于單電源應(yīng)用。

•電路模擬和數(shù)字部分的單獨接地是最簡單和最有效的噪聲抑制方法之一。多層印刷電路板上的一層或多層通常用于接地層。接地板有助于分配熱量并減少電磁干擾噪音。確保在物理上分離數(shù)字和模擬接地,注意接地電流的流動。有關(guān)詳細信息,請參閱電路板布局技術(shù)(SLOA089)。

•為了減少寄生耦合,輸入軌跡應(yīng)盡可能遠離電源或輸出軌跡。如果這些記錄道不能保持分離,則垂直穿過敏感記錄道要比與噪聲記錄道平行要好得多。

•將外部組件盡可能靠近設(shè)備。如圖42所示,保持RF和RG接近逆變輸入可以最大限度地減小寄生電容。

•輸入記錄道的長度應(yīng)盡可能短。始終記住,輸入軌跡是電路中最敏感的部分。

•考慮在關(guān)鍵線路周圍設(shè)置一個驅(qū)動的低阻抗保護環(huán)。保護環(huán)可以顯著降低附近不同電位的漏電電流。

•為了獲得最佳性能,TI建議在板組裝后清潔PCB。

•任何精密集成電路都可能因水分進入塑料包裝而發(fā)生性能變化。在任何水性PCB清潔過程之后,TI建議烘烤PCB組件,以去除清潔過程中引入設(shè)備包裝的水分。在大多數(shù)情況下,在85°C的低溫清潔后烘烤30分鐘就足夠了。

布局示例

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍牙WIFI模組、進口芯片替換國產(chǎn)降成本等解決方案,可承接項目開發(fā),以及元器件一站式采購服務(wù),類型有運放芯片、電源芯片、MO芯片、藍牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1