特征

快速吞吐量:250 kSPS

規(guī)定用于2.35 V至5.25 V的VDD

低功率:

4兆瓦,250 kSPS,3伏電源

在250 kSPS時(shí)為13.5 mW,5 V電源

寬輸入帶寬:

輸入頻率為100 kHz時(shí),最小信噪比為71 dB

靈活的電源/串行時(shí)鐘速度管理

管道無延遲

高速串行接口:

SPI®/QSPI™/微絲™/DSP兼容

待機(jī)模式:最大1μA

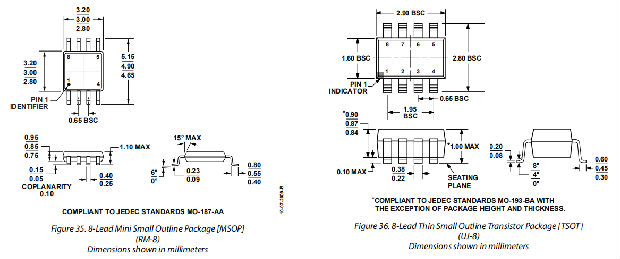

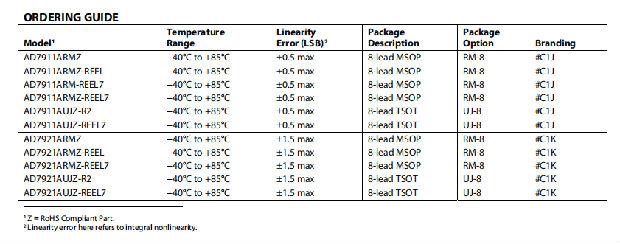

8導(dǎo)TSOT封裝

8-引線MSOP封裝

應(yīng)用

電池供電系統(tǒng):

個(gè)人數(shù)字助理

醫(yī)療器械

移動(dòng)通信

儀表和控制系統(tǒng)

數(shù)據(jù)采集系統(tǒng)

高速調(diào)制解調(diào)器

光學(xué)傳感器

一般說明

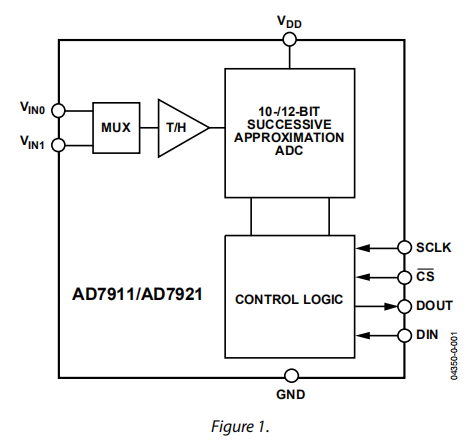

AD7911/AD79211分別是10位和12位高速、低功耗、雙通道逐次逼近adc。這些部件的工作電壓為2.35伏至5.25伏,吞吐率高達(dá)250 kSPS。這些部件包含一個(gè)低噪聲、寬帶寬的跟蹤保持放大器,可以處理超過6兆赫的輸入頻率。轉(zhuǎn)換過程和數(shù)據(jù)采集由CS和串行時(shí)鐘控制,允許設(shè)備與微處理器或DSP接口。輸入信號(hào)在CS下降沿采樣,轉(zhuǎn)換也在此時(shí)啟動(dòng)。沒有與部件相關(guān)的管道延遲。

要轉(zhuǎn)換的通道通過DIN引腳選擇,操作模式由CS控制。來自DOUT管腳的串行數(shù)據(jù)流有一個(gè)信道標(biāo)識(shí)符位,它提供有關(guān)轉(zhuǎn)換信道的信息。

AD7911/AD7921采用先進(jìn)的設(shè)計(jì)技術(shù),在高吞吐量下實(shí)現(xiàn)非常低的功耗。

部件的參考從VDD內(nèi)部獲取,因此允許ADC具有最寬的動(dòng)態(tài)輸入范圍。因此,部件的模擬輸入范圍是0到VDD。轉(zhuǎn)換率由SCLK信號(hào)決定。

產(chǎn)品亮點(diǎn)

1、TSOT封裝中的2通道,250 kSPS,10-/12位ADC。

2、低功耗。

3、靈活的電源/串行時(shí)鐘速度管理。轉(zhuǎn)換率由串行時(shí)鐘決定;當(dāng)串行時(shí)鐘速度增加時(shí),轉(zhuǎn)換時(shí)間縮短。部件還具有斷電模式,以在較低的吞吐量下最大限度地提高功率效率。當(dāng)不轉(zhuǎn)換時(shí)使用掉電模式時(shí),平均功耗降低。電流消耗最大為1μA,通常在在斷電模式下。

4、源于電源的參考。

5、無管道延遲。這些部件采用標(biāo)準(zhǔn)逐次逼近ADC,通過CSinput和once-off轉(zhuǎn)換控制精確控制采樣瞬間。

功能框圖

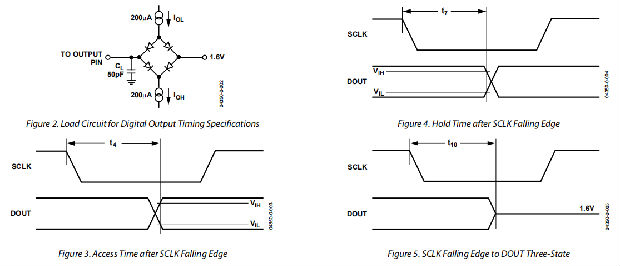

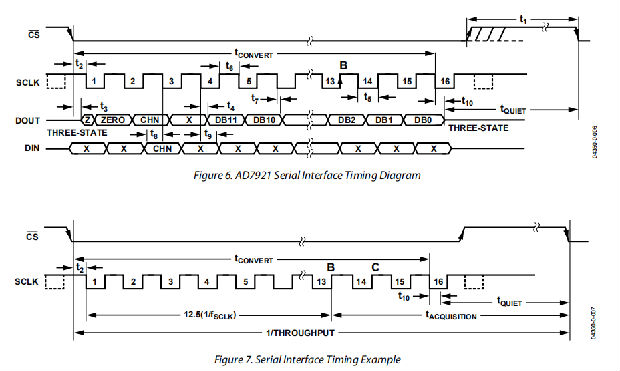

時(shí)序圖

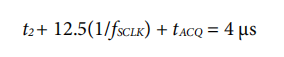

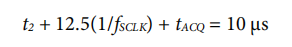

計(jì)時(shí)示例

圖6和圖7顯示了定時(shí)規(guī)范部分的一些定時(shí)參數(shù)。

定時(shí)示例1

如圖7所示,當(dāng)fSCLK=5mhz,吞吐量為50ksps-ic/" title="250ksps">250ksps時(shí),周期時(shí)間為:

t2=10ns時(shí),tACQ為1.49μs,滿足tACQ 290ns的要求。

在圖7中,tACQ由2.5(1/fSCLK)+t10+tQUIET組成,其中t10=30ns最大值。這允許tQUIET的值為960 ns,滿足30 ns的最低要求。

定時(shí)示例2

AD7921也可以在較低的時(shí)鐘頻率下工作。如圖7所示,當(dāng)fSCLK=2mhz,吞吐量為100ksps時(shí),周期時(shí)間為:

t2=10ns時(shí),tACQ為3.74μs,滿足tACQ 290ns的要求。

在圖7中,tACQ由2.5(1/fSCLK)+t10+tQUIET組成,其中t10=30ns最大值。這允許tQUIET的值為2.46μs,滿足30 ns的最低要求。

在這個(gè)例子中,與其他較慢的時(shí)鐘值一樣,信號(hào)可能已經(jīng)在轉(zhuǎn)換完成之前獲得,但是仍然需要在轉(zhuǎn)換之間留出30 ns的最小值。在這個(gè)例子中,信號(hào)應(yīng)該在圖7中的大約C點(diǎn)完全采集。

術(shù)語

積分非線性

與通過ADC傳輸函數(shù)端點(diǎn)的直線的最大偏差。對(duì)于AD7911/AD7921,傳輸函數(shù)的端點(diǎn)是零標(biāo)度,即第一個(gè)代碼轉(zhuǎn)換下的1個(gè)LSB點(diǎn),以及滿刻度,即最后一個(gè)代碼轉(zhuǎn)換上方的點(diǎn)1lsb。

微分非線性

測(cè)量值與理想1 LSB之間的差值在ADC中的任何兩個(gè)相鄰代碼之間發(fā)生變化。

偏移誤差

第一個(gè)代碼轉(zhuǎn)換(00…000)到(00…001)與理想值的偏差,即AGND+1 LSB。

偏移誤差匹配

任意兩個(gè)通道之間偏移誤差的差值。

增益誤差

最后一個(gè)代碼轉(zhuǎn)換(111…110)到(111…111)與理想值的偏差,即偏移誤差調(diào)整后的VREF−1 LSB。

增益誤差匹配

任何兩個(gè)通道之間增益誤差的差異。

總不可調(diào)整誤差

包括增益誤差、線性誤差和偏移誤差的綜合規(guī)范。

通道間隔離

信道間串?dāng)_水平的度量。通過將20 kHz至500 kHz的全標(biāo)度正弦波信號(hào)應(yīng)用于非選定輸入信道,并確定該信號(hào)在所選信道中用10 kHz信號(hào)衰減的程度來測(cè)量。該數(shù)字給出了AD7911/AD7921的兩個(gè)信道的最壞情況。

跟蹤并保持采集時(shí)間

在轉(zhuǎn)換結(jié)束后,跟蹤保持放大器的輸出達(dá)到其最終值在±1 LSB內(nèi)所需的時(shí)間。跟蹤保持放大器在轉(zhuǎn)換結(jié)束時(shí)返回到跟蹤模式。有關(guān)更多詳細(xì)信息,請(qǐng)參閱串行接口部分。

信噪比和失真比(SINAD)

在A/D轉(zhuǎn)換器輸出端測(cè)得的信噪比和失真率。信號(hào)是正弦波的均方根值,噪聲是所有非基本信號(hào)的均方根值之和,采樣頻率的一半(fs/2),包括諧波,但不包括直流電。

信噪比

在A/D轉(zhuǎn)換器輸出端測(cè)得的信噪比。信號(hào)是正弦波輸入的rms值。噪聲是Nyquist帶寬(fs/2)內(nèi)的均方根量化誤差。正弦波的rms值是其峰峰值除以√2的一半,量化噪聲的rms值為q/√12。該比率取決于數(shù)字化過程中量化層級(jí)的數(shù)量;層級(jí)越多,量化噪音越小。對(duì)于理想的N位轉(zhuǎn)換器,SNR定義為

SNR=6.02 N+ 1.76 dB

因此,對(duì)于12位轉(zhuǎn)換器,信噪比為74 dB;對(duì)于10位轉(zhuǎn)換器,信噪比為62 dB。

然而,ADC中的各種誤差源導(dǎo)致測(cè)量的信噪比小于理論值。這些誤差是由積分和微分非線性、內(nèi)部交流噪聲源等引起的。

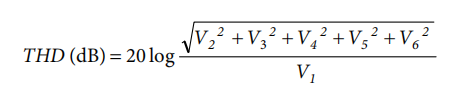

總諧波失真(THD)

諧波的均方根和與基波的比值,定義為:

式中:

V1是基波的均方根振幅。

V2、V3、V4、V5和V6是第二次至第六次諧波的均方根振幅。

峰值諧波或雜散噪聲

ADC輸出頻譜中第二大分量的均方根值(高達(dá)fs/2,不包括直流電)與基波的均方根值之比。通常情況下,該規(guī)范的值由頻譜中最大的諧波決定,但對(duì)于諧波埋在噪聲層中的ADC來說,這是一個(gè)噪聲峰值。

互調(diào)失真

當(dāng)輸入由兩個(gè)頻率(fa和fb)的正弦波組成時(shí),任何具有非線性的有源器件都會(huì)在mfa±nfb的和頻和差頻下產(chǎn)生失真產(chǎn)物,其中m,n=0,1,2,3,依此類推。互調(diào)失真項(xiàng)是指m和n都不等于零的項(xiàng)。例如,二階項(xiàng)包括(fa+fb)和(fa−fb),而三階項(xiàng)包括(2fa+fb)、(2fa−fb)、(fa+2fb)和(fa−2fb)。

AD7911/AD7921使用CCIF標(biāo)準(zhǔn)進(jìn)行測(cè)試,其中使用兩個(gè)輸入頻率(請(qǐng)參閱“規(guī)格”部分中的fa和fb)。在這種情況下,二階項(xiàng)的頻率通常與原始正弦波相距甚遠(yuǎn),而三階項(xiàng)的頻率通常接近輸入頻率。因此,二階項(xiàng)和三階項(xiàng)是分開規(guī)定的。互調(diào)失真的計(jì)算如THD規(guī)范中所述,其定義為單個(gè)失真產(chǎn)物的rms和與以分貝表示的基本原理。

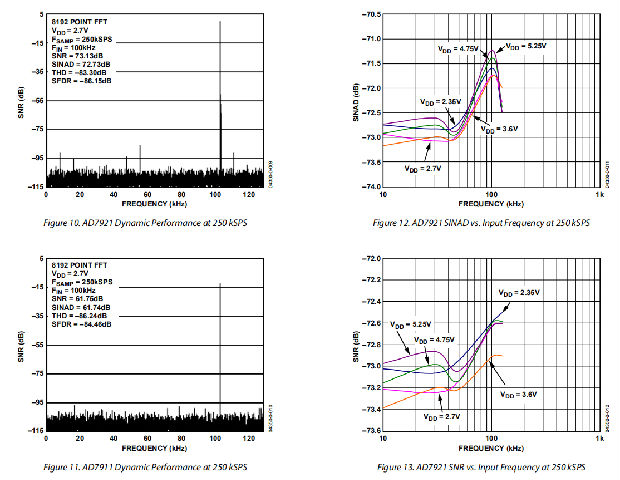

典型性能特征

圖10和圖11分別顯示了AD7921和AD7911在250 kSPS采樣率和100 kHz輸入頻率下的典型FFT圖。

圖12顯示了AD7921以50ksps-ic/" title="250ksps">250ksps采樣,SCLK頻率為5MHz時(shí),不同電源電壓下的SINAD比率性能與輸入頻率的關(guān)系。

圖13顯示了在不同電源電壓下采樣時(shí)的信噪比性能與輸入頻率250 kSPS,SCLK頻率為5 MHz,適用于AD7921。

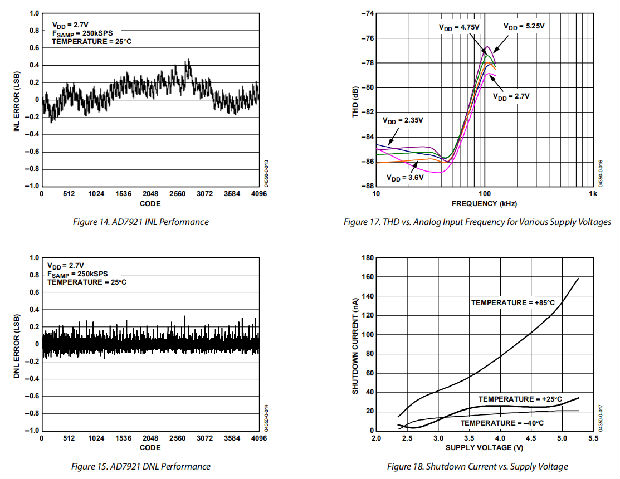

圖14和圖15顯示了AD7921的INL和DNL性能。

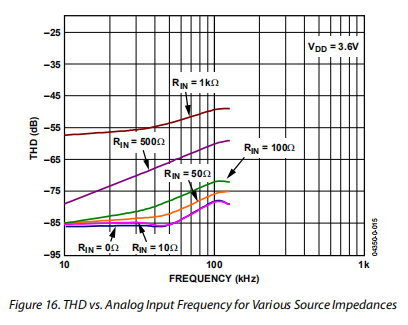

圖16顯示了當(dāng)使用3.6V的電源電壓和50ksps-ic/" title="250ksps">250ksps的采樣率時(shí),不同源阻抗下的總諧波失真與模擬輸入頻率的關(guān)系圖。參見模擬輸入部分。

圖17顯示了在250 kSPS和5 MHz SCLK頻率下采樣時(shí),各種電源電壓下總諧波失真與模擬輸入頻率的關(guān)系圖。

圖18顯示了不同工作溫度下的關(guān)機(jī)電流與電源電壓的關(guān)系。

電路信息

AD7911/AD7921分別是快速、2通道、10-/12位、單電源、模數(shù)轉(zhuǎn)換器(ADC)。這些部件可以在2.35伏到5.25伏的電源下工作。當(dāng)使用5伏或3伏電源供電時(shí),AD7911/AD7921在配備5兆赫時(shí)鐘時(shí),其吞吐率可達(dá)到250 kSPS。

AD7911/AD7921為用戶提供了片上跟蹤和保持、ADC和串行接口,所有這些都封裝在一個(gè)小型的8線TSOT封裝或8線MSOP封裝中,這為用戶提供了比其他解決方案更節(jié)省空間的優(yōu)勢(shì)。串行時(shí)鐘輸入從部件訪問數(shù)據(jù),控制寫入ADC的數(shù)據(jù)傳輸,并為逐次逼近ADC提供時(shí)鐘源。模擬輸入范圍是0到VDD。ADC不需要外部參考,芯片上也不需要參考。AD7911/AD7921的基準(zhǔn)源于電源,因此可提供最寬的動(dòng)態(tài)輸入范圍。

AD7911/AD7921具有斷電選項(xiàng),允許在轉(zhuǎn)換之間節(jié)省電源。斷電功能通過標(biāo)準(zhǔn)串行接口實(shí)現(xiàn),如操作模式部分所述。

變頻器操作

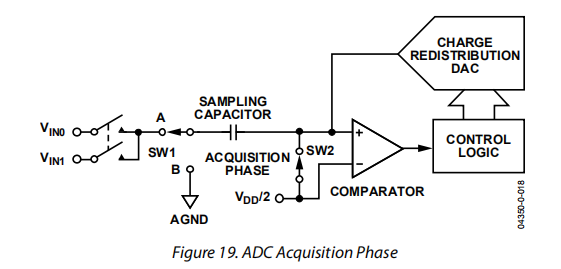

AD7911/AD7921是10-/12位逐次逼近基于電荷再分配DAC的adc。圖19和圖20顯示了ADC的簡化示意圖。圖19顯示了采集階段的ADC。SW2閉合,SW1處于位置A,比較器保持在平衡狀態(tài),采樣電容器獲取所選VIN通道上的信號(hào)。

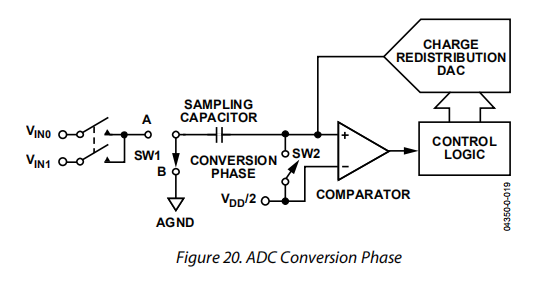

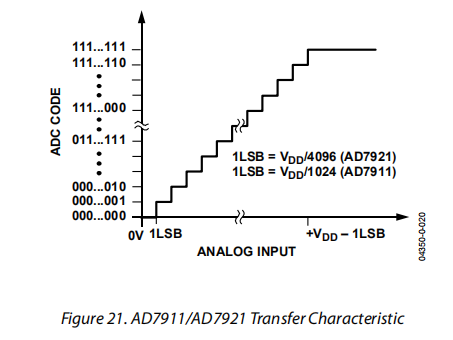

當(dāng)ADC開始轉(zhuǎn)換時(shí)(見圖20),SW2打開,SW1移動(dòng)到位置B,導(dǎo)致比較器變得不平衡。控制邏輯和電荷再分配DAC用于從采樣電容器中增減固定量的電荷,以使比較器回到平衡狀態(tài)。當(dāng)比較器重新平衡時(shí),轉(zhuǎn)換完成。控制邏輯產(chǎn)生ADC輸出代碼。圖21顯示了ADC傳輸函數(shù)。

ADC傳遞函數(shù)

AD7911/AD7921的輸出編碼是直接二進(jìn)制的。設(shè)計(jì)的代碼轉(zhuǎn)換發(fā)生在連續(xù)的整數(shù)LSB值處,即1 LSB、2 LSB,依此類推。對(duì)于AD7921,LSB大小為VDD/4096,對(duì)于AD7911,LSB大小為VDD/1024。AD7911/AD7921的理想傳輸特性如圖21所示。

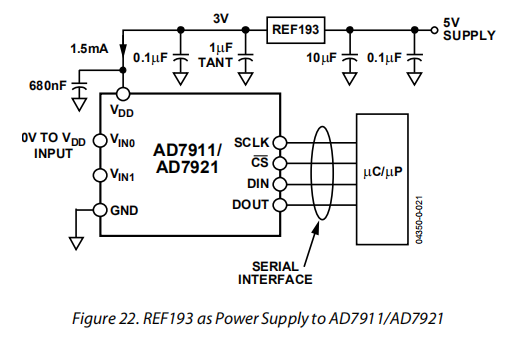

典型接線圖

圖22顯示了AD7911/AD7921的典型連接圖。VREF是從VDD內(nèi)部獲取的,因此VDD應(yīng)該很好地解耦。這提供了0 V到VDD的模擬輸入范圍。轉(zhuǎn)換結(jié)果以16位字輸出,其中有兩個(gè)前導(dǎo)零,后跟識(shí)別轉(zhuǎn)換通道的通道標(biāo)識(shí)符位,后跟與轉(zhuǎn)換通道匹配的無效位,然后是12位或10位結(jié)果的MSB。對(duì)于AD7911,10位結(jié)果后面跟兩個(gè)0。請(qǐng)參閱串行接口部分。

另外,由于AD7911/AD7921所需的電源電流非常低,因此可以使用精密基準(zhǔn)作為AD7911/AD7921的電源。REF19x基準(zhǔn)電壓(REF195用于5V或REF193用于3V)可用于向ADC提供所需電壓(見圖22)。如果電源非常嘈雜或系統(tǒng)電源電壓不是5 V或3 V(例如15 V)的某個(gè)值,則此配置特別有用。REF19x向AD7911/AD7921輸出穩(wěn)定電壓。如果使用低壓差REF193,則需要向AD7911/AD7921供電的電流通常為1.5 mA。當(dāng)ADC以250 kSPS的速率轉(zhuǎn)換時(shí),REF193需要向AD7911/AD7921提供最大2 mA的電流。REF193的負(fù)載調(diào)節(jié)通常為10 ppm/mA(REF193,Vs=5 V),由此產(chǎn)生的2 mA誤差為20 ppm(60μV)。對(duì)于該誤差,LSA為0821.0,對(duì)應(yīng)于AD792 VDD=3 V來自REF193,AD7911的LSB誤差為0.061。

對(duì)于需要考慮功耗的應(yīng)用,應(yīng)使用ADC的斷電模式和REF19x基準(zhǔn)的休眠模式來提高電源性能。

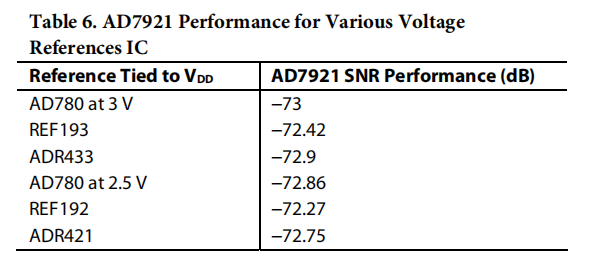

表6提供了一些典型的性能數(shù)據(jù),在相同的設(shè)置條件下,各種參考值用作VDD源和50 kHz輸入音調(diào)。

模擬量輸入

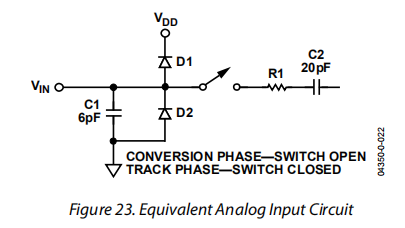

圖23顯示了AD7911/AD7921模擬輸入結(jié)構(gòu)的等效電路。兩個(gè)二極管D1和D2為模擬輸入提供ESD保護(hù)。必須注意確保模擬輸入信號(hào)不會(huì)超過電源軌300毫伏,因?yàn)檫@會(huì)導(dǎo)致這些二極管正向偏壓并開始向基板傳導(dǎo)電流。這些二極管在不會(huì)對(duì)零件造成不可逆損壞的情況下可以傳導(dǎo)的最大電流為10毫安。

圖23中的電容器C1通常約為6 pF,主要?dú)w因于管腳電容。電阻器R1是由跟蹤保持開關(guān)的導(dǎo)通電阻構(gòu)成的集中元件,還包括輸入多路復(fù)用器的導(dǎo)通電阻。該電阻通常約為100Ω。電容器C2是ADC采樣電容器,通常具有20pf的電容。

對(duì)于交流應(yīng)用,建議使用相關(guān)模擬輸入引腳上的帶通濾波器從模擬輸入信號(hào)中移除高頻分量。在諧波失真和信噪比非常重要的應(yīng)用中,模擬輸入應(yīng)該由低阻抗源驅(qū)動(dòng)。大的源阻抗會(huì)顯著影響ADC的交流性能。這可能需要使用輸入緩沖放大器。運(yùn)算放大器的選擇是特定應(yīng)用的函數(shù)。

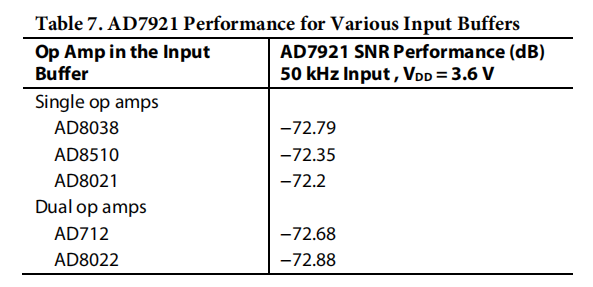

表7提供了一些典型的性能數(shù)據(jù),在相同的設(shè)置條件下,各種運(yùn)放用作輸入緩沖器,輸入音調(diào)為50khz。

當(dāng)沒有放大器用于驅(qū)動(dòng)模擬輸入時(shí),源阻抗應(yīng)限制在低值。最大源阻抗取決于可容忍的總諧波失真(THD)量。THD隨著源阻抗的增加和性能的降低而增加(見圖16)。

數(shù)字輸入

應(yīng)用于AD7911/AD7921的數(shù)字輸入不受限制模擬輸入的最大額定值的限制。相反,應(yīng)用的數(shù)字輸入可以達(dá)到7V,并且不像模擬輸入那樣受到VDD+0.3V限制的限制。例如,如果AD7911/AD7921在3 V的VDD下工作,則5 V邏輯電平可用于數(shù)字輸入。然而,值得注意的是,當(dāng)VDD=3V時(shí),DOUT上的數(shù)據(jù)輸出仍然具有3V邏輯電平。SCLK、DIN和CS的另一個(gè)優(yōu)點(diǎn)不受VDD+0.3V限制的限制,這是避免了電源排序問題。如果在VDD之前應(yīng)用了CS、DIN或SCLK,則不會(huì)像在VDD之前應(yīng)用大于0.3V的信號(hào)一樣存在閂鎖風(fēng)險(xiǎn)。

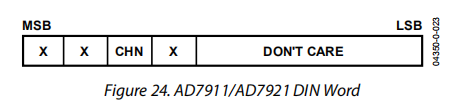

DIN輸入

下一次轉(zhuǎn)換中要轉(zhuǎn)換的通道是通過寫入DIN引腳來選擇的。DIN引腳上的數(shù)據(jù)被加載到SCLK下降沿的AD7911/AD7921中。在從零件讀取轉(zhuǎn)換結(jié)果的同時(shí),數(shù)據(jù)被傳輸?shù)紻IN引腳上的零件中。

只使用DIN字的第三位;其余的被ADC忽略。第三個(gè)MSB是信道標(biāo)識(shí)符位,它標(biāo)識(shí)下一次轉(zhuǎn)換中要轉(zhuǎn)換的信道,VIN0(CHN=0)或VIN1(CHN=1)。

輸出輸出

來自AD7911/AD7921的轉(zhuǎn)換結(jié)果作為串行數(shù)據(jù)流提供在該輸出上。在進(jìn)行轉(zhuǎn)換的同時(shí),這些位在SCLK下降沿上時(shí)鐘輸出。

AD7921的串行數(shù)據(jù)流由兩個(gè)前導(dǎo)零組成,后跟標(biāo)識(shí)所轉(zhuǎn)換信道的位,與信道標(biāo)識(shí)位匹配的無效位,以及先提供MSB的12位轉(zhuǎn)換結(jié)果。

對(duì)于AD7911,串行數(shù)據(jù)流由兩個(gè)前導(dǎo)零組成,后跟標(biāo)識(shí)所轉(zhuǎn)換信道的位,與信道標(biāo)識(shí)位匹配的無效位,以及先提供MSB的10位轉(zhuǎn)換結(jié)果,然后是兩個(gè)尾隨的零。

操作模式

AD7911/AD7921的兩種工作模式是正常模式和斷電模式。通過控制CS信號(hào)的邏輯狀態(tài)來選擇操作模式。轉(zhuǎn)換初始化后CS被拉高的點(diǎn)決定了AD7911/AD7921是否進(jìn)入斷電模式。類似地,如果已經(jīng)處于斷電模式,CS可以控制設(shè)備是恢復(fù)正常操作還是保持?jǐn)嚯娔J健?/p>

斷電模式旨在提供靈活的電源管理選項(xiàng),并針對(duì)不同的應(yīng)用需求優(yōu)化功耗與吞吐量比率。

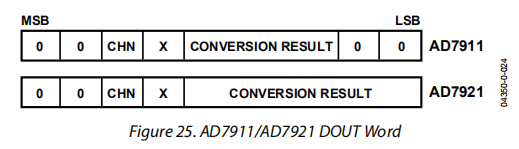

正常模式

正常模式旨在獲得最快的吞吐量性能。用戶不必?fù)?dān)心任何通電時(shí)間,因?yàn)锳D7911/AD7921始終保持完全通電。圖26顯示了AD7911/AD7921在此模式下的操作。

轉(zhuǎn)換在CS的下降沿開始,如本節(jié)所述。為確保部件始終保持完全通電,串行接口ECS必須保持在較低水平,直到CS下降沿后經(jīng)過至少10個(gè)SCLK下降沿。如果CS在第10個(gè)SCLK下降沿之后但在T轉(zhuǎn)換結(jié)束之前的任何時(shí)候變高,則部件保持通電狀態(tài),但轉(zhuǎn)換終止,DOUT返回三個(gè)狀態(tài)。對(duì)于AD7911/AD7921,至少需要14和16個(gè)串行時(shí)鐘周期來完成轉(zhuǎn)換并訪問完整的轉(zhuǎn)換結(jié)果。

CS可以高怠速直到下一次轉(zhuǎn)換,或者可以低怠速直到CS在下一次轉(zhuǎn)換之前返回高電平(實(shí)際上是怠速CS low)。一旦數(shù)據(jù)傳輸完成(DOUT返回到三個(gè)狀態(tài)),就可以通過再次引入CSlow在安靜時(shí)間tQUIET之后啟動(dòng)另一個(gè)轉(zhuǎn)換。

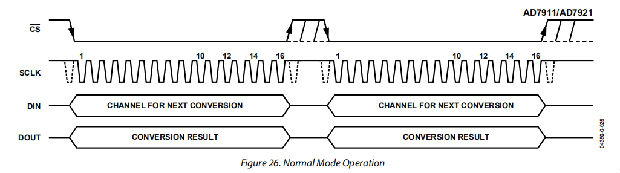

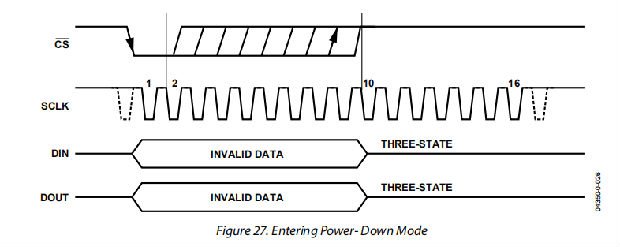

斷電模式

斷電模式適用于需要較慢吞吐量的應(yīng)用程序。在ADC的每一個(gè)轉(zhuǎn)換過程中,或者在一個(gè)比較長的時(shí)間內(nèi)關(guān)閉ADC的吞吐量,或者在ADC之間以較高的速率進(jìn)行轉(zhuǎn)換在幾次轉(zhuǎn)換的爆發(fā)之間。當(dāng)AD7911/AD7921處于斷電模式時(shí),所有模擬電路斷電。

要進(jìn)入斷電模式,轉(zhuǎn)換過程必須通過在SCLK的第二個(gè)下降沿之后和SCLK的第10個(gè)下降沿之前的任何時(shí)間將CS調(diào)高來中斷,如圖27所示。一旦在SCLKs窗口中CS被調(diào)高,則部件進(jìn)入斷電模式,CS下降沿啟動(dòng)的轉(zhuǎn)換終止,DOUT返回到三個(gè)狀態(tài)。如果CS在第二個(gè)SCLK下降沿之前變高,則部件將保持在正常模式并且不會(huì)斷電。這有助于避免因CS線路故障而意外斷電。

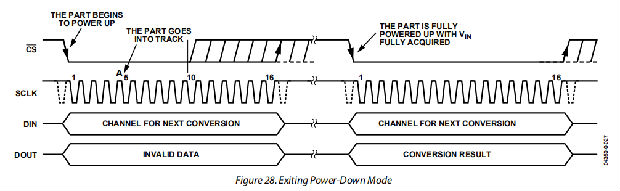

要退出此操作模式并再次接通AD7911/AD7921的電源,將執(zhí)行虛擬轉(zhuǎn)換。在CS的下降沿,設(shè)備開始通電,只要CS保持在較低水平,直到第10個(gè)SCLK下降沿之后,設(shè)備就會(huì)繼續(xù)通電。一旦經(jīng)過16個(gè)SCLK并且下一次轉(zhuǎn)換得到有效數(shù)據(jù),設(shè)備就完全通電,如圖28所示。如果在SCLK的第10個(gè)下降沿之前CS處于高位,則AD7911/AD7921將返回?cái)嚯娔J健_@有助于避免由于CS線路上的故障或CS較低時(shí)8個(gè)SCLK周期的意外突發(fā)而意外通電。因此,盡管設(shè)備可能在CS的下降沿開始通電,但它在CS的上升沿再次斷電,只要這發(fā)生在第10個(gè)SCLK下降沿之前。

通電時(shí)間

AD7911/AD7921的通電時(shí)間為1μs,這意味著在SCLK頻率高達(dá)5mhz的情況下,一個(gè)虛擬周期始終足以使設(shè)備通電。一旦虛擬循環(huán)完成,ADC將完全通電,并正確獲取輸入信號(hào)。靜態(tài)時(shí)間tQUIET必須仍然允許從虛擬轉(zhuǎn)換到CS的下一個(gè)下降沿后總線返回到三個(gè)狀態(tài)的點(diǎn)。當(dāng)以250 kSPS的吞吐率運(yùn)行時(shí),AD7911/AD7921通電并在一個(gè)虛擬周期內(nèi)獲取±1 LSB內(nèi)的信號(hào)。

如圖28所示,當(dāng)以虛擬循環(huán)從斷電模式通電時(shí),在部件斷電時(shí)處于保持模式的跟蹤和保持返回到CS下降沿后部件接收到的第五個(gè)SCLK下降沿上的跟蹤模式。在中顯示為點(diǎn)A。此時(shí),部件開始在當(dāng)前偽轉(zhuǎn)換中選擇的信道上獲取信號(hào)。

盡管在任何SCLK頻率下,一個(gè)虛擬周期足以為設(shè)備通電并獲取VIN,但并不一定意味著必須始終經(jīng)過16個(gè)SCLK的完整虛擬周期才能通電并完全獲取VIN。1μs足以使設(shè)備通電并獲取輸入信號(hào)。例如,如果將5 MHz SCLK頻率應(yīng)用于ADC,則周期時(shí)間為3.2μs。在一個(gè)虛擬循環(huán)(3.2μs)中,部件將通電并完全獲取VIN。然而,在使用5mhz SCLK的1μs后,僅經(jīng)過5個(gè)SCLK周期。在這個(gè)階段,ADC將完全通電。在這種情況下,CSC可以在第10個(gè)SCLK下降沿后升高,并在一段時(shí)間后再次降低,tQUIET,以啟動(dòng)轉(zhuǎn)換。

當(dāng)電源首次應(yīng)用于AD7911/AD7921時(shí),ADC可在斷電模式或正常模式下通電。因此,最好允許虛擬循環(huán)過去,以確保零件在嘗試有效轉(zhuǎn)換之前完全通電。同樣,如果用戶希望在不使用時(shí)保持部件斷電模式,并在斷電模式下通電,則可以使用虛擬循環(huán),通過執(zhí)行如圖27所示的循環(huán)來確保設(shè)備處于斷電模式。

一旦向AD7911/AD7921供電,通電時(shí)間與從斷電模式通電時(shí)相同。在正常模式下,部件完全通電大約需要1μs。在執(zhí)行虛擬循環(huán)之前,無需等待1μs,以確保所需的操作模式。相反,在向ADC供電后,可以直接發(fā)生假周期。如果在虛擬轉(zhuǎn)換之后直接執(zhí)行第一次有效轉(zhuǎn)換,則必須注意確保允許足夠的采集時(shí)間。當(dāng)ADC在電源接通后首次通電時(shí),跟蹤和保持處于保持狀態(tài)。它返回到CS下降沿后部件接收到的第五個(gè)SCLK下降沿上的軌跡。

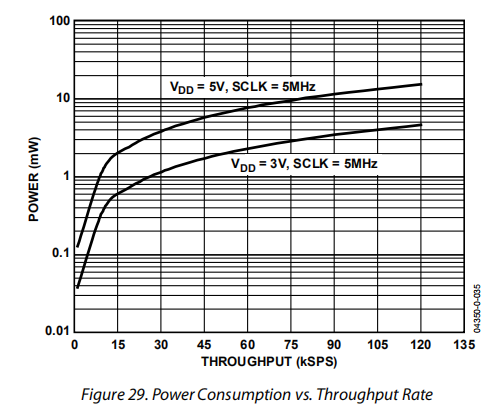

功率與吞吐量

通過在不轉(zhuǎn)換時(shí)使用AD7911/AD7921上的斷電模式,ADC的平均功耗在較低的吞吐量下降低。圖29顯示了當(dāng)吞吐量降低時(shí),設(shè)備如何在斷電狀態(tài)下保持更長時(shí)間,并且隨著時(shí)間的推移,平均功耗也相應(yīng)降低。

例如,如果AD7911/AD7921以50ksps的吞吐量和5mhz的SCLK(VDD=5v)的連續(xù)采樣模式工作,并且在轉(zhuǎn)換之間將設(shè)備置于斷電模式,則功耗計(jì)算如下。正常運(yùn)行時(shí)的功耗為20 mW(VDD=5 V)。如果一個(gè)虛擬循環(huán)在轉(zhuǎn)換(3.2μs)之間給部件通電,而剩余的轉(zhuǎn)換時(shí)間是另一個(gè)循環(huán)(3.2μs),則AD7911/AD7921在每個(gè)轉(zhuǎn)換周期中消耗20 mW,持續(xù)6.4μs。如果吞吐量為50 kSPS且周期時(shí)間為20μs,則每個(gè)周期消耗的平均功率為:

如果VDD=3v,SCLK=5mhz,并且設(shè)備在轉(zhuǎn)換之間再次處于功率下降模式,則正常運(yùn)行期間的功耗為6mw。在每個(gè)轉(zhuǎn)換周期中,AD7911/AD7921現(xiàn)在耗散6 mW,持續(xù)6.4μs。當(dāng)吞吐量為50ksps時(shí),每個(gè)周期消耗的平均功率為:

在前面的示例中,沒有考慮部件處于斷電模式時(shí)的功耗,因?yàn)殛P(guān)機(jī)電流非常低,因此不會(huì)對(duì)整體功耗值產(chǎn)生任何影響。圖29顯示了在使用5V和3V電源的轉(zhuǎn)換之間使用斷電模式時(shí)的功耗與吞吐量的關(guān)系。

斷電模式適用于吞吐量約為120 kSPS及以下的情況,因?yàn)檩^高的采樣率在斷電模式下不會(huì)節(jié)省電力。

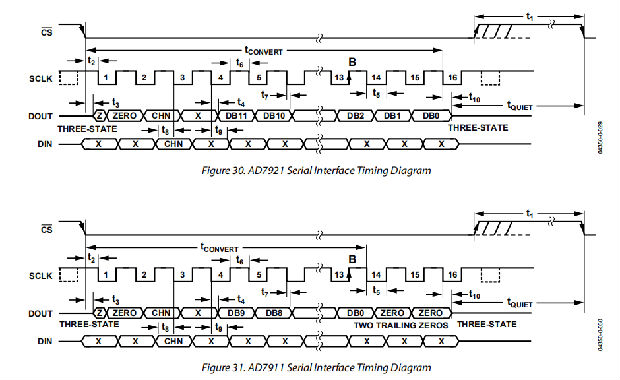

串行接口

圖30和圖31分別顯示了AD7921和AD7911串行接口的詳細(xì)時(shí)序圖。串行時(shí)鐘提供轉(zhuǎn)換時(shí)鐘,并在轉(zhuǎn)換期間控制來自AD7911/AD7921的信息傳輸。

CS信號(hào)啟動(dòng)數(shù)據(jù)傳輸和轉(zhuǎn)換過程。

CS的下降沿將跟蹤和保持置于保持模式,使總線退出三種狀態(tài),此時(shí)對(duì)模擬輸入進(jìn)行采樣,并啟動(dòng)轉(zhuǎn)換。

對(duì)于AD7921,轉(zhuǎn)換需要16個(gè)SCLK周期才能完成。一旦經(jīng)過13個(gè)SCLK下降沿,trackand hold將回到下一個(gè)SCLK上升沿上的軌跡,如圖30中B點(diǎn)所示。在第16個(gè)SCLK下降沿上,DOUT線將回到三個(gè)狀態(tài)。如果上升的邊緣CS發(fā)生在16個(gè)SCLK之前,然后轉(zhuǎn)換終止,DOUT行返回到三個(gè)狀態(tài)。否則,DOUT在第16個(gè)SCLK下降沿返回到3個(gè)狀態(tài),如圖30所示。執(zhí)行轉(zhuǎn)換過程和從AD7921訪問數(shù)據(jù)需要16個(gè)串行時(shí)鐘周期。

對(duì)于AD7911,轉(zhuǎn)換需要14個(gè)SCLK周期才能完成。一旦經(jīng)過13個(gè)SCLK下降沿,trackand hold將回到下一個(gè)SCLK上升沿上的軌跡,如圖31中B點(diǎn)所示。

如果CS上升沿出現(xiàn)在14個(gè)SCLK之前,則轉(zhuǎn)換終止,DOUT線返回到三個(gè)狀態(tài)。如果在循環(huán)中考慮16個(gè)SCLK,則DOUT在第16個(gè)SCLK下降沿返回到3個(gè)狀態(tài),如圖31所示。

CS進(jìn)入低時(shí)鐘,第一個(gè)前導(dǎo)零被讀入微控制器或DSP。然后,從第二個(gè)前導(dǎo)零開始的后續(xù)SCLK下降沿對(duì)剩余數(shù)據(jù)進(jìn)行時(shí)鐘輸出。因此,串行時(shí)鐘上的第一下降時(shí)鐘邊緣具有提供的第一前導(dǎo)零并且還時(shí)鐘輸出第二前導(dǎo)零。數(shù)據(jù)傳輸中的最后一位在第16個(gè)下降沿有效,在前一個(gè)下降沿上一個(gè)(第15個(gè))下降沿被打卡。

在使用較慢的SCLK的應(yīng)用程序中,可以讀入數(shù)據(jù)在每個(gè)SCLK上升沿。在這種情況下,SCLK的第一下降沿時(shí)鐘輸出第二超前零點(diǎn),并且可以在第一上升沿讀取。但是,第一個(gè)前導(dǎo)零是除非在第一個(gè)下降沿沒有讀取,否則當(dāng)CS變低時(shí)會(huì)丟失時(shí)鐘。SCLK的第15個(gè)下降沿時(shí)鐘出最后一個(gè)位,可以在第15個(gè)上升SCLK邊緣讀取。

如果CS在SCLK下降沿剛過之后變低,則CS像以前一樣時(shí)鐘輸出第一個(gè)前導(dǎo)零,并且可以在SCLK上升沿中讀取。下一個(gè)SCLK下降沿時(shí)鐘輸出第二個(gè)前導(dǎo)零,它可以在下一個(gè)上升沿讀取。

微處理器接口

AD7911/AD7921上的串行接口允許部件直接連接到一系列微處理器上。本節(jié)介紹如何將AD7911/AD7921與一些更常見的微控制器和DSP串行接口協(xié)議連接起來。

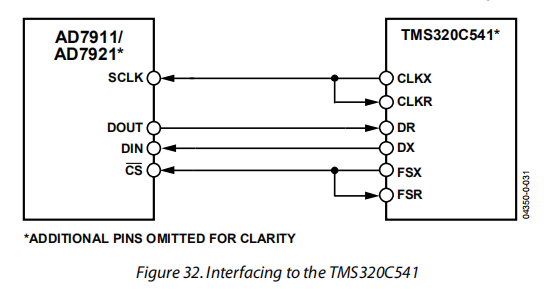

AD7911/AD7921至TMS320C541接口

TMS320C541上的串行接口使用連續(xù)的串行時(shí)鐘和幀同步信號(hào)來與AD7911/AD7921等外圍設(shè)備同步數(shù)據(jù)傳輸操作。CS輸入允許TMS320C541和AD7911/AD7921之間的簡單接口,無需任何粘合邏輯。TMS320C541的串行端口設(shè)置為在突發(fā)模式下工作(串行端口控制寄存器SPC中的FSM=1),內(nèi)部串行時(shí)鐘CLKX(SPC寄存器中的MCM=1)和內(nèi)部幀信號(hào)(SPC寄存器中的TXM=1);因此,這兩個(gè)引腳都配置為輸出。對(duì)于AD7921,字長度應(yīng)設(shè)置為16位(SPC寄存器中FO=0)。此DSP只允許字長度為16位或8位的幀。因此,在AD7911中,當(dāng)需要14位時(shí),F(xiàn)O位應(yīng)該設(shè)置為16位,并且需要16個(gè)sclk。對(duì)于AD7911,在最后兩個(gè)時(shí)鐘周期內(nèi),兩個(gè)尾隨零被時(shí)鐘輸出。

SPC寄存器中的值如下:

FO = 0

FSM = 1

MCM = 1

TXM = 1

為了在AD7911/AD7921上實(shí)現(xiàn)斷電模式,可以將格式位FO設(shè)置為1,從而將字長度設(shè)置為8位。

連接圖如圖32所示。注意,對(duì)于信號(hào)處理應(yīng)用,來自TMS320C541的幀同步信號(hào)必須提供等距采樣。

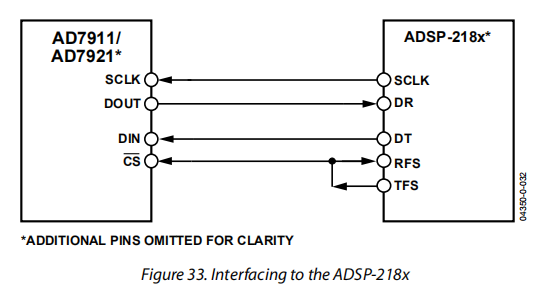

AD7911/AD7921至ADSP-218x

ADSP-218x系列DSP直接與AD7911/AD7921接口,無需任何粘合邏輯。運(yùn)動(dòng)控制寄存器的設(shè)置如下:

TFSW=RFSW=1,交替幀

INVRFS=INVTFS=1,激活低幀信號(hào)

DTYPE=00,右對(duì)齊數(shù)據(jù)

ISCLK=1,內(nèi)部串行時(shí)鐘

TFSR=RFSR=1,為每個(gè)單詞加上幀

IRFS=0,設(shè)置RFS作為輸入

ITFS=1,將TFS設(shè)置為輸出

SLEN=1111,16位用于AD7921

SLEN=1101,AD7911為14位

要實(shí)現(xiàn)斷電模式,SLEN應(yīng)設(shè)置為0111,以發(fā)出8位SCLK突發(fā)。連接圖如圖33所示。ADSP-218x將運(yùn)動(dòng)的TFS和RFS捆綁在一起,TFS被設(shè)置為輸出,RFS被設(shè)置為輸入。DSP在交替成幀模式下工作,運(yùn)動(dòng)控制寄存器如前所述設(shè)置。這個(gè)在TFS上生成的幀同步信號(hào)與CS相關(guān)聯(lián),并且與所有信號(hào)處理應(yīng)用一樣,需要等距采樣。然而,在本例中,定時(shí)器中斷用于控制ADC的采樣率,在某些情況下,可能無法實(shí)現(xiàn)等距采樣。

定時(shí)器寄存器加載一個(gè)值,該值在要求的采樣間隔內(nèi)提供中斷。當(dāng)接收到中斷時(shí),用TFS/DT(ADC控制字)傳輸一個(gè)值。TFS用于控制RFS,從而控制數(shù)據(jù)的讀取。串行時(shí)鐘的頻率設(shè)置在SCLKDIV寄存器中。當(dāng)使用TFS發(fā)送指令時(shí),即TX0=AX0,檢查SCLK的狀態(tài)。DSP等待,直到SCLK變高、變低、再變高,然后傳輸開始。如果定時(shí)器和SCLK值的選擇使得要傳輸?shù)闹噶畎l(fā)生在SCLK的上升沿上或附近,則可以傳輸數(shù)據(jù),或者等待下一個(gè)時(shí)鐘邊緣。

例如,ADSP-2189的主時(shí)鐘頻率為40mhz。如果SCLKDIV寄存器加載值為3,則獲得5 MHz的SCLK,并且每一個(gè)SCLK周期經(jīng)過8個(gè)主時(shí)鐘周期。根據(jù)所選的吞吐量,如果定時(shí)器寄存器加載值803(803+1=804),則在中斷之間以及隨后在發(fā)送指令之間發(fā)生100.5sclk。由于傳輸指令發(fā)生在SCLK邊緣,因此這種情況導(dǎo)致非平衡采樣。如果中斷之間的sclk數(shù)是N的整數(shù),則由DSP實(shí)現(xiàn)等距采樣。

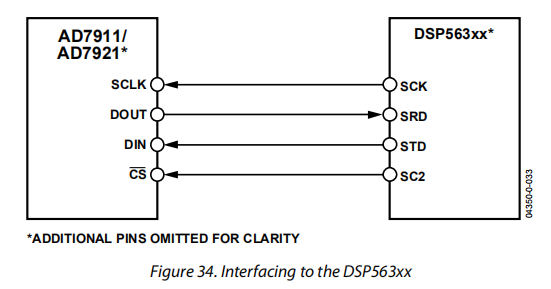

AD7911/AD7921至DSP563xx接口

圖34中的連接圖顯示了如何將AD7911/AD7921連接到摩托羅拉DSP563xx系列DSP的SSI(同步串行接口)。SSI在同步和正常模式下運(yùn)行(控制寄存器B,CRB中的SYN=1和MOD=0),Tx和Rx的內(nèi)部生成字幀同步(CRB中的位FSL1=0和FSL0=0)。通過設(shè)置AD7921的位WL2=0、WL1=1和WL0=0,將控制寄存器A(CRA)中的字長度設(shè)置為16。此DSP不提供14位字長選項(xiàng),因此AD7911字長設(shè)定為16位元,就像AD7921一樣。對(duì)于AD7911,轉(zhuǎn)換過程使用16個(gè)SCLK周期,最后兩個(gè)時(shí)鐘周期用兩個(gè)尾隨的0來填充16位字。

為了在AD7911/AD7921上實(shí)現(xiàn)斷電模式,可通過在CRA中設(shè)置位WL2=0、WL1=0和WL0=0將字長度更改為8位。FSP位在CRB寄存器可以設(shè)置為1,這意味著幀變低,轉(zhuǎn)換開始。同樣,通過CRB寄存器中的位SCD2、SCKD和SHFD,串行端口中的Pin SC2(幀同步信號(hào))和SCK被配置為輸出,并且MSB首先被移位。

數(shù)值如下:

MOD = 0

SYN = 1

WL2,WL1,WL0取決于字長

FSL1=0,F(xiàn)SL0=0

FSP=1,負(fù)幀同步

SCD2=1

SCKD=1

SHFD=0

注意,對(duì)于信號(hào)處理應(yīng)用,來自DSP563xx的幀同步信號(hào)必須提供等距采樣。

應(yīng)用程序提示

接地及布置

安裝AD7911/AD7921的印刷電路板的設(shè)計(jì)應(yīng)使模擬和數(shù)字部分分開并限制在電路板的某些區(qū)域內(nèi)。這有助于使用容易分離的地平面。最小腐蝕技術(shù)通常對(duì)接地層最好,因?yàn)樗芴峁┳詈玫钠帘巍?shù)字和模擬接地層只能在一個(gè)地方連接。如果AD7911/AD7921處于多個(gè)設(shè)備需要AGND到DGND連接的系統(tǒng)中,則仍應(yīng)在一個(gè)點(diǎn)進(jìn)行連接,該點(diǎn)應(yīng)盡可能靠近AD7911/AD7921。

避免在設(shè)備下運(yùn)行數(shù)字線,因?yàn)檫@些耦合噪聲到模具上。模擬接地層應(yīng)允許在AD7911/AD7921下運(yùn)行,以避免噪聲耦合。連接到AD7911/AD7921的電源線應(yīng)使用盡可能大的跡線,以提供低阻抗路徑,并減少故障對(duì)電源線的影響。時(shí)鐘等快速開關(guān)信號(hào)應(yīng)采用數(shù)字接地進(jìn)行屏蔽,以避免向電路板的其他部分輻射噪聲,時(shí)鐘信號(hào)不得在模擬輸入附近運(yùn)行。避免數(shù)字和模擬信號(hào)交叉。電路板對(duì)側(cè)的跡線應(yīng)彼此成直角,以減少穿過電路板的影響。微帶技術(shù)是目前為止最好的,但并不總是可以與雙面板。在這種技術(shù)中,電路板的元件側(cè)專用于接地層,而信號(hào)則放置在焊料側(cè)。

良好的解耦也非常重要。模擬電源應(yīng)采用10μF鉭與0.1μF電容器并聯(lián)進(jìn)行解耦。為了從這些去耦元件中獲得最佳性能,用戶應(yīng)努力將去耦電容器與VDD和GND引腳之間的距離保持在最小值,并將各自的引腳連接起來。

外形尺寸

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國產(chǎn)降成本等解決方案,可承接項(xiàng)目開發(fā),以及元器件一站式采購服務(wù),類型有運(yùn)放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價(jià)格請(qǐng)咨詢?cè)诰€客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號(hào):粵ICP備2023092210號(hào)-1