特征

4臺ADC裝在一個包裝中

編碼串行數(shù)字輸出,每個通道有ECC

片上溫度傳感器

−95 dB信道間串擾

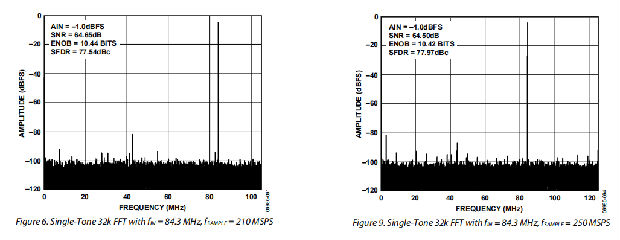

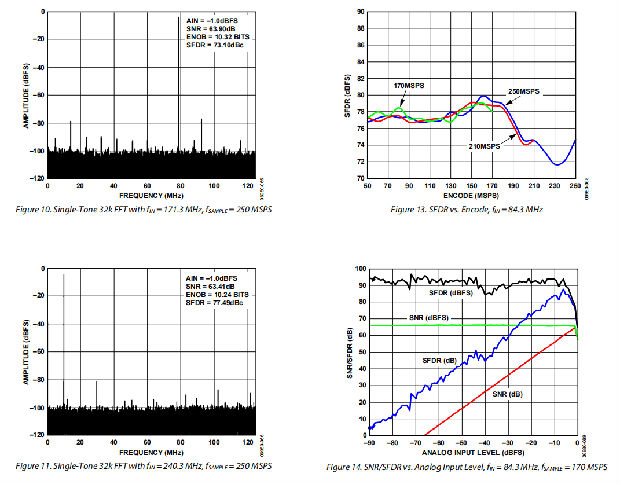

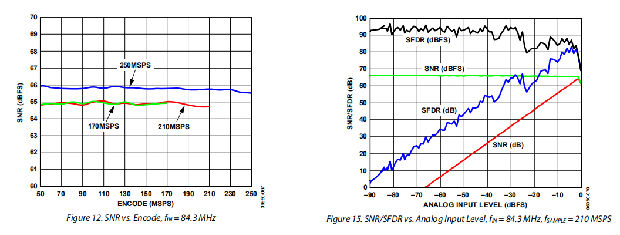

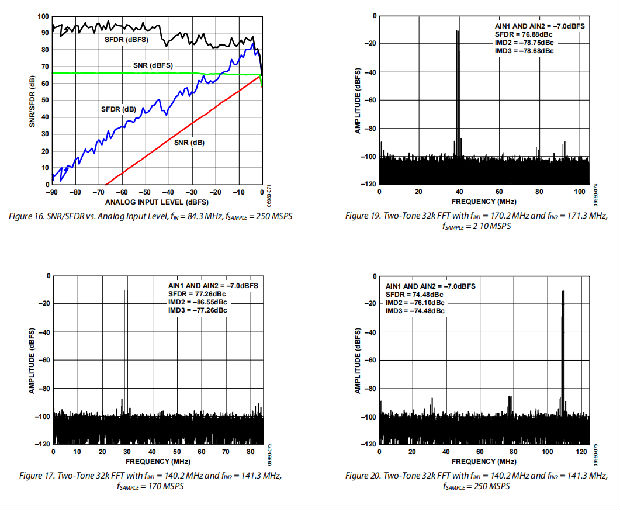

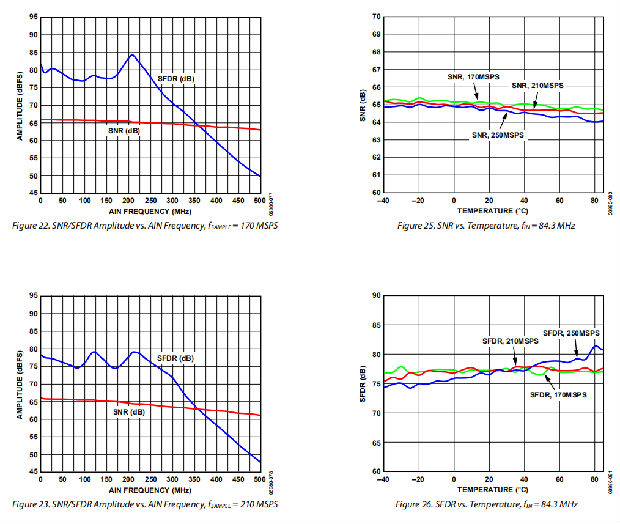

信噪比=65 dBFS,AIN=85 MHz,250 MSPS

SFDR=77 dBc,AIN=85 MHz,250 MSPS

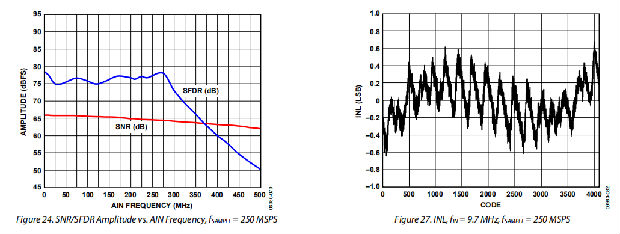

優(yōu)良的線性度

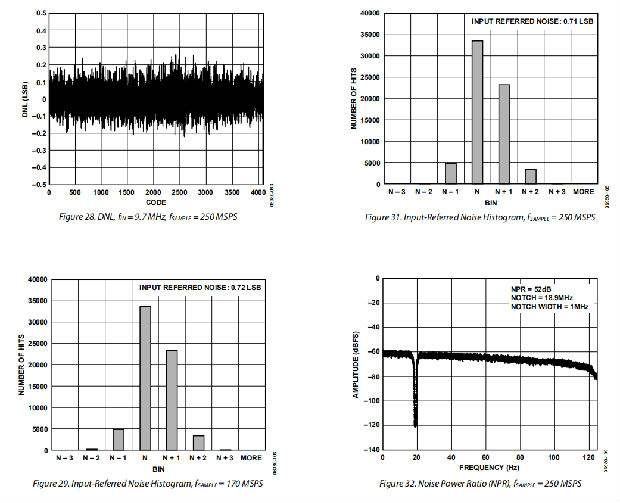

DNL=±0.3 LSB(典型)

INL=±0.7 LSB(典型)

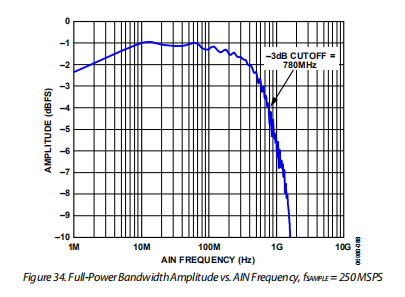

780 MHz全功率模擬帶寬

功率耗散=每通道380兆瓦,250兆瓦/秒

1.25 V p-p輸入電壓范圍,可調(diào)至1.5 V p-p

1.8 V電源操作

時鐘占空比穩(wěn)定器

串行端口接口具有斷電模式

數(shù)字測試模式啟用

可編程收割臺

可編程引腳功能(PGMx、PDWN)

應用

通信接收機

電纜頭端設(shè)備/M-CMTS

寬帶無線電

無線基礎(chǔ)設(shè)施收發(fā)器

雷達/軍用航空航天子系統(tǒng)

試驗設(shè)備

一般說明

AD9239是一個四位、12位、250 MSPS的模數(shù)轉(zhuǎn)換器(ADC),具有片上溫度傳感器和高速串行接口。它的設(shè)計支持數(shù)字化高頻,寬動態(tài)范圍的信號,輸入帶寬高達780兆赫。輸出數(shù)據(jù)被序列化并以包格式呈現(xiàn),包括信道特定信息、編碼樣本和糾錯代碼。

ADC需要一個1.8V電源,輸入時鐘可以用正弦波、LVPECL、TTL或LVDS進行差分驅(qū)動。時鐘占空比穩(wěn)定器允許高性能在全速和廣泛的時鐘占空比范圍。片上基準消除了外部解耦的需要,可以通過SPI控制進行調(diào)整。

支持多種斷電和待機模式。當啟用待機操作時,數(shù)字鏈路仍在運行時,ADC通常每個信道消耗145兆瓦。

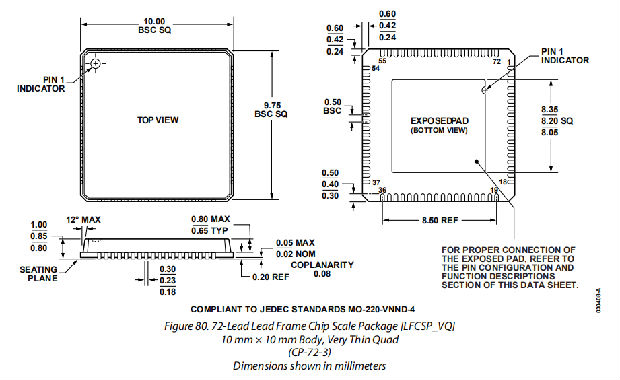

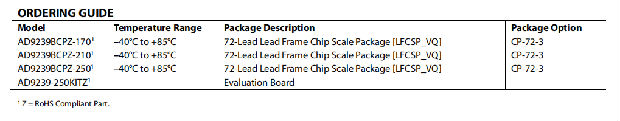

AD9239采用先進的CMOS工藝制造,采用無鉛/RoHS兼容的72引線LFCSP封裝。其規(guī)定的工業(yè)溫度范圍為−40°C至+85°C。

產(chǎn)品亮點

1.四個ADC包含在一個節(jié)省空間的小包裝中。

2.片上PLL允許用戶提供一個ADC采樣時鐘,PLL分配并倍增以產(chǎn)生相應的數(shù)據(jù)速率時鐘。

3.編碼數(shù)據(jù)速率支持每個通道高達4.0 Gbps。編碼包括加擾以確保正確的直流共模、嵌入式時鐘和糾錯。

4.AD9239由一個1.8伏電源供電。

5.靈活的同步方案和可編程模式引腳。

6.片上溫度傳感器。

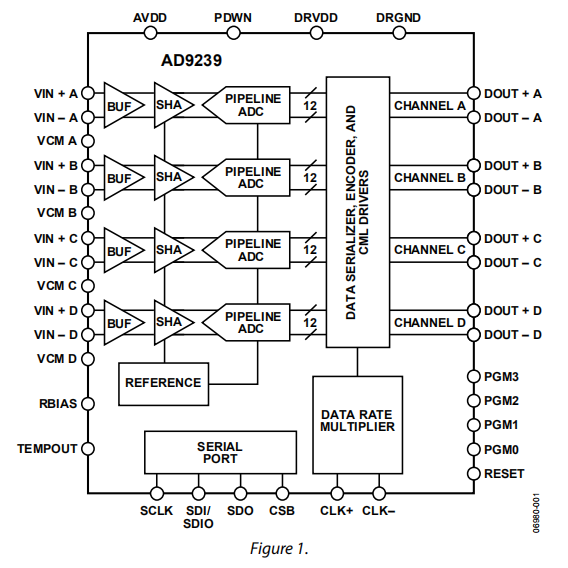

功能框圖

時序圖

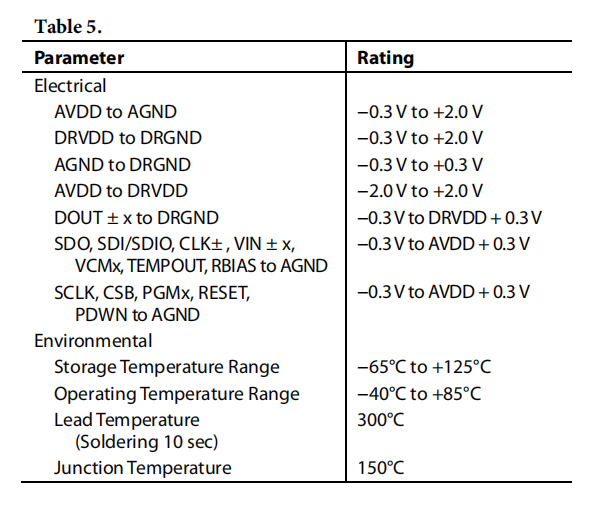

絕對最大額定值

超過絕對最大額定值的應力可能會對設(shè)備造成永久性損壞。這只是一個應力額定值;不暗示設(shè)備在本規(guī)范操作部分所述條件或任何其他條件下的功能操作。長時間暴露在絕對最大額定值條件下可能會影響設(shè)備的可靠性。

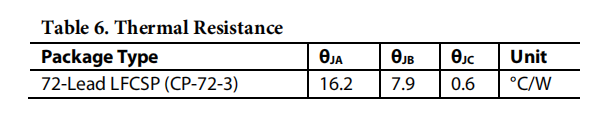

熱阻

必須將暴露的葉片焊接到LFCSP包的接地層上。將暴露的槳葉焊接到客戶板上增加了焊點的可靠性,最大限度地提高了封裝的熱容量。

典型的θJA、θJA和θJA值是為靜止空氣中的4層板指定的。氣流增加散熱,有效降低θJA。此外,與封裝直接接觸的金屬從金屬痕跡、通孔、接地和電源平面引出,減小了θJA。

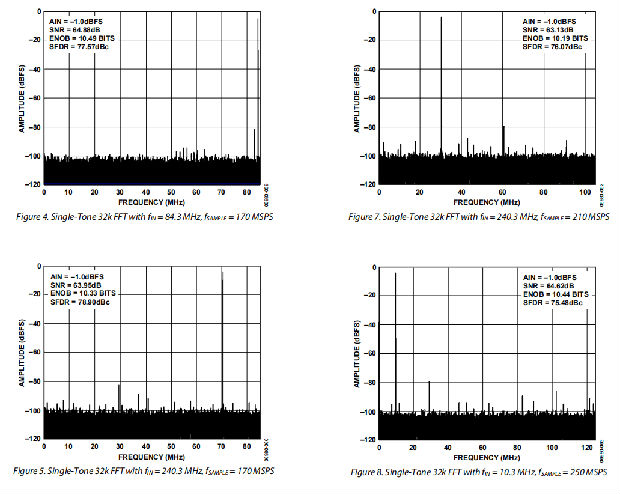

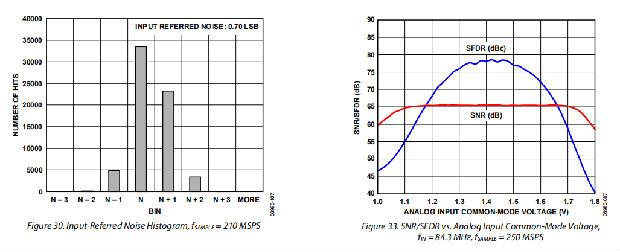

典型性能特征

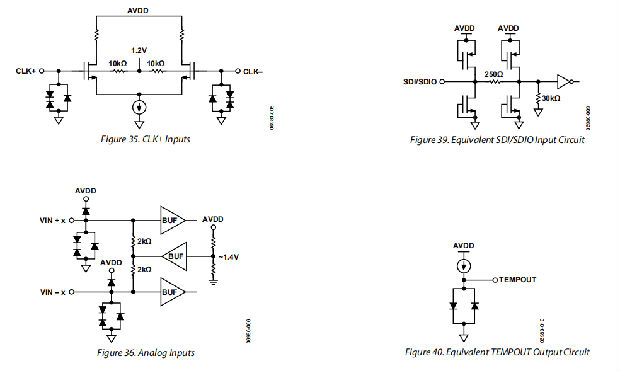

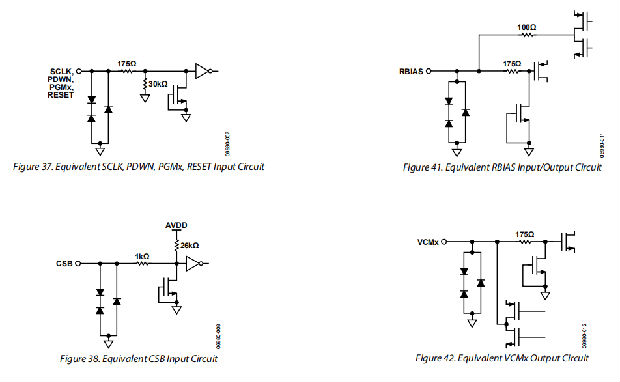

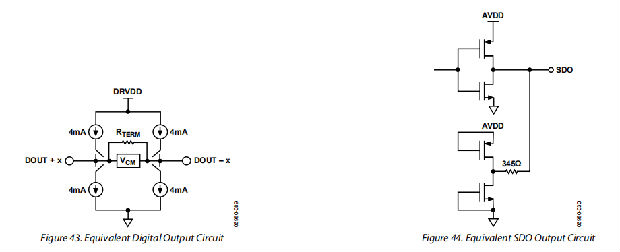

等效電路

操作理論

AD9239結(jié)構(gòu)由差分輸入緩沖器、前端采樣保持放大器(SHA)和流水線開關(guān)電容ADC組成。在數(shù)字校正邏輯中,每個級的量化輸出被組合成最終的12位結(jié)果。流水線結(jié)構(gòu)允許第一級對新的輸入樣本進行操作,而其余的階段則對之前的樣本進行操作。采樣發(fā)生在時鐘的上升沿。

管道的每一級(不包括最后一級)由連接到開關(guān)電容DAC的低分辨率flash ADC和級間剩余放大器(例如,乘法數(shù)模轉(zhuǎn)換器(MDAC))組成。剩余放大器放大了重構(gòu)的DAC輸出和流水線中下一級的flash輸入之間的差異。每個階段使用一位冗余,以便于閃存錯誤的數(shù)字校正。最后一級由一個flash ADC組成。

輸入級包含一個差分SHA,可以在差分或單端模式下進行交流或直流耦合。管道ADC的輸出由數(shù)據(jù)序列化器、編碼器和CML驅(qū)動程序塊轉(zhuǎn)換成最終的串行格式。數(shù)據(jù)速率倍增器創(chuàng)建用于在CML輸出端輸出高速串行數(shù)據(jù)的時鐘。

模擬輸入注意事項

AD9239的模擬輸入是一個差分緩沖器。該輸入經(jīng)過優(yōu)化以提供卓越的寬帶性能,并要求模擬輸入進行差分驅(qū)動。如果采用單端信號驅(qū)動模擬輸入,則信噪比和信噪比性能會下降。

為了獲得最佳動態(tài)性能,驅(qū)動VIN+x和VIN−x的源阻抗應匹配,以使共模穩(wěn)定誤差對稱。這些誤差通過ADC的共模抑制來減小。一個小電阻每個輸入端串聯(lián)有助于降低從驅(qū)動源輸出級注入的峰值瞬態(tài)電流。

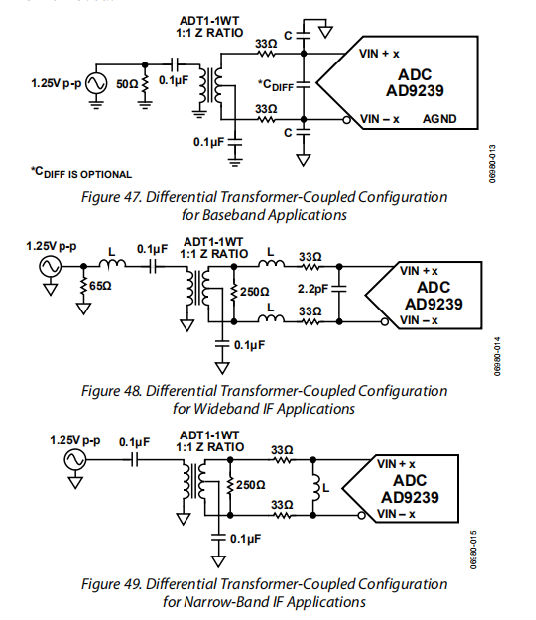

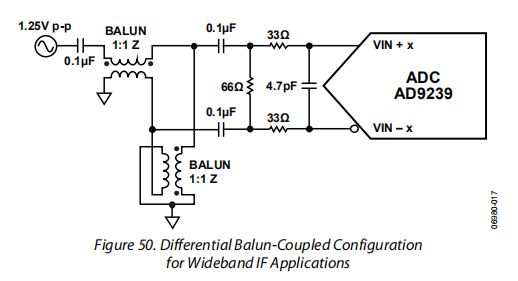

此外,低Q電感器或鐵氧體磁珠可以放置在輸入的每一個支路上,以減少模擬輸入端的高差分電容,從而實現(xiàn)ADC的最大帶寬。在高頻(IF)驅(qū)動變流器前端時,需要使用低Q電感器或鐵氧體磁珠。一個并聯(lián)電容器或兩個單端電容器可以放置在輸入端,以提供匹配的無源網(wǎng)絡(luò)。這最終在輸入端產(chǎn)生一個低通濾波器,以限制不必要的寬帶噪聲。參見AN-827應用說明和模擬對話文章“寬帶A/D轉(zhuǎn)換器的變壓器耦合前端”(第39卷,2005年4月)以獲取有關(guān)此主題的更多信息。通常,精確值取決于應用程序。

通過將ADC設(shè)置為差分配置中的最大跨距,可以實現(xiàn)最大的信噪比性能。對于AD9239,默認輸入量程為1.25 V p-p。要為不同的輸入量程配置ADC,請參閱寄存器18。為了獲得最佳性能,應使用1.25 V p-p或更大的輸入量程。

差分輸入配置

有幾種方法可以主動或被動地驅(qū)動AD9239;在任何一種情況下,都可以通過差分驅(qū)動模擬輸入來實現(xiàn)最佳性能。例如,使用ADA4937差分放大器驅(qū)動AD9239為基帶和第二奈奎斯特(~100 MHz IF)應用提供了卓越的性能和靈活的ADC接口(見圖45和圖46)。在任何一種應用中,1%的電阻應用于良好的增益匹配。還應注意的是,直流耦合配置將顯示雜散性能的一些退化。如需進一步參考,請參閱ADA4937數(shù)據(jù)表。

對于信噪比是一個關(guān)鍵參數(shù)的應用,差動變壓器耦合是推薦的輸入配置(見圖47至圖49),以實現(xiàn)AD9239的真正性能。

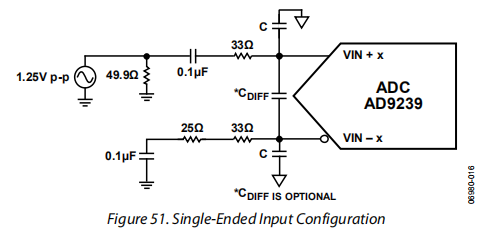

無論配置如何,并聯(lián)電容器C的值取決于輸入頻率,可能需要減小或移除。

單端輸入配置

單端輸入可以在成本敏感的應用程序中提供足夠的性能。在這種配置中,由于輸入共模擺幅不匹配,SFDR和失真性能會降低。如果應用需要單端輸入配置,確保每個輸入端的源阻抗匹配良好,以實現(xiàn)最佳性能。當VIN−x引腳終止時,1.25 V p-p的滿標度輸入可應用于ADC的VIN+x引腳。圖51詳細說明了典型的單端輸入配置。

時鐘輸入注意事項

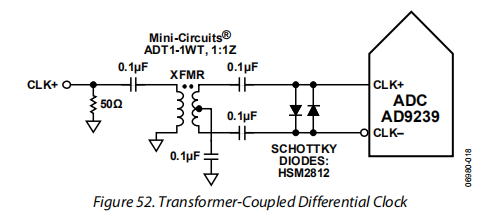

為獲得最佳性能,AD9239采樣時鐘輸入(CLK+和CLK-)應使用差分信號進行時鐘控制。該信號通常通過變壓器或電容器交流耦合到CLK+和CLK-引腳。這些引腳的內(nèi)部偏置為1.2V,無需額外偏置。

圖52顯示了為AD9239計時的首選方法。低抖動時鐘源使用射頻變壓器從單端信號轉(zhuǎn)換為差分信號。穿過二次變壓器的back-toback-Schottky二極管將進入AD9239的時鐘偏移限制到大約0.8v的p-p差。這有助于防止時鐘的大電壓波動通過AD9239的其他部分供電,并保持信號的快速上升和下降時間,這對低抖動性能至關(guān)重要。

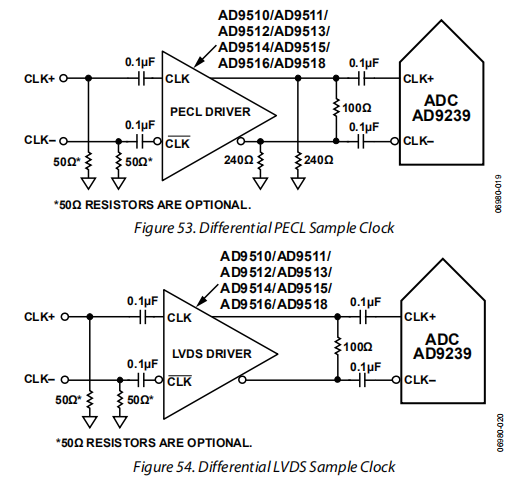

另一個選擇是交流耦合差分PECL信號到采樣時鐘輸入引腳,如圖53所示。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515/AD9516/AD9518系列時鐘驅(qū)動器提供了出色的抖動性能。

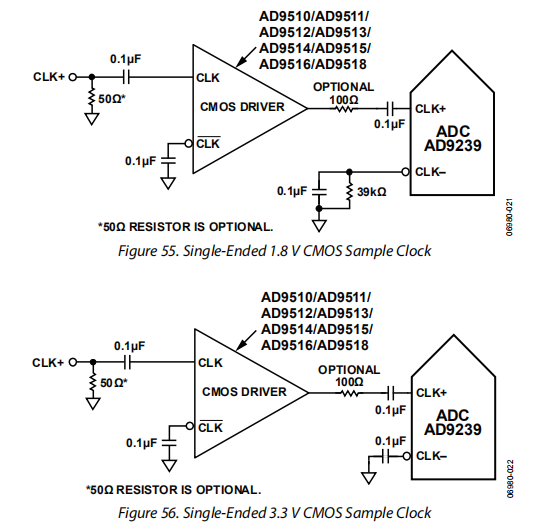

在某些應用中,用單端CMOS信號驅(qū)動采樣時鐘輸入是可以接受的。在這種應用中,CLK+應直接從CMOS柵極驅(qū)動,CLK-引腳應通過一個0.1μF電容器與一個39KΩ電阻器并聯(lián)接地(見圖55)。盡管CLK+輸入電路電源為AVDD(1.8 V),但該輸入設(shè)計為可承受高達3.3 V的輸入電壓,因此提供了多種驅(qū)動邏輯電壓選擇。

時鐘占空比考慮因素

典型的高速adc使用兩個時鐘邊緣來產(chǎn)生各種內(nèi)部定時信號。因此,這些adc可能對時鐘占空比很敏感。通常,時鐘占空比需要5%的公差以保持動態(tài)性能特性。

AD9239包含一個占空比穩(wěn)定器(DCS),該穩(wěn)定器對非采樣邊緣進行重定時,提供具有50%額定占空比的內(nèi)部時鐘信號。這樣就可以在不影響AD9239性能的情況下實現(xiàn)寬范圍的時鐘輸入占空比。當DCS開啟(默認)時,噪聲和失真性能在很大的占空比范圍內(nèi)幾乎沒有變化。但是,有些應用可能需要關(guān)閉DCS功能。如果是這樣,請記住,在這種模式下操作時,動態(tài)范圍性能可能會受到影響。有關(guān)使用此功能的更多詳細信息,請參閱內(nèi)存映射部分。

輸入端上升沿的抖動是一個重要的問題,內(nèi)部穩(wěn)定電路并不能減少這種抖動。占空比控制回路在低于50 MHz標稱時鐘頻率時不起作用。不建議此ADC時鐘是動態(tài)的。動態(tài)移動時鐘需要很長的等待時間,以便后端串行捕獲重定時并重新同步到接收邏輯。這個長時間常數(shù)遠遠超過了DSC和PLL鎖定和穩(wěn)定所需的時間。只有在極少數(shù)情況下,才有必要禁用寄存器9的DCS電路(見表14)。建議保持DCS電路啟用,以最大限度地提高交流性能。

時鐘抖動注意事項

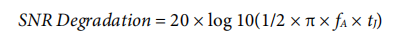

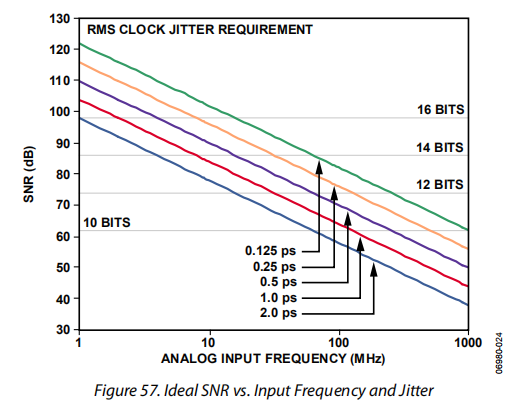

高速、高分辨率ADC對時鐘輸入的質(zhì)量很敏感。在給定輸入頻率(fA)下,僅由于孔徑抖動(tJ)而導致的信噪比下降可以通過以下公式計算:

在這個方程中,rms孔徑抖動代表所有抖動源的均方根,包括時鐘輸入、模擬輸入信號和ADC孔徑抖動。如果欠采樣應用程序?qū)Χ秳犹貏e敏感(參見圖57)。

在孔徑抖動可能影響AD9239動態(tài)范圍的情況下,時鐘輸入應被視為模擬信號。時鐘驅(qū)動器的電源應與ADC輸出驅(qū)動器電源分開,以避免用數(shù)字噪聲調(diào)制時鐘信號。低抖動,晶體控制振蕩器是最好的時鐘源。如果時鐘是從另一種類型的源(通過選通、除法或其他方法)生成的,則應在最后一步中用原始時鐘重定時。

請參閱AN-501應用說明,AN-756應用程序。

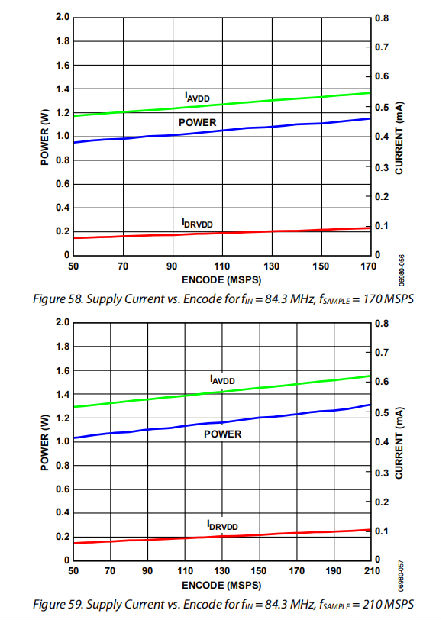

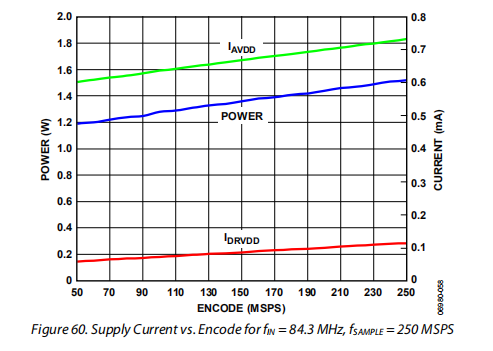

功率損耗

如圖58至圖60所示,AD9239消耗的功率與其時鐘頻率成正比。數(shù)字功耗變化不大,因為它主要由DRVDD電源和數(shù)字輸出驅(qū)動器的偏置電流決定。

數(shù)字啟動順序

從AD9239輸出的數(shù)字數(shù)據(jù)被編碼和打包,這要求設(shè)備有一定的啟動順序。用戶應初始化以下步驟,以便在接收邏輯處捕獲相干數(shù)據(jù)。

1、 通過寄存器0的位5初始化軟復位(見表14)。

2、 默認情況下,所有PGMx管腳自動初始化為同步管腳。這些引腳可用于在初始啟動期間鎖定FPGA定時和數(shù)據(jù)捕獲。這些引腳分別對應于每個通道(PGM3=通道A)。

3、 每個同步管腳保持在低位,直到其各自的PGMx管腳接收到來自接收器的高信號輸入,在此期間,ADC輸出一個訓練模式。

4、 訓練模式默認為用戶在寄存器19到寄存器20中實現(xiàn)的值。

5、 當接收器找到幀邊界時,同步標識通過同步管腳或SPI寫入被解除斷言。ADC在下一個分組邊界上輸出有效數(shù)據(jù)。同步建立所需的時間高度依賴于接收機的邏輯處理。請參閱“開關(guān)規(guī)格”部分;開關(guān)定時與ADC通道直接相關(guān)。

6、 一旦設(shè)備的穩(wěn)態(tài)操作發(fā)生,這些管腳可以通過使用寄存器53分配給備用選項(見表14)。所有其他管腳充當通用同步管腳。

為了使數(shù)字輸出的每個信道之間的偏差和時間偏差最小化,應采取以下措施以確保每個信道數(shù)據(jù)包在其指定交換時間的±1時鐘周期內(nèi)。對于某些接收器邏輯,這不是必需的。

1、 通過外部PDWN引腳完全斷電。

2、 通過外部復位引腳復位芯片。

3、 通過釋放外部PDWN引腳來恢復電源。

數(shù)字輸出和定時

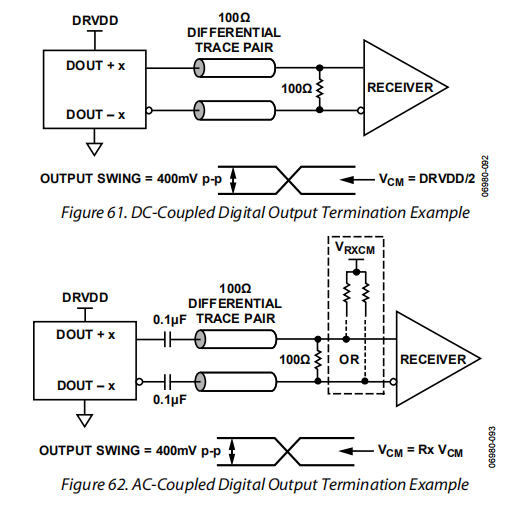

AD9239具有差分數(shù)字輸出,默認情況下通電。驅(qū)動電流在芯片上導出,并將每個輸出端的輸出電流設(shè)置為標稱8毫安。每個輸出都有一個100Ω動態(tài)內(nèi)部終端,以減少不必要的反射。應在每個接收器輸入端放置一個100Ω差動終端電阻器,以在接收器處產(chǎn)生標稱800 mV p-p擺動。或者,可使用單端50Ω終端。當使用單端終端時,終端電壓應為DRVDD/2;否則,交流耦合電容器可用于端接任何單端電壓。

AD9239數(shù)字輸出可與定制專用集成電路(ASIC)和現(xiàn)場可編程門陣列(FPGA)接收器接口,在噪聲環(huán)境中提供卓越的切換性能。建議采用單點對點網(wǎng)絡(luò)拓撲,并在盡可能靠近接收器邏輯的位置放置一個100Ω差分終端電阻器。如果使用直流耦合連接,數(shù)字輸出的共模自動將自身偏置到接收器電源的一半(即,對于1.8 V的接收器電源,共模電壓為0.9 V)。對于不在DRVDD電源范圍內(nèi)的接收器邏輯,應使用交流耦合連接。只需在每個輸出引腳上放置一個0.1μF電容器,并在靠近接收器側(cè)的位置引出一個100Ω差分終端。

如果沒有遠端接收器終端或差分跟蹤路由,可能會導致定時錯誤。為避免此類定時誤差,建議記錄道長度小于6英寸,并且差分輸出記錄道應靠近,且長度相等。

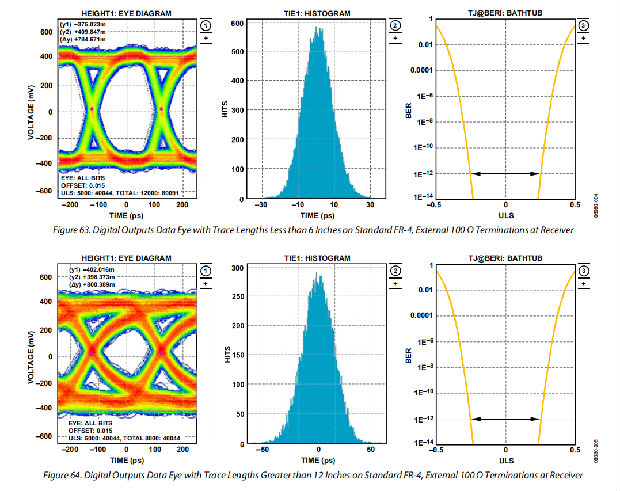

圖63顯示了標準FR-4材料上的數(shù)字輸出(默認)數(shù)據(jù)眼和時間間隔誤差(TIE)抖動直方圖,記錄道長度小于6英寸。圖64顯示了標準FR-4材料上超過12英寸的跡線長度示例。請注意,TIE jitter直方圖反映了當邊緣偏離理想位置時,數(shù)據(jù)眼睛張開度的減少。當跡線長度超過6英寸時,用戶有責任確定波形是否符合設(shè)計的時序預算。

附加的SPI選項允許用戶進一步增加所有四個輸出的輸出驅(qū)動器電壓擺幅,以驅(qū)動更長的記錄道長度(見表14中的寄存器15)。盡管這會在數(shù)據(jù)邊緣產(chǎn)生更大的上升和下降時間,并且不太容易發(fā)生誤碼,但使用此選項時,DRVDD電源的功耗會增加。有關(guān)更多詳細信息,請參閱內(nèi)存映射部分。

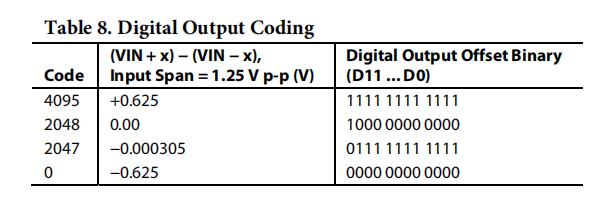

輸出數(shù)據(jù)的格式默認為偏移二進制。輸出編碼格式示例見表8。

要將輸出數(shù)據(jù)格式更改為twos補碼或格雷碼,請參閱內(nèi)存映射部分。

來自每個ADC的數(shù)據(jù)被序列化并在單獨的通道上提供。每個串行流的數(shù)據(jù)速率等于N位乘以采樣時鐘速率倍,此外還需要考慮8位報頭和糾錯的一些開銷,最大為3.15 Gbps(即,12位×210 MSPS×25%=3.15 Gbps)。最低的典型時鐘速率是100毫秒/秒。對于低于100毫秒/秒的時鐘速率,請參閱SPI內(nèi)存映射中的寄存器21。此選項允許用戶調(diào)整PLL環(huán)路帶寬,以便使用低至50msps的時鐘速率。

寄存器14允許用戶從其標稱狀態(tài)反轉(zhuǎn)數(shù)字輸出。這不應與將串行流反轉(zhuǎn)為LSB-first模式相混淆。在默認模式下,如圖2所示,MSB位于數(shù)據(jù)輸出串行流中的第一個。然而,這可以反轉(zhuǎn),以便LSB在數(shù)據(jù)輸出串行流中是第一個。

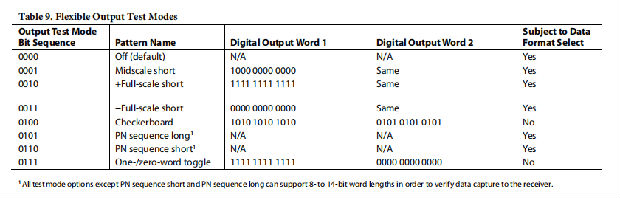

有八個數(shù)字輸出測試模式選項可通過SPI啟動。在驗證接收機捕獲和定時時,此功能非常有用。有關(guān)可用的輸出位排序選項,請參閱表9。有些測試模式有兩個連續(xù)的單詞,可以根據(jù)所選的測試模式以各種方式交替。需要注意的是,有些模式不符合數(shù)據(jù)格式選擇選項。此外,可以在0x19、0x1A、0x1B、0x1C、0x1D、0x1E、0x1F和0x20寄存器地址中分配自定義用戶定義的測試模式。

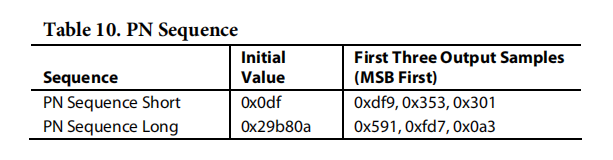

PN序列短模式產(chǎn)生每2−1或511比特重復自身的偽隨機比特序列。

PN序列長模式產(chǎn)生一個偽隨機比特序列,每2−1或8388607比特重復一次。

有關(guān)如何通過SPI更改這些附加數(shù)字輸出定時特性的信息,請參閱內(nèi)存映射部分。

數(shù)字輸出加擾器及糾錯碼

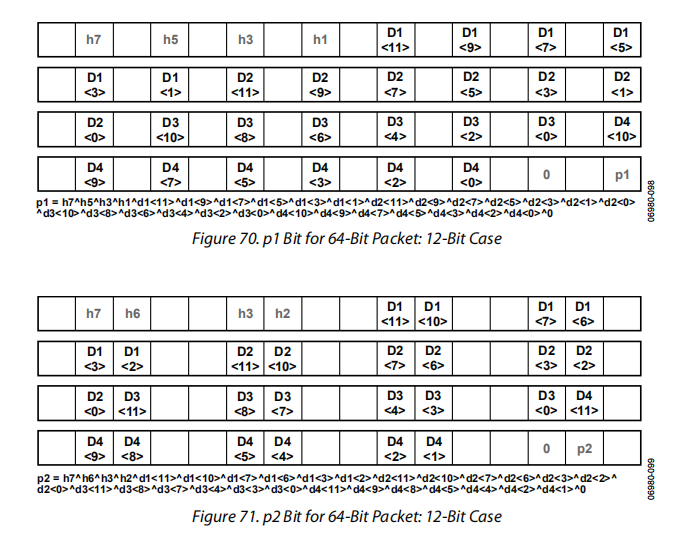

來自AD9239的數(shù)據(jù)以64位的數(shù)據(jù)包串行發(fā)送。這些數(shù)字源于輸出數(shù)據(jù)流為16×編碼時鐘的必要性。數(shù)據(jù)包包括報頭、數(shù)據(jù)和糾錯碼(即,8位報頭+48位數(shù)據(jù)(4個轉(zhuǎn)換)+8位ECC=64位)。12位協(xié)議如圖2和表1所示。

糾錯碼

糾錯碼(ECC)是一種易于實現(xiàn)的漢明碼。在傳輸過程中,ECC使用七位來糾正一個錯誤或檢測一個或兩個錯誤。

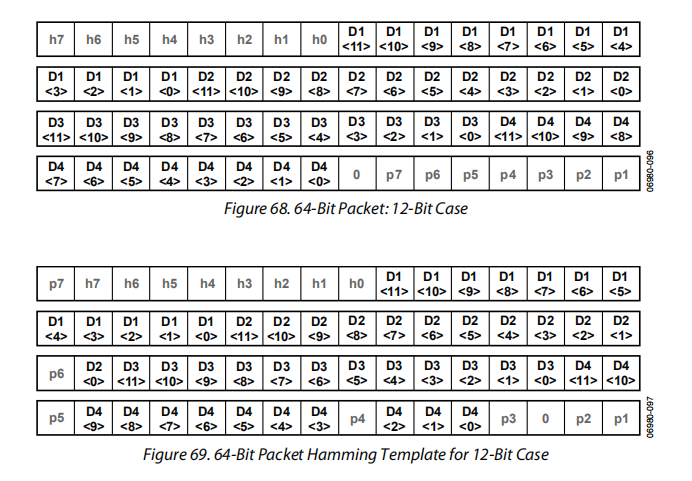

ECC的MSB始終為0,不用于檢測錯誤。ECC的六個LSB是給定位的異或的結(jié)果(參見圖68到圖75)。這些位允許對報頭和數(shù)據(jù)字段中的任何位進行奇偶校驗。

在計算出Hamming奇偶校驗位之后,第七個奇偶校驗位被應用于整個分組。此奇偶校驗允許糾正數(shù)據(jù)或ECC位中的錯誤。

在一般實現(xiàn)中,奇偶校驗位位于2個位置的冪次方,但是從這些位置提取并放在分組的末尾。圖68到圖75顯示了哪些報頭和數(shù)據(jù)位與奇偶校驗位相關(guān)聯(lián)。

在接收器中,執(zhí)行這些奇偶校驗并計算接收器奇偶校驗位。接收到的奇偶校驗位和計算出的奇偶校驗位之間的差表示哪個位出錯了。

擾頻器

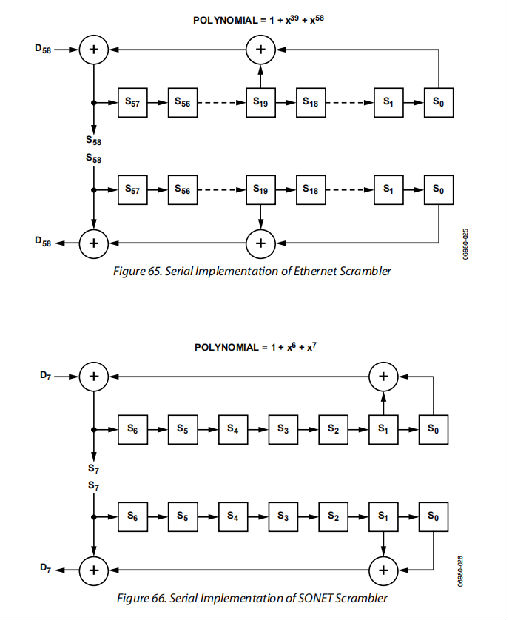

AD9239上有三個擾頻器。擾頻器是以太網(wǎng)擾頻器(x58+x39+1)、SONET擾頻器(x7+x6+1)和靜態(tài)逆變擾頻器(在分組中的設(shè)定位置反轉(zhuǎn)比特)。擾頻器用于幫助平衡包中1和0的數(shù)量。

以太網(wǎng)和SONET加擾器對整個數(shù)據(jù)包(64位)、報頭和數(shù)據(jù)(56位)或僅對數(shù)據(jù)(48位)進行加擾。擾頻器在解擾端或接收端自同步,不需要額外的同步位。要獲取以太網(wǎng)或SONET擾碼器代碼的副本,請發(fā)送電子郵件至高速變頻器@模擬網(wǎng). 圖65和圖66顯示了以太網(wǎng)和SONET加擾器的串行實現(xiàn)。并行實現(xiàn)允許擾頻器和解擾器以較低的時鐘速率運行,并且可以在接收機的結(jié)構(gòu)中實現(xiàn)。

以太網(wǎng)和SONET加擾器的串行實現(xiàn)更容易顯示正在做什么。并行實現(xiàn)必須從串行實現(xiàn)派生。最終產(chǎn)品取決于需要并行處理多少位。對于擾頻器,即使在56位和48位的情況下也要處理64位。為了在56位和48位上實現(xiàn)這一點,兩個樣本的一部分用于填充輸入字的其余部分。

逆變器平衡示例

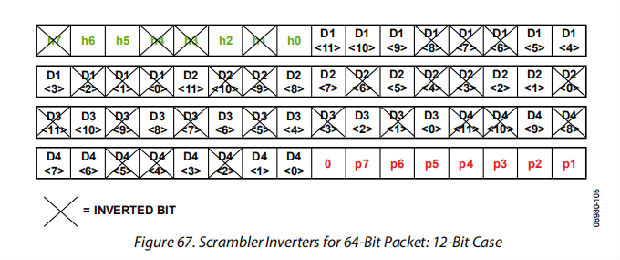

反相器實現(xiàn)使用預先確定的位位置來平衡轉(zhuǎn)換器中的超量程條件(全部為1或全部為0)。所有的情況下都會出現(xiàn)反轉(zhuǎn),而不僅僅是超量程的情況。

解擾器可以基于用戶的任意位數(shù)選擇處理。在基于反相器的擾碼器中,分組是基于超范圍條件來平衡的。如果每個數(shù)據(jù)包都是平衡的,那么比特流應該是平衡的。代替從一個包到另一個包的隨機序列,某些反轉(zhuǎn)被設(shè)置在包內(nèi)的預定比特位置。這使得解碼可以在接收端完成。圖67顯示了12位數(shù)據(jù)情況下數(shù)據(jù)包中的反相器以及報頭中的反相器順序。

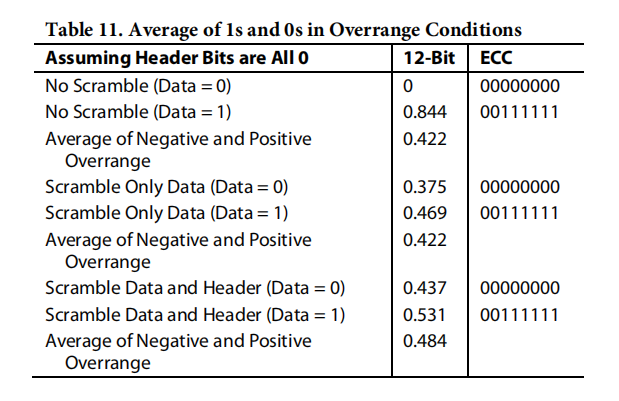

表11顯示了各種情況下的數(shù)據(jù)包平均值。

如果模擬信號超出范圍,則超出范圍的正值和超出范圍的負值應大致相同。不加擾和僅加擾數(shù)據(jù)的平均值大致相同。如果報頭用于指示超出范圍,則12位情況下的平衡將得到改善。

計算漢明碼的奇偶校驗位

漢明比特的定義如下。圖中給出了一個12位示例的定義。漢明奇偶校驗位交織在數(shù)據(jù)中。這樣可以更容易地看到數(shù)字關(guān)系。接收端的解碼只是反轉(zhuǎn)。另一份文件將說明如何正確糾正傳輸中的錯誤。

p8位(奇偶校驗位的MSB)始終為0。p7位是計算完其他奇偶校驗位后,整個數(shù)據(jù)包的奇偶校驗位。

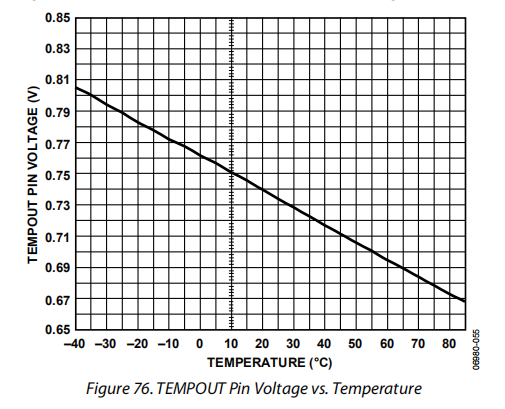

溫度輸出引腳

TEMPOUT引腳可用作過程溫度傳感器來監(jiān)測器件的內(nèi)部模具溫度。該引腳的典型輸出為734毫伏,時鐘頻率為250毫秒/秒,負溫升系數(shù)為−1.12毫伏/攝氏度。該引腳的電壓響應如圖76所示。

RBIAS引腳

要設(shè)置ADC的內(nèi)部核心偏置電流,在接地和RBIAS引腳之間放置一個電阻器(名義上等于10.0 kΩ)。電阻電流在芯片上導出,并將ADC的AVDD電流設(shè)置為250 MSPS時的標稱725 mA。因此,必須在該電阻器上使用1%或更小的公差,以獲得一致的性能。

VCMx引腳

通過VIN x的外部驅(qū)動電壓,可以為VIN x的外部輸入+V提供一個參考電壓。當連接外部設(shè)備(如放大器或變壓器)與模擬輸入接口時,可能需要這些引腳。

復位引腳

復位引腳將所有SPI寄存器設(shè)置為其默認值和數(shù)據(jù)路徑。使用此引腳需要用戶重新同步數(shù)字輸出。該引腳僅允許1.8 V電壓。

PDWN引腳

當斷言為高電平時,PDWN引腳關(guān)閉所有ADC通道,包括輸出驅(qū)動器。此功能可以更改為備用功能。見表14中的寄存器8。使用此功能,用戶可以將所有頻道置于待機模式。輸出驅(qū)動器發(fā)送偽隨機數(shù)據(jù),直到使用寄存器14禁用輸出。

通過斷言PDWN引腳高,AD9239被置于斷電模式,關(guān)閉參考、參考緩沖器、PLL和偏置網(wǎng)絡(luò)。在這種狀態(tài)下,ADC通常消耗3mw。如果任何SPI特性在斷電功能啟用之前被更改,則在PDWN被拉低后芯片繼續(xù)工作,而不需要重置。當PDWN引腳拉低時,AD9239返回正常工作模式。該引腳僅允許1.8 V電壓。

SDO引腳

SDO引腳用于需要4線SPI模式操作的應用。為了正常工作,它應該通過一個10 kΩ的電阻器與AGND相連。或者,設(shè)備引腳可以保持打開,345Ω內(nèi)部下拉電阻器將該引腳拉低。該引腳僅符合1.8 V邏輯。

SDI/SDIO引腳

SDI/SDIO引腳用于需要4線或3線SPI模式操作的應用。為了正常工作,它應該通過一個10 kΩ的電阻器與AGND相連。或者,裝置引腳可以保持打開狀態(tài),30kΩ的內(nèi)部下拉電阻將該引腳拉低。該引腳僅允許1.8 V電壓。

SCLK引腳

對于正常操作,SCLK引腳應通過一個10 kΩ的電阻器連接到AGND。或者,裝置引腳可以保持打開,30kΩ的內(nèi)部下拉電阻器將該引腳拉低。該引腳僅允許1.8 V電壓。

CSB引腳

正常工作時,CSB引腳應通過一個10 kΩ的電阻器與AVDD相連。或者,裝置引腳可以保持打開狀態(tài),26kΩ的內(nèi)部上拉電阻將該引腳拉高。通過將CSB引腳綁定到AVDD,所有SCLK和SDI/SDIO信息都將被忽略。相比之下,通過將CSB引腳綁低,SDO和SDI/SDIO引腳上的所有信息都寫入設(shè)備。此功能允許用戶在必要時減少對設(shè)備的跟蹤數(shù)。該引腳僅允許1.8 V電壓。

PGMx引腳

默認情況下,所有PGMx管腳都自動初始化為同步管腳。這些引腳用于在初始啟動期間鎖定FPGA定時和數(shù)據(jù)捕獲。這些引腳分別對應于每個通道(PGM3=通道A)。同步管腳應拉低,直到該管腳接收到來自接收器的高信號輸入,在此期間,ADC輸出一個訓練字。訓練字默認為用戶在寄存器19到寄存器20中實現(xiàn)的值。當接收器找到幀邊界時,同步標識被解除斷言為高電平,ADC在下一個分組邊界上輸出有效數(shù)據(jù)。

一旦設(shè)備發(fā)生穩(wěn)態(tài)操作,這些管腳可使用表14中的寄存器53分配為備用選項。所有其他管腳更改為全局同步管腳。

該引腳僅允許1.8 V電壓。

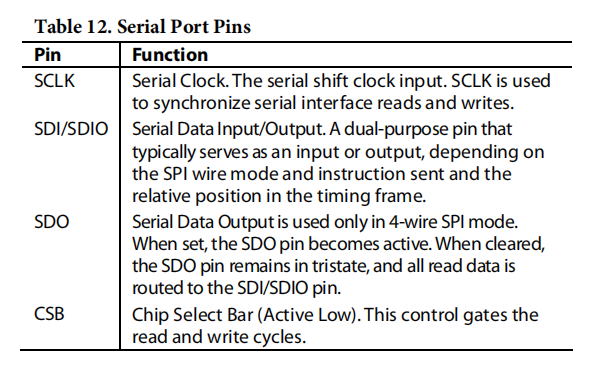

串行端口接口(SPI)

AD9239串行端口接口允許用戶通過ADC中提供的結(jié)構(gòu)化寄存器空間為特定功能或操作配置轉(zhuǎn)換器。這可能為用戶提供額外的靈活性和定制,具體取決于應用程序。地址通過串行端口訪問,可以通過該端口寫入或讀取。內(nèi)存被組織成字節(jié),這些字節(jié)可以進一步劃分為字段,如內(nèi)存映射部分中所述。詳細的操作信息可以在模擬設(shè)備公司,AN-877應用說明中找到,通過SPI接口到高速ADC。

四個引腳定義SPI:SCLK、SDI/SDIO、SDO和CSB(見表12)。SCLK引腳用于同步呈現(xiàn)給ADC的讀寫數(shù)據(jù)。SDI/SDIO引腳是一個雙用途引腳,它允許向內(nèi)部ADC內(nèi)存映射寄存器發(fā)送和讀取數(shù)據(jù)。CSB引腳是一個激活的低電平控制,用于啟用或禁用讀寫循環(huán)。

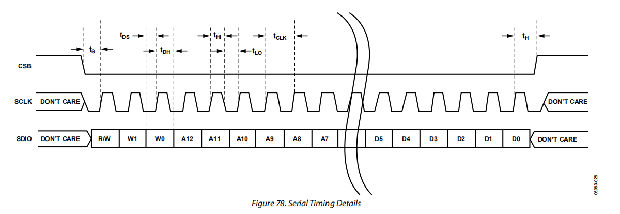

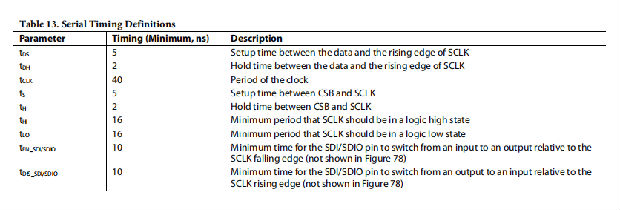

CSB的下降沿和SCLK的上升沿共同決定幀序列的開始。在指令階段,傳輸一條16位指令,隨后傳輸一個或多個數(shù)據(jù)字節(jié),由位字段W0和位字段W1確定。圖78和表13提供了串行定時及其定義的示例。

在正常操作期間,CSB用于向設(shè)備發(fā)出信號,指示要接收和處理SPI命令。當CSB降低時,設(shè)備處理SCLK和SDI/SDIO來執(zhí)行指令。通常,在通信周期完成之前,CSB保持在低水平。然而,如果連接到一個速度慢的設(shè)備,CSB可以在字節(jié)之間調(diào)高,從而允許老的微控制器有足夠的時間將數(shù)據(jù)傳輸?shù)揭莆患拇嫫髦小.攤鬏斠粋€、兩個或三個字節(jié)的數(shù)據(jù)時,CSB可能會暫停。當W0和W1設(shè)置為11時,設(shè)備進入流模式并繼續(xù)處理數(shù)據(jù),無論是讀還是寫,直到CSB取高結(jié)束通信循環(huán)。這使得完全的內(nèi)存?zhèn)鬏敳恍枰~外的指令。不管是哪種模式,如果CSB在字節(jié)傳輸過程中處于高位,SPI狀態(tài)機將重置,設(shè)備將等待新的指令。

除了操作模式外,SPI端口配置還影響AD9239的工作方式。對于不需要控制端口的應用程序,可以將CSB線綁在高處。這會將SDI/SDIO引腳置于其輔助模式,如SDI/SDIO引腳部分所定義。CSB也可以綁低以啟用2線模式。當CSB處于低位時,SCLK和SDI/SDIO是通信所需的唯一引腳。雖然設(shè)備在通電期間是同步的,但用戶應確保串行端口在使用此模式時與CSB線路保持同步。在雙線模式下運行時,建議獨占使用1、2或3字節(jié)傳輸。沒有活動的CSB線路,可以進入流模式,但不能退出。

除了字長之外,指令階段還決定串行幀是讀操作還是寫操作,允許串行端口同時用于對芯片進行編程并讀取片上存儲器的內(nèi)容。如果指令是回讀操作,則執(zhí)行回讀操作會導致SDI/SDIO引腳在串行幀的適當點從輸入變?yōu)檩敵觥?/p>

數(shù)據(jù)可以在MSB-或LSB-first模式下發(fā)送。MSB first模式是加電時的默認模式,可以通過調(diào)整配置寄存器來更改。有關(guān)此功能和其他功能的更多信息,請參閱AN-877應用說明,通過SPI接口到高速ADC。

硬件接口

表12中所述的管腳構(gòu)成用戶編程設(shè)備和AD9239串行端口之間的物理接口。使用SPI時,SDO、SCLK和CSB引腳作為輸入。SDI/SDIO引腳是雙向的,在寫入階段作為輸入,在回讀期間作為輸出。

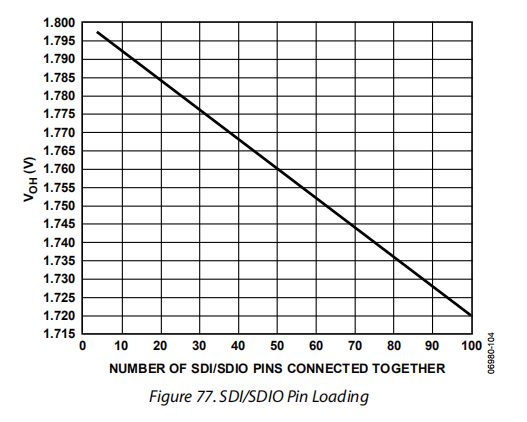

如果多個SDI/SDIO引腳共用一個公共連接,應注意確保滿足適當?shù)腣OH電平。假設(shè)每個AD9239的負載相同,圖77顯示了可以連接在一起的SDI/SDIO引腳的數(shù)量以及由此產(chǎn)生的VOH電平。該接口足夠靈活,可以由串行PROM或PIC微控制器控制,為用戶提供了一種替代方法,而不是完全SPI控制器,來編程ADC(參見an-812應用說明)。

對于希望在不使用ADC的情況下操作ADC的用戶從CSB、SCLK、SDO和SDI/SDIO引腳上移除所有連接。通過斷開這些引腳與控制總線的連接,ADC可以在其最基本的操作中工作。每一個引腳都有一個內(nèi)部終端,浮動到各自的水平。

內(nèi)存映射

讀取內(nèi)存映射表

內(nèi)存映射寄存器表(表14)中的每一行有8個位位置。內(nèi)存映射分為三個部分:芯片配置寄存器(地址0x00到地址0x02)、設(shè)備索引和傳輸寄存器(地址0x05和地址0xFF)以及ADC功能寄存器(地址0x08到地址0x53)。

內(nèi)存映射的最左邊一列表示寄存器地址號,默認值顯示在第二個最右邊的列中。第7位列是給定的默認十六進制值的開始。例如,地址0x09,時鐘寄存器,有一個默認值0x01,這意味著比特7=0,比特6=0,比特5=0,比特4=0,比特3=0,比特2=0,比特1=0,比特0=1,或者二進制的0000 0001。此工作循環(huán)的默認設(shè)置為穩(wěn)定器接通。通過在寄存器0xFF(傳輸位)中寫入0到0位,然后在寄存器0xFF(傳輸位)中寫入0x01,占空比穩(wěn)定器關(guān)閉。重要的是在每個寫入序列之后都有一個傳輸位來更新SPI寄存器。有關(guān)此功能和其他功能的更多信息,請參閱AN-877應用說明,通過SPI接口到高速ADC。

保留位置

除非寫入本數(shù)據(jù)表中建議的默認值,否則不應寫入未定義的內(nèi)存位置。值標記為0的地址應視為保留地址,并在通電期間將0寫入其寄存器。

默認值

當AD9239從復位中出來時,關(guān)鍵寄存器被預先加載了默認值。這些值如表14所示,其中X表示未定義的特性。

邏輯電平

對各種寄存器的解釋如下:“bit is set”與“bit is set to Logic 1”或“writing Logic 1 for the bit”同義。同樣,“clear a bit”與“bit is set to”同義“邏輯0”或“為位寫入邏輯0”。

電源和接地建議

將電源連接到AD9239時,建議使用兩個單獨的1.8 V電源:一個用于模擬(AVDD)和一個用于數(shù)字(DRVDD)。如果只有一個電源可用,則應首先將其路由至AVDD,然后分接并用鐵氧體磁珠或濾波扼流圈隔離,然后再為DRVDD提供去耦電容器。用戶可以使用幾種不同的去耦電容器來覆蓋高頻和低頻。它們應位于靠近印刷電路板(PCB)水平的入口點,并靠近零件,且軌跡長度最小。

使用AD9239時,一個PCB接地平面就足夠了。通過對PCB的模擬、數(shù)字和時鐘部分進行適當?shù)慕怦詈椭悄軇澐郑梢暂p松實現(xiàn)最佳性能。

暴露槳葉熱段塞建議

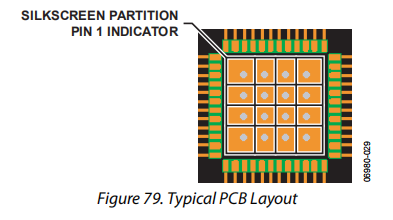

為了達到AD9239的最佳電性能和熱性能,需要將AD9239下面的裸露擋板連接到模擬地(AGND)。PCB上的一個暴露的連續(xù)銅平面應與AD9239暴露的撥桿(引腳0)相匹配。銅平面應具有多個通孔,以實現(xiàn)盡可能低的熱電阻路徑,以使散熱流經(jīng)PCB底部。這些通孔應使用不導電環(huán)氧樹脂填充或堵塞。

為了最大限度地提高ADC和PCB之間的覆蓋率和附著力,通過在PCB上覆蓋一個絲網(wǎng)將連續(xù)的銅平面分割成幾個均勻的部分。在回流焊過程中,這在ADC和PCB之間提供了幾個連接點,而使用一個沒有分區(qū)的連續(xù)平面保證只有一個連接點。參見圖79了解PCB布局例子。

外形尺寸

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍牙WIFI模組、進口芯片替換國產(chǎn)降成本等解決方案,可承接項目開發(fā),以及元器件一站式采購服務(wù),類型有運放芯片、電源芯片、MO芯片、藍牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導體/HDSC_華大半導體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導體/TD_TECHCODE美國泰德半導體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1