特征

•基于2:6 PLL的高性能時(shí)鐘合成器/乘法器/分頻器

•用戶可編程PLL頻率

•通過SMBus數(shù)據(jù)接口輕松進(jìn)行在線編程

•寬PLL分頻比允許0-PPM輸出時(shí)鐘誤差

•接受單端CMOS時(shí)鐘輸入或LVA差分輸入

•可接收8 MHz至54 MHz的晶體頻率

•支持高達(dá)200 MHz的LVCMOS或差分輸入頻率

•兩個(gè)可編程控制輸入[S0/S1],用于用戶定義的控制信號

•六個(gè)LVCMOS輸出,輸出頻率高達(dá)300 MHz

•LVCMOS輸出可編程為互補(bǔ)信號

•通過可編程輸出開關(guān)矩陣[6x6]自由選擇輸出頻率,包括每個(gè)輸出的7位后分頻器

•集成PLL環(huán)路濾波器組件

•低周期抖動(典型60 ps)

•采用擴(kuò)頻時(shí)鐘(SSC)降低系統(tǒng)EMI

•用于降低系統(tǒng)EMI的可編程輸出轉(zhuǎn)換速率控制(SRC)

•3.3V設(shè)備電源

•工業(yè)溫度范圍–40°C至85°C

•易于PLL設(shè)計(jì)和編程的開發(fā)和編程工具(TI Pro時(shí)鐘™)

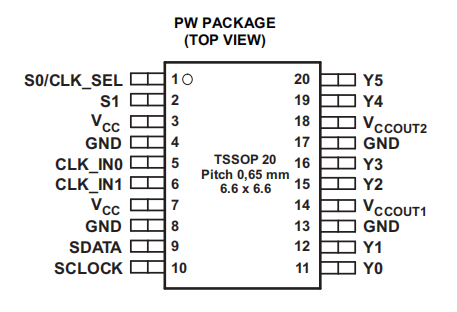

•采用20針TSSOP包裝

•工廠可編程定制默認(rèn)設(shè)置。更多詳情請聯(lián)系TI銷售部。

應(yīng)用

•無線基站

•網(wǎng)卡

•數(shù)據(jù)通信/電信

終端分配

說明

CDC706是目前最小且功能強(qiáng)大的PLL合成器/倍增器/分頻器之一。盡管外形小巧,CDC706非常靈活。它能夠從給定的輸入頻率產(chǎn)生幾乎獨(dú)立的輸出頻率。

輸入頻率可由LVCMOS、差分輸入時(shí)鐘或單晶導(dǎo)出。可通過SMBus數(shù)據(jù)接口控制器選擇適當(dāng)?shù)妮斎氩ㄐ巍?/p>

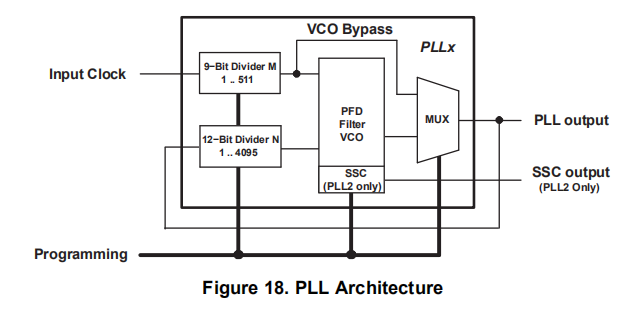

為了實(shí)現(xiàn)獨(dú)立的輸出頻率,每個(gè)PLL的參考分頻器M和反饋分頻器N可以設(shè)置為M分頻器的1到511以及N分頻器的1到4095的值。PLL-VCO(壓控振蕩器)頻率比被路由到自由可編程輸出開關(guān)矩陣的六個(gè)輸出中的任何一個(gè)。開關(guān)矩陣包括額外的7位后除法器(1到127)和每個(gè)輸出的逆變邏輯。

深M/N分頻比允許從任何參考輸入頻率(例如,27兆赫)產(chǎn)生零ppm時(shí)鐘。

CDC706包括三個(gè)pll,其中一個(gè)支持SSC(擴(kuò)頻時(shí)鐘)。PLL1、PLL2和PLL3的設(shè)計(jì)頻率高達(dá)300 MHz,并針對具有寬分頻因子的零ppm應(yīng)用進(jìn)行了優(yōu)化。

PLL2還支持中心擴(kuò)頻和下行擴(kuò)頻時(shí)鐘(SSC)。這是減少電磁干擾的常用技術(shù)。此外,旋轉(zhuǎn)速率可控(SRC)輸出邊最小化了EMI噪聲。

根據(jù)鎖相環(huán)頻率和分頻器設(shè)置,內(nèi)部環(huán)路濾波器元件將自動調(diào)整,以實(shí)現(xiàn)鎖相環(huán)的高穩(wěn)定性和最佳抖動傳輸特性。

該設(shè)備提供定制應(yīng)用程序。它使用出廠默認(rèn)配置進(jìn)行了預(yù)編程(參見圖13),并且可以通過串行SMBus接口將其重新編程為不同的應(yīng)用程序配置。

兩個(gè)自由可編程輸入,S0和S1,可用于控制每個(gè)應(yīng)用最苛刻的邏輯控制設(shè)置(輸出禁用到低,輸出3態(tài),斷電,PLL旁路等)。

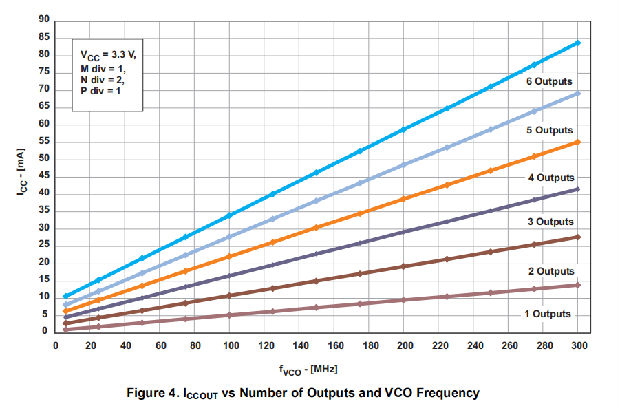

CDC706有三個(gè)電源引腳,VCC、VCCOUT1和VCCOUT2。VCC是設(shè)備的電源。它的工作電壓為3.3伏。VCCOUT1和VCCOUT2是輸出的電源引腳。VCCOUT1為輸出Y0和Y1供電,VCOUT2為輸出Y2、Y3、Y4和Y5供電。兩個(gè)輸出電源可以是2.3伏到3.6伏。當(dāng)輸出電壓低于3.3伏時(shí),輸出電流驅(qū)動受到限制。

CDC706的特點(diǎn)是在-40°C到85°C的溫度下工作。

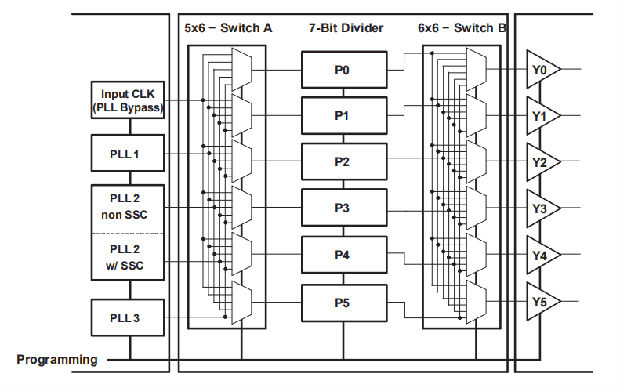

功能框圖

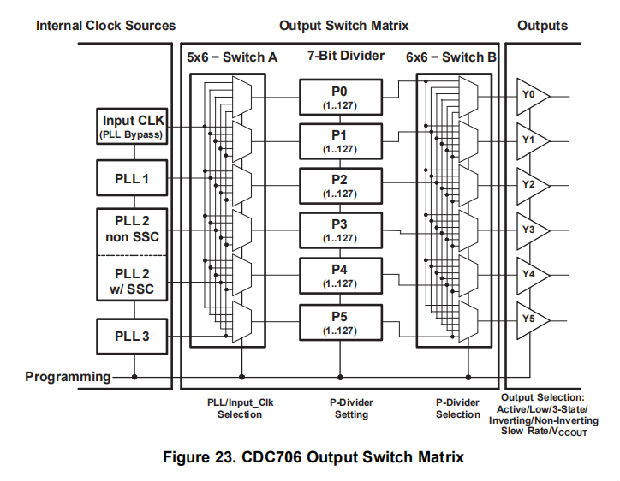

輸出開關(guān)矩陣

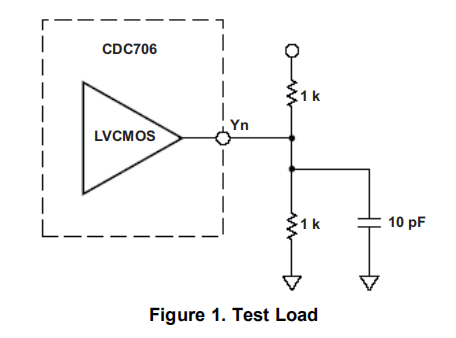

參數(shù)測量信息

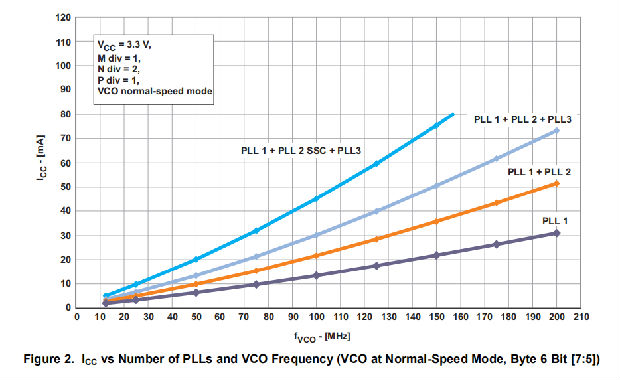

典型特征

申請信息

SMBus數(shù)據(jù)接口

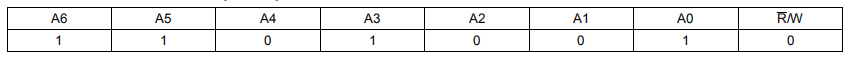

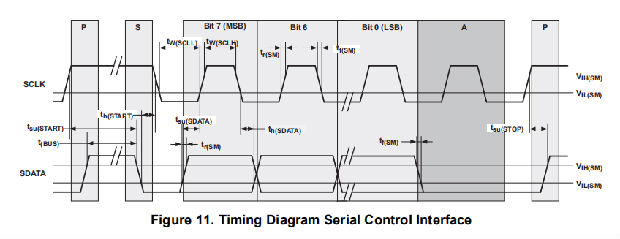

為了提高時(shí)鐘合成器的靈活性和功能,提供了一個(gè)雙信號串行接口。它遵循SMBus規(guī)范版本2.0,它基于I2C的操作原理http://www.smbus.org。

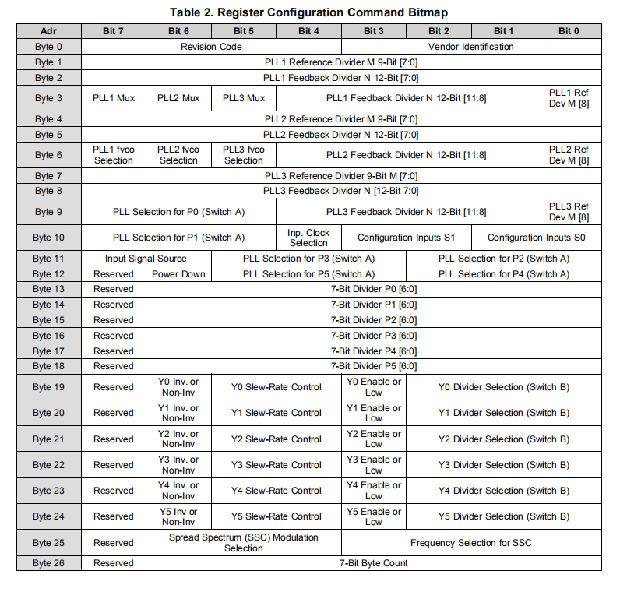

通過SMBus,可以單獨(dú)啟用或禁用各種設(shè)備功能,例如單個(gè)時(shí)鐘輸出緩沖區(qū)。與SMBus數(shù)據(jù)接口相關(guān)聯(lián)的寄存器在通電時(shí)初始化為其默認(rèn)設(shè)置;因此,使用此接口是可選的。時(shí)鐘設(shè)備寄存器的更改通常在系統(tǒng)初始化時(shí)進(jìn)行,如果需要的話。

數(shù)據(jù)協(xié)議

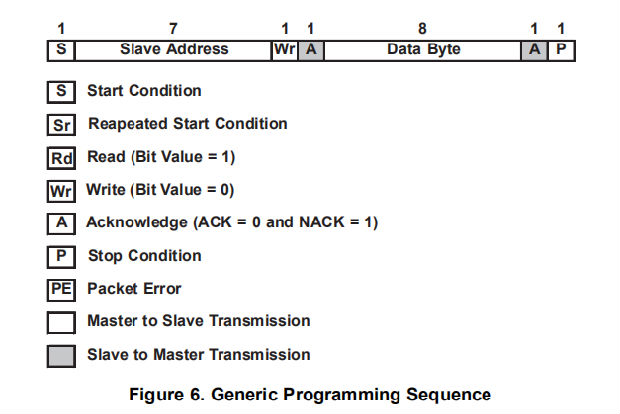

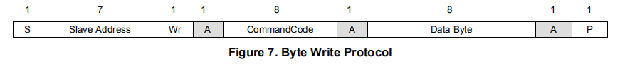

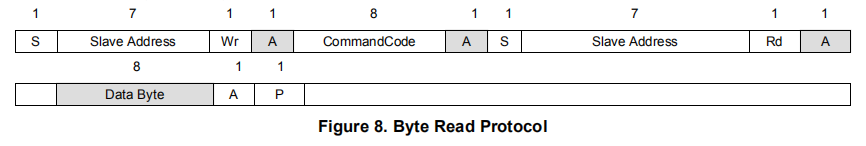

時(shí)鐘驅(qū)動程序串行協(xié)議接受控制器的字節(jié)寫入、字節(jié)讀取、塊寫入和塊讀取操作。

對于塊寫/讀操作,字節(jié)必須按從最低字節(jié)到最高字節(jié)(最高有效位在前)的順序訪問,并能在傳輸完任何完整字節(jié)后停止。對于字節(jié)寫入和字節(jié)讀取操作,系統(tǒng)控制器可以訪問單獨(dú)尋址的字節(jié)。

一旦一個(gè)字節(jié)被發(fā)送出去,它就被寫入內(nèi)部寄存器,并在ACK位的上升沿立即生效。這適用于每個(gè)傳輸?shù)淖止?jié),與這是字節(jié)寫入還是塊寫入序列無關(guān)。

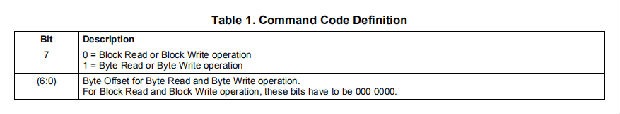

索引字節(jié)的偏移量在命令代碼中編碼,如表1所述。

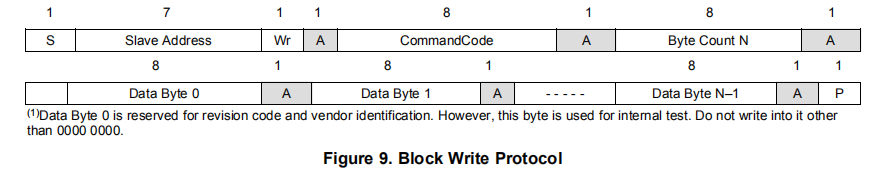

圖9和圖10概述了塊寫入和塊讀取協(xié)議,而圖7和圖8概述了相應(yīng)的字節(jié)寫入和字節(jié)讀取協(xié)議。

從接收器地址(7位)

字節(jié)寫入編程序列

字節(jié)讀取編程序列

塊寫入編程序列(1)

塊讀編程序列

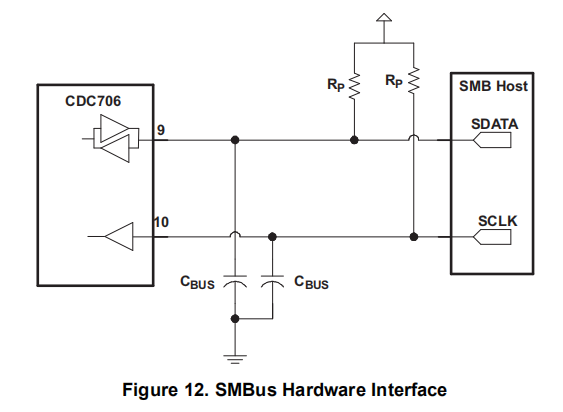

SMBus硬件接口

下圖顯示了CDC706時(shí)鐘合成器如何連接到SMBU。注意,通過上拉電阻器(Rp)的電流必須滿足SMBus規(guī)格(最小100μA,最大350μA)。如果CDC706未連接到SMBus,SDATA和SCLK輸入必須與10 kΩ電阻器連接到VCC,以避免浮動輸入條件。

默認(rèn)設(shè)備設(shè)置

CDC706預(yù)先編程為出廠默認(rèn)配置,如下所示。這將使設(shè)備處于工作模式,而無需先對其進(jìn)行編程。默認(rèn)設(shè)置在通電后或斷電/上電順序后出現(xiàn),直到用戶將其重新編程為不同的應(yīng)用程序配置。通過串行SMBUS接口編程新的寄存器設(shè)置。

可根據(jù)客戶要求編程不同的默認(rèn)設(shè)置。有關(guān)更多信息,請聯(lián)系德州儀器銷售或營銷代表。

輸出頻率可計(jì)算為:

功能描述

時(shí)鐘輸入(時(shí)鐘輸入0和時(shí)鐘輸入1)

CDC706具有兩個(gè)時(shí)鐘輸入,可用作:

•晶體振蕩器輸入(默認(rèn)設(shè)置)

•兩個(gè)獨(dú)立的單端LVCMOS輸入端

•差分信號輸入

專用時(shí)鐘輸入可由字節(jié)11的輸入信號源位[7:6]選擇。

晶體振蕩器輸入

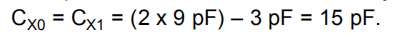

晶體模式的輸入頻率范圍為8mhz~54mhz。CDC706使用皮爾斯型振蕩器電路,其中包含用于反相放大器的反饋電阻。然而,用戶必須添加外部電容器CX0,CX1)以匹配晶體的輸入負(fù)載電容器(參見圖14)。可以計(jì)算所需值:

其中CL是為晶體單元指定的晶體負(fù)載電容器,CICB是設(shè)備的輸入電容,包括板電容(PCB的雜散電容)。

例如,對于CL為9 pF、CICB為4 pF的27 MHz基本晶體,

重要的是要使用從設(shè)備到晶體單元的短PCB軌跡,以保持振蕩器回路的雜散電容最小。

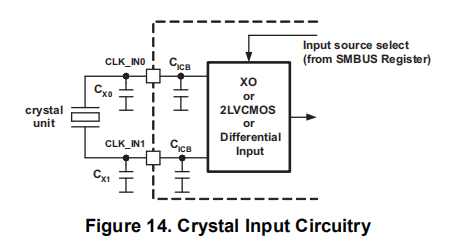

為了保證振蕩的穩(wěn)定,必須施加一定的驅(qū)動功率。CDC706具有自適應(yīng)增益控制的輸入振蕩器,用戶無需手動編程增益。驅(qū)動電平是振蕩晶體單元消耗的功率,通常以諧振器消耗的功率(等效串聯(lián)電阻(ESR))來表示。圖15給出了結(jié)果驅(qū)動電平與晶體頻率和ESR的關(guān)系。

例如,如果使用ESR為50Ω的27 MHz晶體,2 x CL為18 pF,則驅(qū)動功率為21μW。應(yīng)將驅(qū)動電平保持在最小值,以避免過度驅(qū)動晶體。在振蕩器規(guī)范中,為每種類型的晶體規(guī)定了最大功耗,即,對于上述示例,為100μW。

單端LVCMOS時(shí)鐘輸入

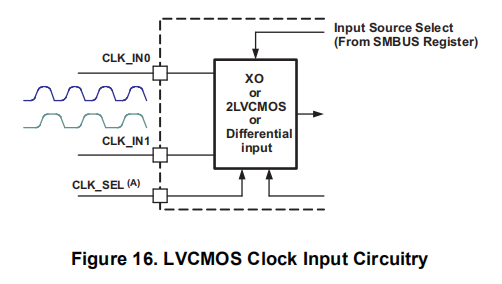

當(dāng)選擇LVCMOS時(shí)鐘模式時(shí),CLK iu IN0和CLK_IN1作為常規(guī)時(shí)鐘輸入引腳,可以驅(qū)動到200兆赫。兩個(gè)時(shí)鐘輸入電路在設(shè)計(jì)上是相等的,可以相互獨(dú)立使用(見圖16)。內(nèi)部時(shí)鐘選擇位字節(jié)10位[4]選擇兩個(gè)輸入時(shí)鐘中的一個(gè)。CLK_IN0是默認(rèn)選擇。也可以選擇將外部控制引腳S0/CLK_SEL編程為時(shí)鐘選擇引腳,字節(jié)10,位[1:0]。

兩個(gè)時(shí)鐘輸入可用于冗余切換,即在主時(shí)鐘和次時(shí)鐘之間切換。注:時(shí)鐘輸入之間的相位差可能需要PLL校正。此外,在主從時(shí)鐘之間的頻率不同的情況下,鎖相環(huán)必須重新鎖定到新的頻率。

A、 CLK_SEL是可選的,可以通過SMBUS設(shè)置進(jìn)行配置。

差分時(shí)鐘輸入

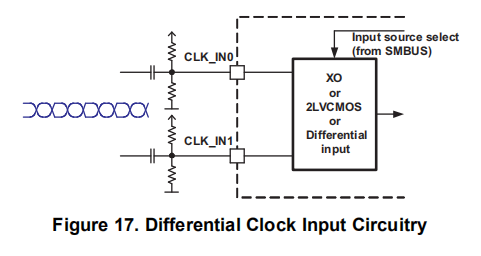

CDC706也支持差分信號。在這種模式下,CLK_IN0和CLK_IN1引腳用作差分信號輸入,可以驅(qū)動到200兆赫。

在200 mV至VCC–0.6的差分共模輸入電壓范圍內(nèi),差分輸入電壓的最小幅值為100 mV。如果應(yīng)用了LVDS或LVPECL信號電平,建議使用交流耦合和偏置結(jié)構(gòu)來調(diào)整不同的物理層(見圖17)。電容器去除信號的直流分量(共模電壓),而交流分量(電壓擺幅)則被傳遞。電阻上拉和/或下拉網(wǎng)絡(luò)表示用于在交流耦合電容器的接收器側(cè)設(shè)置共模電壓的偏置結(jié)構(gòu)。直流耦合也是可能的。

PLL配置和設(shè)置

CDC706包括三個(gè)功能和性能相同的鎖相環(huán)。除了PLL2,它還支持?jǐn)U頻時(shí)鐘(SSC)生成。圖18顯示了鎖相環(huán)的框圖。

所有三個(gè)鎖相環(huán)都是為最簡單的配置而設(shè)計(jì)的。用戶只需分別定義輸入和輸出頻率或分頻器(M,N,P)設(shè)置即可。所有其他參數(shù),如電荷泵電流、濾波器元件、相位裕度或環(huán)路帶寬都由設(shè)備自己控制和設(shè)置。這保證了優(yōu)化的抖動衰減和環(huán)路穩(wěn)定性。

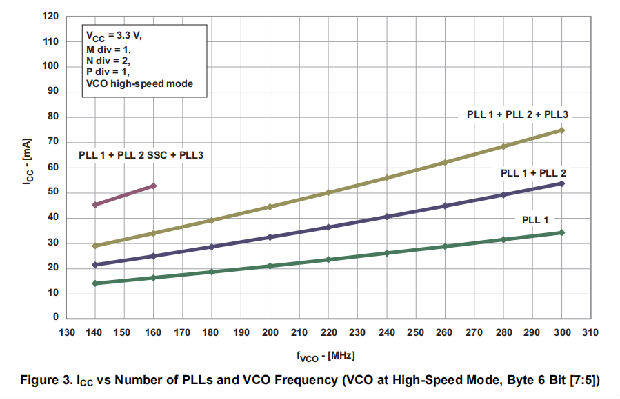

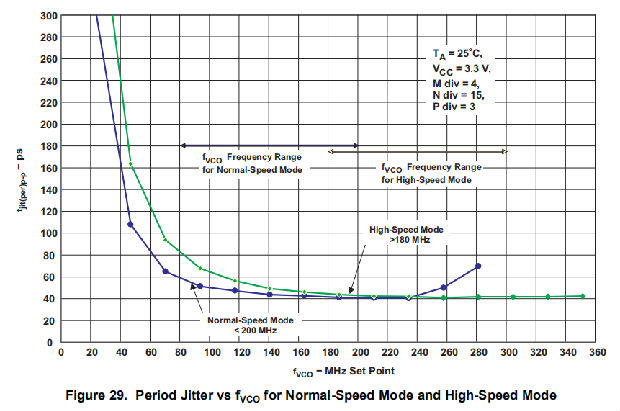

PLL支持正常速度模式(80MHz≤fVCO≤200MHz)和高速模式(180MHz≤fVCO≤300MHz),可由PLLxFVCO選擇(字節(jié)6的位[7:5])。各自的速度選項(xiàng)確保穩(wěn)定的運(yùn)行和最低的抖動。

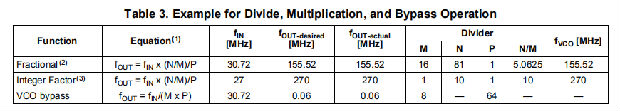

分頻器M和分頻器N在內(nèi)部作為fVCO的分頻器工作,最高可達(dá)250 MHz。這允許分頻比為零ppm輸出時(shí)鐘誤差。

如果fVCO>250 MHz,建議僅使用N/M的整數(shù)因子。

為了獲得最佳的抖動性能,請使分頻器M盡可能小。此外,分?jǐn)?shù)除法器概念要求PLL除法器配置,M≤N(或N/M≥1)。

此外,每個(gè)PLL支持兩個(gè)旁路選項(xiàng):

•PLL旁路和

•VCO旁路

在PLL旁路模式下,PLL完全被旁路,因此輸入時(shí)鐘直接切換到輸出開關(guān)A(字節(jié)9至12的SWAPxx)。在VCO旁路模式下,通過將PLLxMUX設(shè)置為1(字節(jié)3的位[7:5]),只有相應(yīng)PLL的VCO被旁路。但是除法器M仍然可用,并且將輸出除法器擴(kuò)展了額外的9位。這樣就得到了一個(gè)M x P=511 x 127=64897的總分頻器范圍。在VCO旁路模式下,相應(yīng)的PLL塊斷電并使電流消耗最小化。

(1)、計(jì)算中包括輸出開關(guān)矩陣的P除法器。

(2)、fVCO≤250 MHz的分?jǐn)?shù)運(yùn)算。

(3)、fVCO>250 MHz的整數(shù)運(yùn)算。

降低擴(kuò)頻和時(shí)鐘干擾

除了基本的鎖相環(huán)功能外,PLL2還支持?jǐn)U頻時(shí)鐘(SSC)。因此,pll2具有兩個(gè)輸出,SSC輸出和非SSC輸出。兩個(gè)輸出可以并行使用。中心擴(kuò)展SSC調(diào)制信號的平均相位等于非調(diào)制輸入頻率的相位。SSC由輸出開關(guān)A(字節(jié)9至12的SWAPxx)選擇。

SSC也是可旁路的(字節(jié)25,位[6:4]),它關(guān)閉SSC輸出并將其設(shè)置為邏輯低狀態(tài)。PLL2的非SSC輸出不受此模式影響,仍可使用。

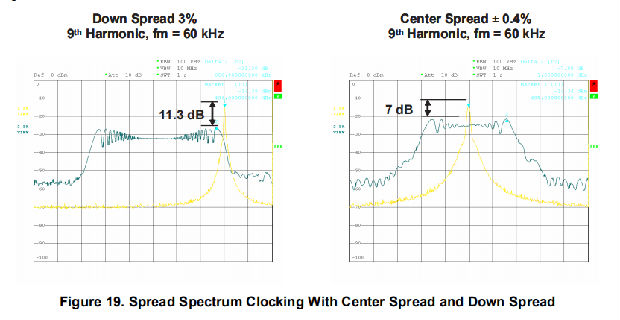

在高速應(yīng)用中,SSC是降低電磁干擾(EMI)噪聲的有效方法。它通過調(diào)制頻率來降低時(shí)鐘信號的射頻能量峰值,并將信號的能量擴(kuò)展到更寬的頻率范圍。因?yàn)闀r(shí)鐘信號的能量保持不變,所以使泛音變寬的頻率必然會降低泛音的振幅。圖19顯示了SSC對DSP 54 MHz時(shí)鐘信號的影響。

調(diào)制時(shí)鐘的峰值幅度比未調(diào)制的載波頻率低11.3db,以減少下擴(kuò)和輻射的電磁能量。

在SSC模式下,用戶可以選擇SSC調(diào)制量和SSC調(diào)制頻率。調(diào)制量是基于載波的頻率偏差(最小/最大頻率),而調(diào)制頻率決定頻率變化的速度。在SSC模式下,最大VCO頻率限制為167 MHz。

SSC調(diào)制量

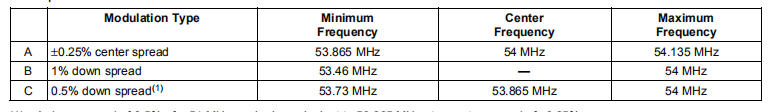

CDC706支持中心擴(kuò)頻和下擴(kuò)調(diào)制。在中心擴(kuò)展中,時(shí)鐘圍繞載波頻率對稱移動,可以是±0.1%、±0.25%和±0.4%。在下擴(kuò)時(shí),時(shí)鐘頻率總是低于載波頻率,可以是1%、1.5%、2%和3%。如果系統(tǒng)不能容忍高于標(biāo)稱頻率的工作頻率(過時(shí)鐘問題),則首選下行擴(kuò)展。

例子:

(1)、54兆赫載波0.5%的下擴(kuò)相當(dāng)于中心擴(kuò)展±0.25%時(shí)的59.865兆赫。

SSC調(diào)制頻率

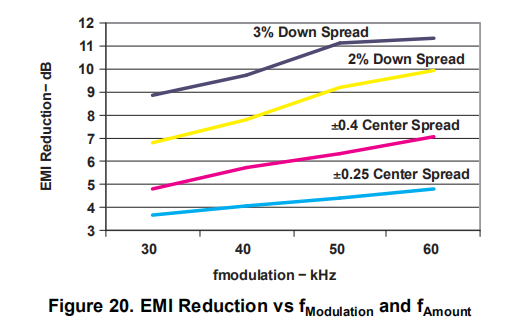

調(diào)制頻率(掃描速率)可在30 kHz和60 kHz之間選擇。它還基于SSC調(diào)制頻率選擇中所示的VCO頻率。如圖20所示,阻尼隨著調(diào)制頻率的增加而增加。它可能受到下游鎖相環(huán)跟蹤偏差的限制。CDC706使用三角形調(diào)制配置文件,這是SSC的常用配置文件之一。

進(jìn)一步降低電磁干擾

最佳阻尼是調(diào)制量、調(diào)制頻率和所考慮的諧波的組合。請注意,由于頻率偏差較大,高次諧波頻率會導(dǎo)致更強(qiáng)的EMI降低。

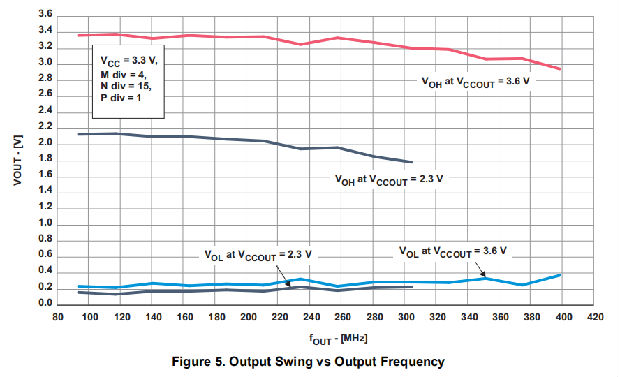

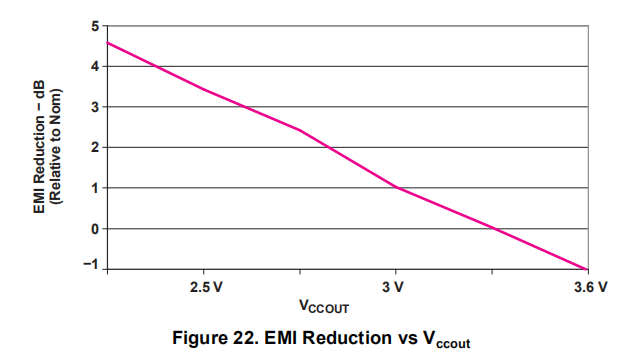

如圖21和圖22所示,較慢的輸出轉(zhuǎn)換率和/或更小的輸出信號幅度有助于更大程度地降低EMI發(fā)射。這兩種措施都降低了時(shí)鐘諧波的射頻能量。CDC706允許在0.6ns到3.3ns(字節(jié)19-24,位[5:4])之間分四步進(jìn)行轉(zhuǎn)換率控制。輸出振幅由兩個(gè)獨(dú)立的輸出電源電壓引腳VCCOUT1和VCCOUT2設(shè)置,范圍從2.3伏到3.6伏不等。即使是低至1.8伏的輸出電源電壓也能工作,但必須考慮最大頻率。

多功能控制輸入S0和S1

CDC706具有兩個(gè)用戶可定義的輸入引腳,可作為外部控制引腳或地址引腳使用。當(dāng)編程為控制引腳時(shí),它們可以作為時(shí)鐘選擇引腳、啟用/禁用引腳或設(shè)備斷電引腳。如果兩個(gè)管腳都用作地址位,則最多可以將四個(gè)設(shè)備連接到同一個(gè)SMBus。各功能在字節(jié)10;位[3:0]中設(shè)置。表4顯示了不同輸出條件、時(shí)鐘選擇和設(shè)備地址的可能設(shè)置。

(1)、非逆變輸出將被設(shè)置為低,逆變輸出將被設(shè)置為高。

(2)、如果S0為0,則選擇CLK_IN0;如果S0為1,則選擇CLK_IN1。

如表4所示,不同的輸出條件有一個(gè)特定的順序:斷電模式覆蓋3狀態(tài),3狀態(tài)覆蓋低狀態(tài),低狀態(tài)覆蓋活動狀態(tài)。

輸出開關(guān)矩陣

輸出開關(guān)矩陣的靈活結(jié)構(gòu)允許用戶通過自由選擇的后分頻器將任何內(nèi)部時(shí)鐘信號源切換到六個(gè)輸出中的任何一個(gè)。

如圖23所示,CDC706基于兩組交換機(jī)和六個(gè)柱式分配器。開關(guān)A包括六個(gè)5輸入MUX,它們選擇四個(gè)PLL時(shí)鐘輸出中的一個(gè),或者直接選擇輸入時(shí)鐘并將其饋送給7位后分頻器(P分頻器)中的一個(gè)。開關(guān)B由6個(gè)6輸入MUX組成,它接受任何后分頻器,并將其饋送給6個(gè)輸出之一Yx。

開關(guān)B被添加到輸出開關(guān)矩陣中,以確保來自一個(gè)P分頻器的輸出頻率100%相位對齊。此外,P-除法器的構(gòu)建方式是每個(gè)除法因子都能自動校正占空比。動態(tài)更改除法器值可能會導(dǎo)致輸出出現(xiàn)故障。

此外,輸出可切換為有源、低或3態(tài)和/或180度相移。輸出轉(zhuǎn)換率和輸出電壓也是用戶可選擇的。

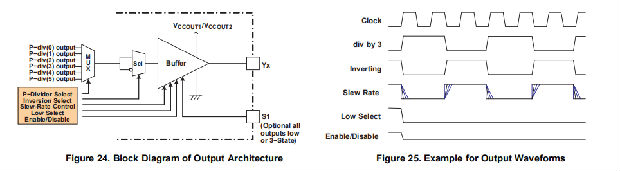

LVCMOS輸出配置

CDC706的輸出級支持所有常見的輸出設(shè)置,例如啟用、禁用、低狀態(tài)和信號反轉(zhuǎn)(180度相移)。它還具有轉(zhuǎn)換速率控制(0.6ns到3.3ns)和可變輸出電源電壓(2.3v到3.6v)。

所有輸出設(shè)置可通過SMBus進(jìn)行編程:

•通過外部控制引腳S0和S1啟用、禁用、低狀態(tài)→字節(jié)10,位[3:0]

•啟用或禁用至低位→字節(jié)19至24,位[3]

•反轉(zhuǎn)/非反轉(zhuǎn)→字節(jié)19至24,位[6]

•轉(zhuǎn)換速率控制→字節(jié)19至24,位[5:4]

•輸出擺動→外部引腳VCCOUT1(引腳14)和VCCOUT2(引腳18)

性能數(shù)據(jù):輸出偏差、抖動、交叉耦合、噪聲抑制(雜散抑制)和相位噪聲

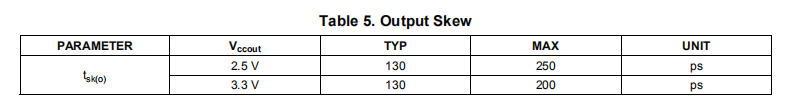

輸出偏差

偏差是時(shí)鐘分布電路的一個(gè)重要參數(shù)。它被定義為由同一輸入時(shí)鐘驅(qū)動的輸出之間的時(shí)間差。表5顯示了CDC706在整個(gè)電源電壓、工作溫度和輸出電壓擺動范圍內(nèi)的高-低和低-高轉(zhuǎn)換的輸出偏差(tsk(o))。

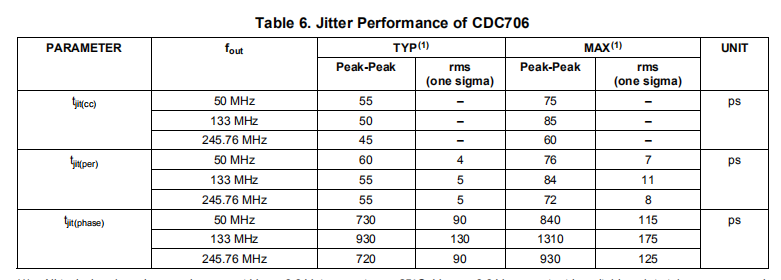

抖動性能

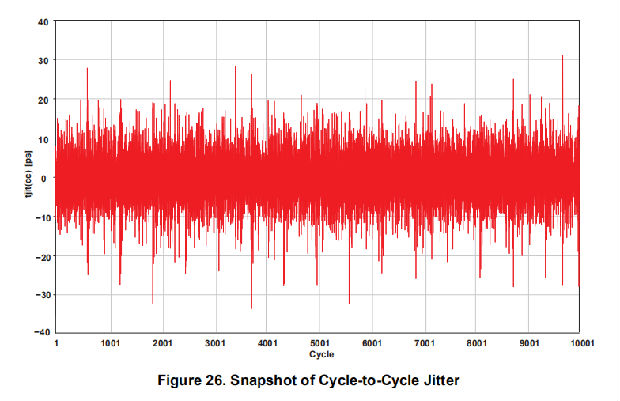

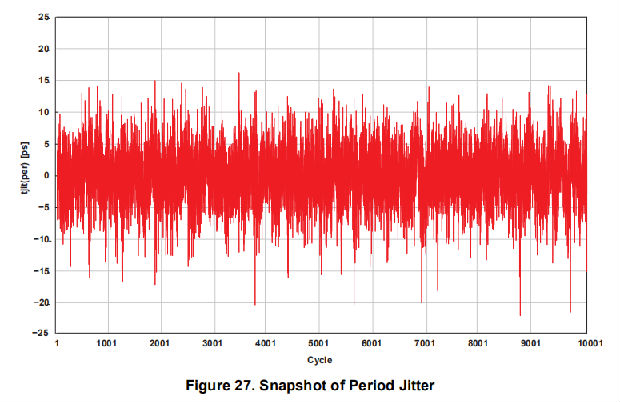

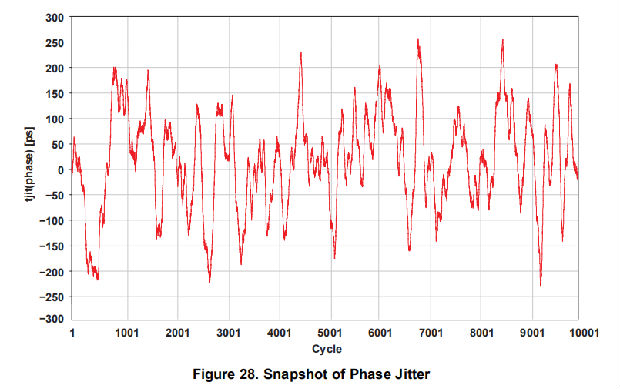

抖動是基于鎖相環(huán)的時(shí)鐘驅(qū)動電路的一個(gè)主要參數(shù)。隨著速度的提高和時(shí)間預(yù)算的減少,這一點(diǎn)變得非常重要。CDC706的鎖相環(huán)和內(nèi)部電路設(shè)計(jì)為最小抖動。峰間周期抖動僅為60ps(典型)。表6給出了表征過程中周期到周期抖動、周期抖動和相位抖動的峰峰值和均方根偏差。

(1)、所有典型值和最大值均為VCC=3.3 V,溫度=25°C,Vccout=3.3 V;一個(gè)輸出為開關(guān),數(shù)據(jù)采集超過10000個(gè)循環(huán)。

圖26、圖27和圖28顯示了10000個(gè)樣本的周期到周期抖動、周期抖動和相位抖動之間的關(guān)系。抖動隨采樣窗口變小或變寬而變化。周期間抖動和周期抖動顯示測量值,而相位抖動是累積的周期抖動。

周期間抖動(tjit(cc))是相鄰周期對的隨機(jī)樣本上相鄰周期之間時(shí)鐘信號周期時(shí)間的變化。周期間抖動永遠(yuǎn)不會大于周期抖動。它也被稱為相鄰周期抖動。

周期抖動(tjit(per))是時(shí)鐘信號在一個(gè)隨機(jī)周期樣本上相對于理想周期(1/fo)的周期時(shí)間偏差。就鎖相環(huán)而言,周期抖動是最壞情況下,與理想情況下鎖相環(huán)輸出的周期偏差。這也被稱為短期抖動。

相位抖動(tjit(相位))是時(shí)鐘信號的長期變化。它是在隨機(jī)循環(huán)樣本中,控制邊相對于t(Θ)平均值的累積偏差。在文獻(xiàn)中,相位抖動、時(shí)間間隔誤差(TIE)或漂移被用來描述頻率的長期變化。在ITU-T:G.810中,漂移被定義為速率小于10hz的相位變化,而抖動被定義為大于10hz的相位變化。測量間隔必須足夠長,以獲得有意義的結(jié)果。漂移可由溫度漂移、老化、電源電壓漂移等引起。

抖動取決于鎖相環(huán)的VCO頻率(fVCO)。與較低的fVCO相比,較高的fVCO會產(chǎn)生更好的抖動性能。壓控振蕩器的頻率可以通過鎖相環(huán)的M和N分頻器來定義。

由于CDC706支持相當(dāng)寬的頻率范圍,該設(shè)備提供了VCO頻率選擇位,即字節(jié)6的位[7:5]。該位定義每個(gè)PLL的抖動優(yōu)化頻率范圍。用戶可以在正常速度模式(80 MHz到200 MHz)和高速模式(180 MHz到300 MHz)之間進(jìn)行選擇。圖29顯示了fVCO在兩個(gè)頻率范圍內(nèi)的抖動性能。

TI-Pro時(shí)鐘軟件自動計(jì)算PLL參數(shù)以優(yōu)化抖動性能。

交叉耦合、雜散抑制和噪聲抑制

集成電路中的交叉耦合是通過芯片的幾個(gè)部分之間的相互作用來實(shí)現(xiàn)的,如輸出級之間、金屬線之間、連接線之間、基板之間等。這種耦合可以是由輸出開關(guān)、泄漏電流、接地彈跳、電源瞬變等引起的電容、電感和電阻(歐姆)耦合。

CDC706采用BiCMOS工藝技術(shù)設(shè)計(jì),采用硅鍺(SiGe)技術(shù)。該工藝具有良好的線性度、低功耗、一流的噪聲性能和非常好的片上元件之間的隔離特性。

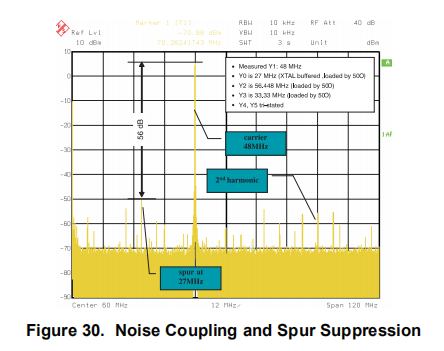

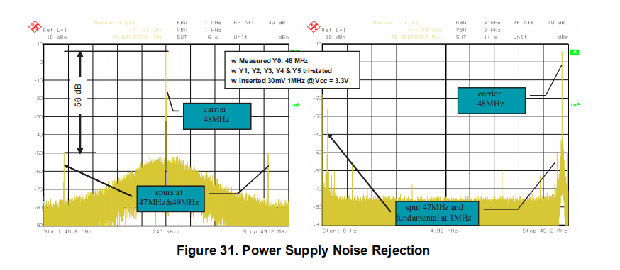

良好的隔離度是使用BiCMOS工藝的一個(gè)主要標(biāo)準(zhǔn),因?yàn)樗梢允柜詈闲?yīng)最小化。即使所有三個(gè)鎖相環(huán)都激活并且所有輸出都打開,噪聲抑制明顯高于50分貝。圖30和圖31顯示了CDC706的噪聲耦合、雜散抑制和電源噪聲抑制的示例。模具各自的測量條件如圖30和圖31所示。

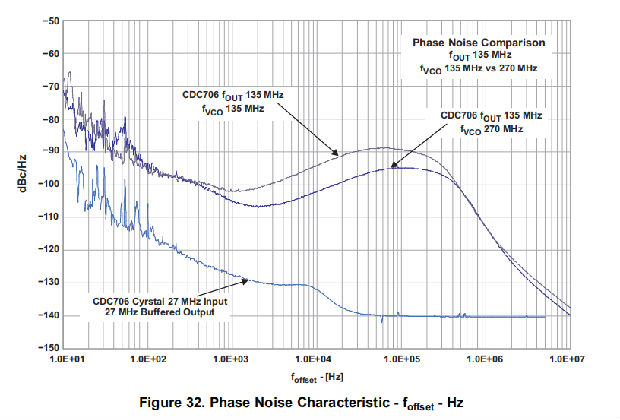

相位噪聲特性

在高速通信系統(tǒng)中,鎖相環(huán)頻率合成器的相位噪聲特性備受關(guān)注。相位噪聲在頻域描述時(shí)鐘信號的穩(wěn)定性,類似于時(shí)域中的抖動規(guī)范。

相位噪聲是隨機(jī)和離散噪聲引起的寬斜率和假峰值的結(jié)果。離散雜散分量可能由信號源中已知的時(shí)鐘頻率、電源線干擾和混頻器產(chǎn)品引起。隨機(jī)噪聲漲落引起的展寬是由相位噪聲引起的。它可能是有源和無源器件中的熱噪聲、散粒噪聲和/或閃爍噪聲的結(jié)果。

鎖相環(huán)頻率合成器的一個(gè)重要因素是環(huán)路帶寬(–3db截止頻率),大的環(huán)路帶寬(LBW)會產(chǎn)生快速的瞬態(tài)響應(yīng),但參考雜散衰減較小。CDC706的LBW約為100khz至250khz,這取決于所選的PLL參數(shù)。

對于CDC706,兩個(gè)相位噪聲特性是令人感興趣的:晶體輸入級的相位噪聲和內(nèi)部鎖相環(huán)(VCO)的相位噪聲。圖32顯示了各自的相位噪聲特性。

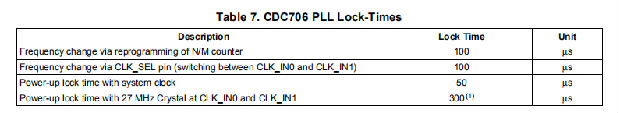

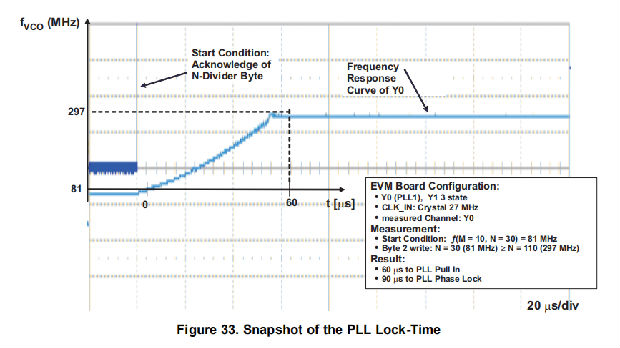

鎖相環(huán)鎖定時(shí)間

有些應(yīng)用使用頻率切換,即在電視應(yīng)用中改變頻率(在頻道之間切換)或在計(jì)算機(jī)中改變PCI-X頻率。鎖相環(huán)在實(shí)現(xiàn)新頻率上所花費(fèi)的時(shí)間是主要的興趣。鎖定時(shí)間是在給定的頻率容差內(nèi)從一個(gè)指定頻率跳到另一個(gè)指定頻率所需的時(shí)間(參見圖33)。它應(yīng)該很低,因?yàn)殚L的鎖定時(shí)間會影響系統(tǒng)的數(shù)據(jù)速率。

PLL鎖定時(shí)間取決于器件配置,并且可以通過VCO頻率來改變,即通過改變M/N分頻器的值。表7給出了CDC706的典型鎖定時(shí)間,圖33顯示了頻率開關(guān)的快照。

(1)、是晶體鎖定時(shí)間(200μs)和PLL鎖定時(shí)間(100μs)的結(jié)果。

電源排序

CDC706包括三個(gè)電源引腳VCC、VCCOUT1和VCCOUT2。由于三個(gè)電源節(jié)點(diǎn)彼此分離,因此沒有電源排序要求。因此,可以以任何順序向三個(gè)節(jié)點(diǎn)供電。

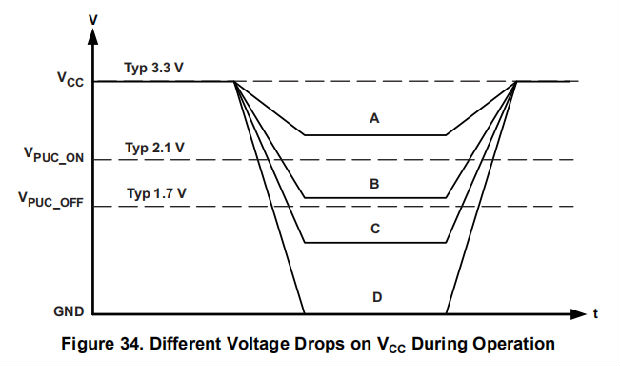

此外,該部件有一個(gè)通電電路,當(dāng)VCC超過2.1 V(典型值)時(shí),該電路會打開設(shè)備;當(dāng)VCC小于1.7 V(典型值)時(shí),該電路會關(guān)閉設(shè)備。在斷電模式下,所有輸出和時(shí)鐘輸入均關(guān)閉。

電源電壓下降時(shí)的設(shè)備行為

CDC706有一個(gè)通電電路,在VPUC_打開時(shí)激活設(shè)備功能(典型2.1 V)。同時(shí),ROM信息被加載到寄存器中。此機(jī)制確保通電后有一個(gè)預(yù)定義的默認(rèn)值,無需在應(yīng)用程序中重新編程CDC706。

在電源電壓下降的情況下,通電電路確保寄存器中始終有一個(gè)定義的設(shè)置。圖34顯示了不同幅度的可能電壓降。

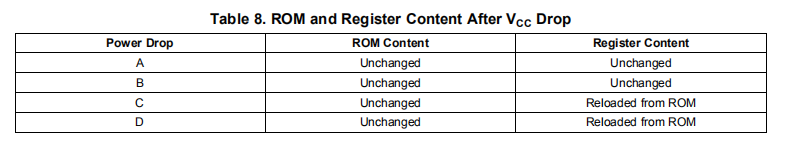

CDC706通電電路有一個(gè)內(nèi)置的遲滯。如果電壓保持在VPUC_OFF以上(通常為1.7 V),寄存器內(nèi)容保持不變。如果電壓降到VPUC U OFF以下,內(nèi)部寄存器在VPUC U ON再次交叉后由ROM重新加載。VPUC_ON通常為2.1V。表8顯示了上述電壓下降后ROM和寄存器的內(nèi)容。

EVM和編程軟件

cdc706evm是一個(gè)開發(fā)工具包,由性能評估模塊、TI-Pro時(shí)鐘軟件和用戶指南組成。更多信息,請聯(lián)系德州儀器銷售或營銷代表。

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國產(chǎn)降成本等解決方案,可承接項(xiàng)目開發(fā),以及元器件一站式采購服務(wù),類型有運(yùn)放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價(jià)格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1