特點

•支持DLP4500 DMD的可靠運行

•兩種類型的輸入接口

–YUV、YCrCb或RGB數(shù)據(jù)格式

–每種顏色8、9或10位

–像素時鐘支持高達150 MHz

-單通道,LVDS平板顯示器(FPD-Link)兼容輸入接口

–支持高達90 MHz有效像素時鐘速率的信號源

–支持8、9、10 YUV、YCrCb或RGB格式輸入的四種解調(diào)像素映射模式

•兩種操作模式

–結(jié)構(gòu)光模式

–像素精確模式,無需視頻處理

–輸入數(shù)據(jù)到微鏡的一對一映射

–高達4225赫茲的1位二進制模式速率

–8位灰度模式速率高達120赫茲

–視頻投影模式

–可編程顏色坐標調(diào)整

–可編程顏色空間轉(zhuǎn)換

–可編程脫氣

–時空復(fù)用(抖動)

•動態(tài)和變形縮放

•支持閃屏顯示

•支持10赫茲到120赫茲的幀速率

•高速、雙數(shù)據(jù)速率DMD接口

•微處理器外圍設(shè)備

–可編程PWM和捕捉定時器

–兩個I2C端口

–一個USB 1.1從端口

–32 kB的內(nèi)部RAM

–專用LED PWM發(fā)生器

•集成時鐘生成電路

–在單個32 MHz晶體上工作

–集成擴頻時鐘

–微處理器并行閃存

•系統(tǒng)控制:

–集成DMD電源和重置駕駛員控制

–DMD水平和垂直圖像翻轉(zhuǎn)

•JTAG邊界掃描測試支持

•419針塑料球柵陣列封裝

應(yīng)用

•機器視覺

•工業(yè)檢驗

•3D掃描

•三維光學(xué)計量

•自動指紋識別

•人臉識別

•增強現(xiàn)實

•交互式顯示

•信息疊加

•光譜學(xué)

•化學(xué)分析儀

•醫(yī)療器械

•光刺激

•虛擬儀表

說明

DLPC350數(shù)字控制器是DLP 0.45 WXGA芯片組的一部分,支持DLP4500 DMD或數(shù)字微鏡設(shè)備的可靠運行。DLPC350控制器在用戶電子設(shè)備和DMD之間提供了一個方便、多功能的接口,支持高速模式速率,為多個輸入分辨率提供LED控制和數(shù)據(jù)格式化。DLPC350還輸出觸發(fā)信號,用于與相機、傳感器或其他外圍設(shè)備同步顯示的模式。

DLPC350控制器能夠?qū)LP 0.45 WXGA芯片組集成到小尺寸和低成本的光轉(zhuǎn)向應(yīng)用中。0.45 WXGA芯片組的應(yīng)用實例包括具有結(jié)構(gòu)光的三維掃描或計量系統(tǒng)、交互式顯示器、化學(xué)分析儀、醫(yī)療儀器和其他需要空間光調(diào)制的終端設(shè)備(光轉(zhuǎn)向和圖形化)。

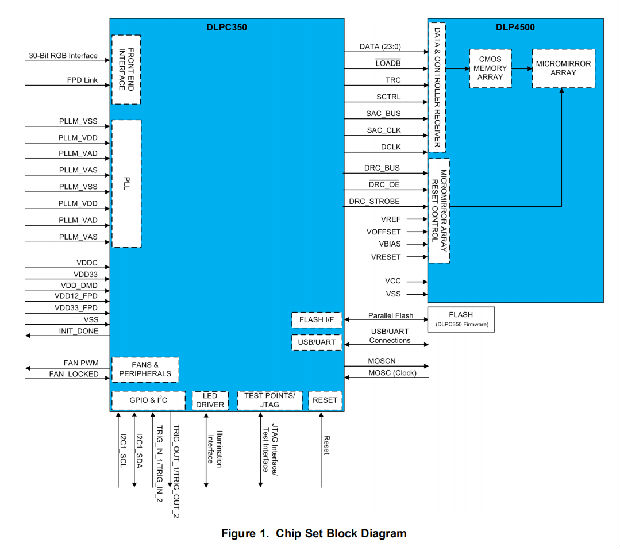

DLPC350是0.45 WXGA芯片組中的兩個設(shè)備之一(見圖1)。另一個設(shè)備是DLP4500 DMD。

方塊圖

在基于DLP的解決方案中,從DLPC350輸入端口到DMD上的圖像的圖像數(shù)據(jù)是100%數(shù)字的。圖像保持數(shù)字形式,不轉(zhuǎn)換為模擬信號。DLPC350處理數(shù)字輸入圖像并將數(shù)據(jù)轉(zhuǎn)換為DLP4500所需的格式。DLP4500通過對每個微鏡使用二進制脈沖寬度調(diào)制(PWM)來控制光線。

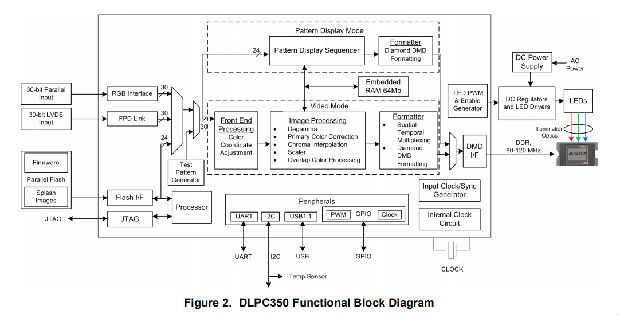

圖2是DLPC350的功能框圖。作為像素處理功能的一部分,DLPC350提供格式轉(zhuǎn)換功能:色度插值和顏色空間轉(zhuǎn)換。DLPC350還提供多種圖像增強功能。DLPC350還支持將輸入數(shù)據(jù)格式化到DMD的必要功能。像素處理功能允許DLPC350和DLP4500支持多種分辨率,包括NTSC、PAL、XGA和WXGA。像素處理功能可以選擇性地繞過本機912×1140像素分辨率,以支持直接的一對一像素映射。

當需要精確的圖案顯示時,本機912 x 1140輸入分辨率圖案與DLP4500上相應(yīng)的微鏡有一對一的關(guān)聯(lián)。DLPC350支持這些圖案的高速顯示。此功能非常適合于結(jié)構(gòu)光、增材制造或數(shù)字曝光等技術(shù)。

命令可以通過I2C接口輸入到DLPC350。

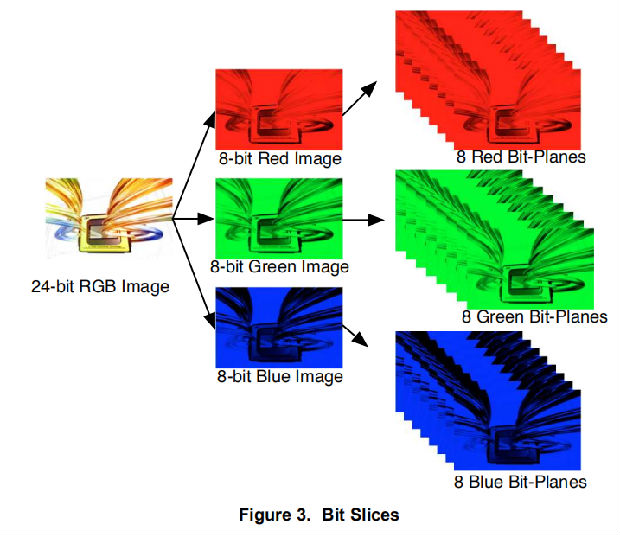

DLPC350以高達120赫茲的幀速率接收24、27或30位RGB數(shù)據(jù)作為輸入。此幀速率由三種顏色(紅色、綠色和藍色)組成,每種顏色在120Hz幀速率中平均分配。因此,每種顏色都分配了2.78ms的時隙。因為每種顏色都有8位、9位或10位深度,所以每個顏色時隙都進一步劃分為位平面。位平面是從全彩色2D圖像的所有像素中提取的一個位的二維排列,以實現(xiàn)動態(tài)深度。見圖3。

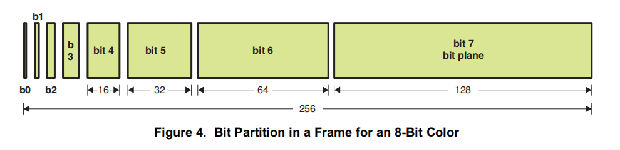

時隙中每個位平面的長度由其二進制表示的相應(yīng)冪加權(quán)。這提供了圖像的二進制脈沖寬度調(diào)制。例如,24位RGB輸入有三種顏色,每種顏色的深度為8位。每個彩色時隙分為8個位平面,該時隙中所有位平面的權(quán)重之和等于256。如圖4所示,請參閱圖4,以了解幀中的位劃分。

因此,單個視頻幀由一系列位平面組成。因為DMD鏡像可以是打開的也可以是關(guān)閉的,所以通過打開與位平面中設(shè)置的位相對應(yīng)的鏡像來創(chuàng)建圖像。在二進制脈沖寬度調(diào)制下,通過控制反射鏡打開的時間量來再現(xiàn)顏色的強度級別。對于輸入到DLPC350的24位RGB幀圖像,DLPC350創(chuàng)建24位平面,將其存儲在嵌入芯片中的雙緩沖eDRAM中,并將其發(fā)送到DLP4500 DMD,一次一個位平面。根據(jù)位平面的位權(quán)重,DLPC350控制該位平面被照亮的時間,控制位平面的強度。為了提高視頻幀中的圖像質(zhì)量,DLPC350采用時空算法對這些位平面、時隙和彩色幀進行混洗和交織。

結(jié)構(gòu)光應(yīng)用

對于不需要這種視頻增強的其他應(yīng)用,可以繞過視頻處理算法并用一組特定的位平面來代替。然后將模式的位深度分配到相應(yīng)的時隙中。此外,輸出觸發(fā)信號也與這些時隙同步以指示何時顯示圖像。對于結(jié)構(gòu)光應(yīng)用,此機制提供了顯示一組圖案并向相機發(fā)送信號以捕捉覆蓋在對象上的這些圖案的功能。

DLPC350在其內(nèi)部內(nèi)存緩沖區(qū)中存儲兩個24位幀。這個48位平面顯示緩沖區(qū)允許DLPC350向DMD陣列發(fā)送一個24位緩沖區(qū),而第二個緩沖區(qū)由閃存填充或通過24位RGB接口流式輸入。在流模式下,DMD數(shù)組顯示前一個24位幀,而當前幀填充顯示緩沖區(qū)的第二個24位幀。一旦顯示了一個24位幀,緩沖區(qū)將旋轉(zhuǎn)訪問下一個24位幀到DMD。因此,顯示的圖像是通過24位RGB并行接口傳輸?shù)臄?shù)據(jù)后面的24位幀。

在結(jié)構(gòu)光模式下,48位平面可以從閃存中預(yù)裝,然后用不同位深度的圖案組合排序。為了使相機與顯示的圖案同步,DLPC350支持三種觸發(fā)模式:模式0、模式1和模式2。

在模式0中,垂直同步用作觸發(fā)輸入。在模式1中,1號觸發(fā)脈沖指示DLPC350進入下一個模式,而2號觸發(fā)器啟動和停止模式序列。在模式0和模式1中,TRIG_OUT_1幀模式的曝光時間,而TRIG_u 2表示模式序列的開始或24位平面的內(nèi)部緩沖區(qū)邊界。在模式2中,觸發(fā)1信號在兩個連續(xù)的模式之間切換,而觸發(fā)脈沖進入下一對模式。

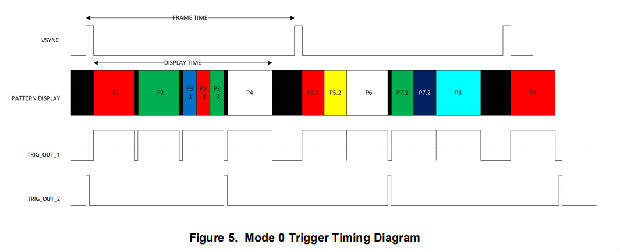

在觸發(fā)器模式0中,如圖5所示,VSYNC啟動模式序列顯示。模式序列由三個連續(xù)的模式組成。第一個模式序列由P1、P2和P3組成。由于P3是一個RGB模式,因此它以P3.1、P3.2和P3.3的時間順序表示來顯示。第二個模式序列由三個模式組成:P4、P5和P6。第三個序列包括P7、P8和P9。TRIG_OUT_1框顯每個模式,而TRIG_OUT_2表示三個模式序列中每個模式的開始。

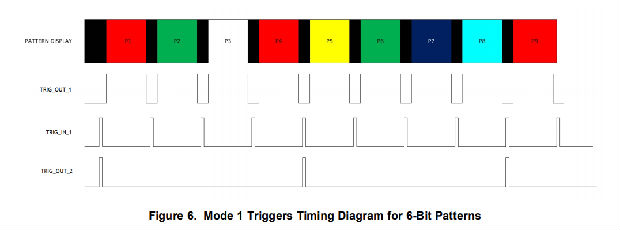

觸發(fā)模式1的示例如圖6所示。顯示四個圖案序列。TRIG_OUT_1框顯每個模式,而TRIG_OUT_2表示每個四個模式序列的開始。觸發(fā)脈沖推進模式。

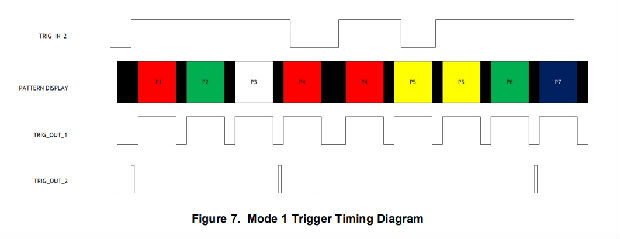

模式1的另一個示例如圖7所示,其中顯示了三個模式序列。TRIG_OUT_1框顯每個顯示的圖案,TRIG_OUT_2表示每個三個圖案序列的開始。_2中的TRIG_用作啟動/停止信號。高時,模式序列開始或繼續(xù)。請注意,在顯示P4模式的中間,_2中的TRIG_低,因此序列停止顯示P4。當觸發(fā)_2中的TRIG_時,模式序列在停止處繼續(xù),重新顯示P4。

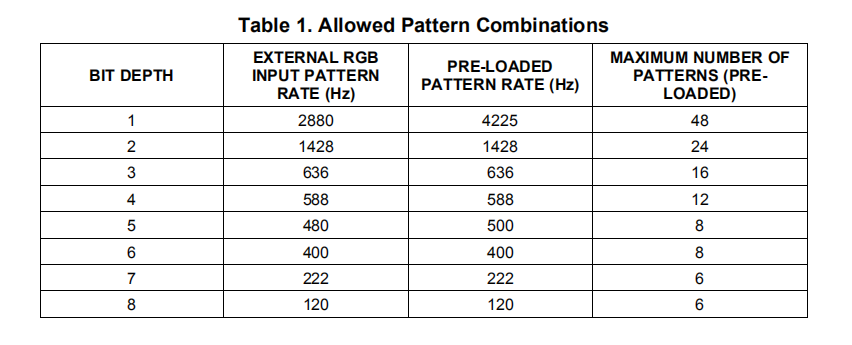

對于觸發(fā)模式2,如圖8所示,TRIG-in-1在兩個模式之間交替,而TRIG-in_-in-2則前進到下一對模式。表1顯示了與模式位深度相關(guān)的允許模式組合。

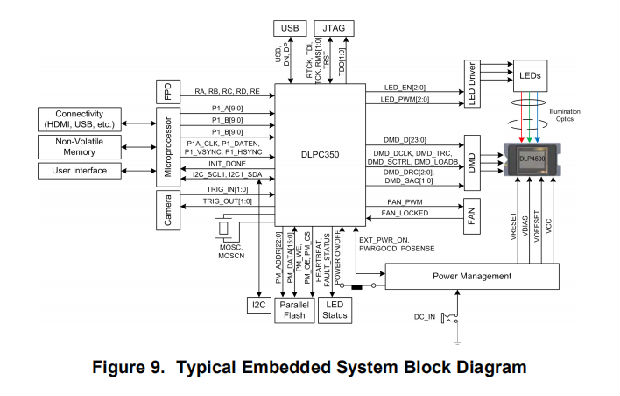

典型系統(tǒng)應(yīng)用

使用DLPC350的典型嵌入式系統(tǒng)應(yīng)用程序如圖9所示。在此配置中,DLPC350控制器支持來自外部源或處理器的24位并行RGB輸入(LCD接口的典型輸入)。該系統(tǒng)同時支持靜態(tài)和動態(tài)視頻源。然而,控制器只支持周期性同步脈沖源。這是運動視頻源的理想選擇,但也可以用于靜態(tài)圖像,方法是保持周期性同步,只在需要時發(fā)送新的數(shù)據(jù)幀。靜止圖像必須完全包含在一個視頻幀中,并且滿足幀定時約束。DLPC350以源幀速率刷新顯示的圖像,并在沒有接收到新幀的間隔內(nèi)重復(fù)上一個活動幀。

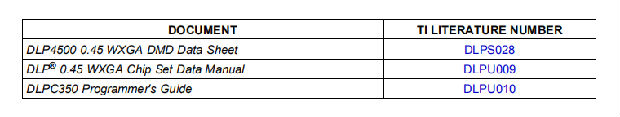

相關(guān)文件

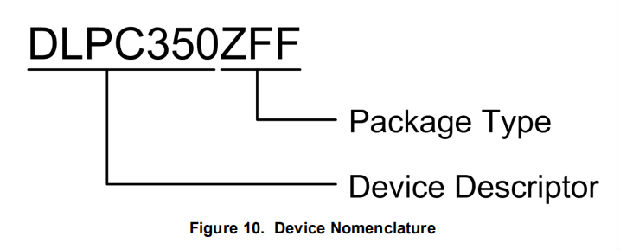

設(shè)備命名法

圖10提供了一個圖例,用于讀取任何DLP設(shè)備的完整設(shè)備名。

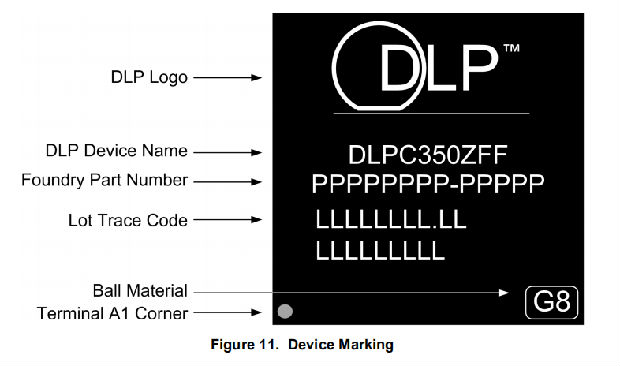

設(shè)備標識

設(shè)備標記由圖11所示的字段組成。

系統(tǒng)通電和復(fù)位

有幾個與系統(tǒng)電源和復(fù)位有關(guān)的因素會影響DLPC350電源引腳的直流誤差(偏移)和交流噪聲。

違約條件

在系統(tǒng)通電時,DLPC350執(zhí)行加電初始化例行程序,該程序?qū)⑹箍刂破髂J為其正常電源模式,相關(guān)時鐘將以其全速啟用,相關(guān)重置將被釋放。大多數(shù)其他時鐘將默認為“禁用”,相關(guān)的重置斷言,直到處理器釋放。這些相同的默認值也將作為所有系統(tǒng)重置事件的一部分應(yīng)用,這些事件發(fā)生時不需要斷開電源或回收電源。

通電或系統(tǒng)重置初始化后,系統(tǒng)將從外部閃存引導(dǎo),之后將啟用其余的控制器時鐘。一旦系統(tǒng)初始化完成,應(yīng)用軟件將決定是否以及何時進入待機模式。

1.2V系統(tǒng)電源

該控制器支持一個低成本的電力輸送系統(tǒng),該系統(tǒng)有一個來自開關(guān)調(diào)節(jié)器的1.2V電源。主核心應(yīng)直接從調(diào)節(jié)器輸出接收1.2V電源,內(nèi)部DLPC350 PLL(VDD U 12_PLLM,VDD_12_PLLD)應(yīng)接收該1.2V電源的單獨過濾版本。具體過濾器建議見PLL。

1.8V系統(tǒng)電源

應(yīng)使用一個1.8V電源為兩個內(nèi)部PLL(VDD U 18 U PLLM,VDD U 18 U PLLD)供電。為了盡可能保持電源清潔,建議通過線性調(diào)節(jié)器獲得該電源,該調(diào)節(jié)器為每個PLL單獨過濾。具體過濾器建議見PLL。

1.9V系統(tǒng)電源

為了最大限度地提高信號完整性,建議使用獨立的線性調(diào)節(jié)器為支持DMD接口(VDD DMD)的1.9V電源供電。為了達到最佳性能,必須嚴格調(diào)節(jié)電源,使其在1.9V±0.1V范圍內(nèi)工作。

3.3V系統(tǒng)電源

DLPC350支持一個低成本的電力輸送系統(tǒng),該系統(tǒng)有一個3.3V電源,來自開關(guān)調(diào)節(jié)器。此3.3V電源將為所有LVCMOS I/O供電。3.3V電源(VDD33)應(yīng)在應(yīng)用1.2V核心電源的所有電源模式下保持激活狀態(tài)。

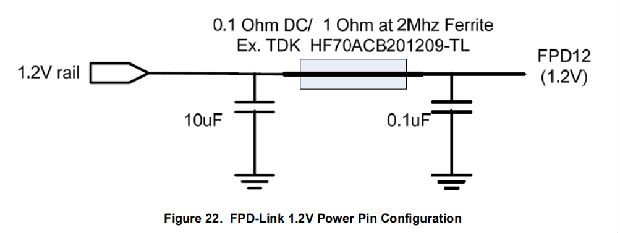

FPD鏈路輸入LVDS系統(tǒng)電源

控制器支持FPD鏈路兼容的LVDS輸入,用于輸入視頻/圖形數(shù)據(jù)以進行顯示的附加方法。此接口有一些與其他控制器1.2V或3.3V電源軌分開的特殊控制器電源考慮事項。FPD Link 1.2V電源引腳配置示例如下所示。

此外,建議將DLF系列電容器與接地端的電阻盡可能低。FPD Link 3.3V電源引腳也應(yīng)采用與1.2V引腳相同的方式使用外部電容器。當不使用FPD鏈路時,可以省略濾波。但是,必須提供相應(yīng)的電壓,以避免潛在的長期可靠性問題。

系統(tǒng)通電/斷電順序

盡管DLPC350需要一系列電源電壓(例如VDDC、VDD U 1X U PLLX、VCC U 18、VCC U DMD、VCCXX_FPD),但對于電源排序的相對順序沒有任何限制,以避免損壞DLPC350。上電和斷電都是如此。同樣,DLPC350的不同電源的通電或斷電之間沒有最短時間。但是,請注意,對于與DLPC350共享電源的其他設(shè)備,存在電源排序要求的情況并不少見。

雖然給定的電源順序不會導(dǎo)致DLPC350損壞,但從功能角度來看,仍有一些特定的電源順序建議,以確保正常運行。

•無論何時應(yīng)用I/O電源,都應(yīng)使用1.2V核心電源。這可確保通電I/O引腳設(shè)置為已知狀態(tài)。因此,建議先使用核心電源。其他電源應(yīng)僅在1.2V DLPC350核心已提升后使用。

•所有控制器電源應(yīng)在POSENSE被斷言之前接通,以確保正確執(zhí)行加電初始化。1.8V PLL電源、1.9V I/O電源和3.3V I/O電源應(yīng)保持不變,只要使用1.2V核心電源和POSENSE。

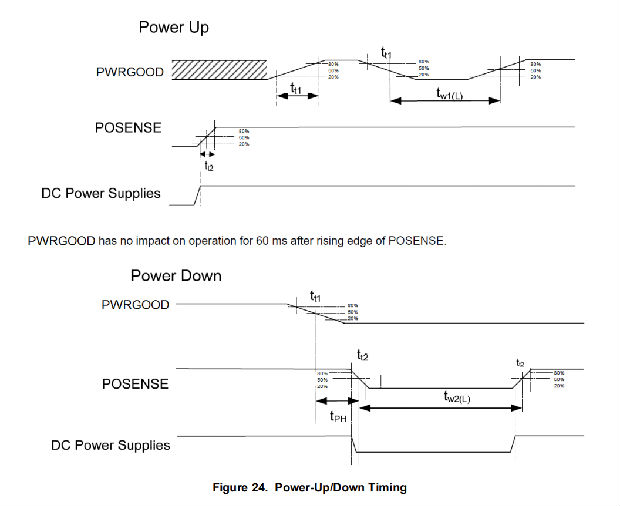

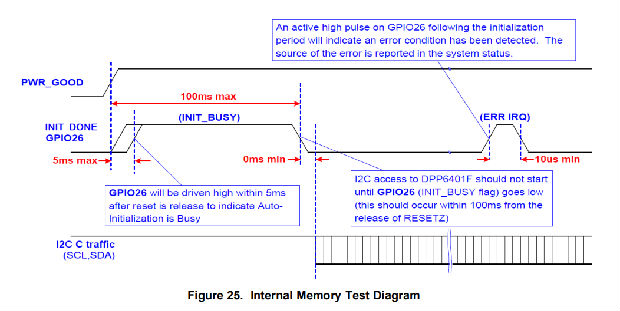

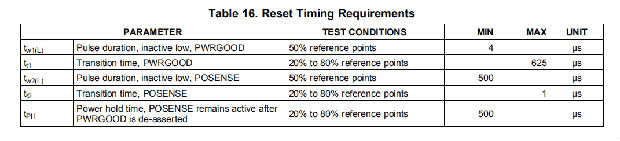

假設(shè)所有DLPC350加電順序都由外部硬件處理。還假設(shè)外部電源監(jiān)視器將在通電期間保持系統(tǒng)內(nèi)DLPC350復(fù)位(itaht為,POSENSE=0)。它應(yīng)繼續(xù)斷言系統(tǒng)重置,直到所有DLPC350電壓達到最低指定電壓水平。在此期間,所有控制器I/O將為三態(tài)或低驅(qū)動。當POSENSE從低到高轉(zhuǎn)換時,主PLL(PLLM)將從重置中釋放,但DLPC350將使控制器的其余部分保持重置100毫秒,以允許PLL鎖定并穩(wěn)定其輸出。在這100毫秒的延遲之后,內(nèi)部重置將被取消斷言,從而使微處理器開始其啟動程序。

開機感應(yīng)(POSENSE)支持

在DLPC350最小電源電壓規(guī)格下,很難設(shè)置一個電源監(jiān)控器來精確跳閘。因此,建議生成POSENSE的外部電源監(jiān)控器將其閾值設(shè)定為最小電源電壓的90%,并確保POSENSE在足夠長的時間內(nèi)保持低電壓,以允許所有電源電壓達到最低控制器要求并穩(wěn)定。注意,用于檢測功率損失的跳閘電壓對POSENSE來說并不重要,因此可能低至額定電源電壓的50%。此外,對于POSENSE來說,響應(yīng)低電壓條件的反應(yīng)時間并不重要。INIT_DONE在這些方面有更重要的要求。

電源良好(PWRGOOD)支持

PWRGOOD信號被定義為一個早期警告信號,在直流電源電壓降到低于規(guī)格值之前,應(yīng)向控制器發(fā)出500微秒的警報。這使得控制器有時間停駐DMD,確保未來操作的完整性。建議在電源調(diào)節(jié)器的輸入側(cè)安裝監(jiān)控感應(yīng)電源。

5V容差支持

除USB數(shù)據(jù)外,DLPC350不支持任何其他5V容限I/O。

電源復(fù)位操作

在加電事件之后,DLPC350硬件將自動啟動主PLL并將控制器置于正常電源模式。然后,它將遵循標準系統(tǒng)重置程序(見下一節(jié))。

系統(tǒng)復(fù)位操作

在任何類型的系統(tǒng)重置(加電重置、PWRGOOD重置等)之后,DLPC350將自動返回到正常電源模式并返回到以下狀態(tài):

•所有GPIO將為三態(tài),因此,所有GPIO控制的電壓開關(guān)將默認啟用所有DLPC350電源線的電源(假設(shè)這些輸出被外部拉高)。

•主PLL將保持激活狀態(tài)(僅在通電復(fù)位時重置),大多數(shù)衍生時鐘將激活。但是,只有與內(nèi)部處理器及其外圍設(shè)備相關(guān)聯(lián)的重置才會被釋放。

•當以全速啟動時,內(nèi)部處理器相關(guān)時鐘將默認為全時鐘速率)。

•為DDR DMD接口(PLLD)供電的PLL將默認為其斷電模式,并且所有派生時鐘都將處于非活動狀態(tài),并斷言相應(yīng)的重置。

•DMD接口(除DMD_DRC_OE)將其輸出默認為邏輯低狀態(tài)。DMD_DRC_OE將默認為三態(tài),但應(yīng)通過PCB上的外部30KΩ至51KΩ的上拉電阻器拉高。

•DLPC350輸出的所有重置將保持斷言,直到內(nèi)部處理器釋放(啟動后)。

•DLPC350將從外部閃存啟動。DLPC350啟動后,它將:

–配置可編程DDR時鐘發(fā)生器(DCG)時鐘速率(即DMD LPDDR接口速率)。

–啟用DCG PLL(PLLD),同時保持分頻器邏輯復(fù)位。

–一旦DCG PLL鎖定,固件將設(shè)置DMD時鐘速率。

–DLPC350固件隨后將釋放DCG除法器邏輯重置,這反過來將啟用所有派生的DCG時鐘。

•配置時鐘后,執(zhí)行內(nèi)部存儲器測試。請參見圖25并注意GPIO26是INIT_DONE信號。

應(yīng)用軟件應(yīng)該等待用戶發(fā)出喚醒命令。一旦控制器被請求“喚醒”,軟件應(yīng)將控制器置于正常模式,并根據(jù)需要重新初始化時鐘和重置。

PCB一般建議

CMOS型引腳的一般處理指南

為了避免浮動CMOS只輸入管腳所引起的潛在損壞電流,建議將未使用的輸入管腳通過上拉電阻器連接到相關(guān)電源或下拉接地。對于帶有內(nèi)部上拉或下拉電阻器的輸入,除非特別推薦,否則無需添加外部上拉或下拉電阻。注意,內(nèi)部上拉和下拉電阻很弱,不應(yīng)期望驅(qū)動外部線路。

雙向管腳被配置為重置默認值的輸入。

除非特別規(guī)定,上拉和下拉電阻可為10 kΩ。

未使用的僅輸出引腳可以保持打開狀態(tài)。

程序存儲器閃存接口

DLPC350提供兩個外部程序存儲器芯片選擇。

•PM_CS_1-啟動閃存設(shè)備的強制CS(標準“NOR”閃存≤128 Mb)

•PM_CS_2-可用于可選閃存設(shè)備(≤128 Mb)

閃存訪問定時由軟件編程,最多可編程31個等待狀態(tài)。等待狀態(tài)分辨率在正常模式下為6.7納秒,在低功耗模式下為53.57納秒。計算等待狀態(tài)值:等待狀態(tài)值=設(shè)備訪問時間÷等待狀態(tài)解析

其中等待狀態(tài)值向上取整。該方程假定最大單向跡線長度為75mm。當其他設(shè)備(如附加閃存)與引導(dǎo)閃存一起使用時,存根長度必須保持較短,并盡可能靠近路徑的閃存端。

DLPC350提供足夠的程序內(nèi)存地址引腳,以支持高達128 Mb的閃存設(shè)備。有兩個雙向管腳(PM_ADDR_22和PM_ADDR_21),一旦軟件對它們進行配置,就可以將它們編程為附加地址管腳。啟用PM_ADDR_21會將閃存大小從32 Mb增加到64 Mb。啟用PM_ADDR_22和PM_ADDR_21會將閃存大小增加到128 Mb。如果使用這些引腳,那么它們需要板級下拉電阻,以防止閃存地址位浮動。

熱因素

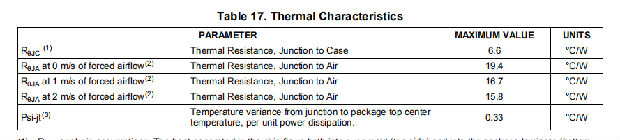

DLPC350的基本熱限制是不得超過最高工作結(jié)溫度(TJ)(參見推薦的工作條件)。該溫度取決于工作環(huán)境溫度、氣流、PCB設(shè)計(包括元件布局密度和所用銅量)、DLPC350的功耗以及周圍元件的功耗。DLPC350封裝的主要目的是通過PCB的電源和接地平面吸熱,因此PCB上的銅含量和氣流是重要因素。

(1)、RθJC分析假設(shè):芯片中產(chǎn)生的熱量既流入過模(頂面)又流入封裝層壓板(底面),然后通過封裝焊料球流入PCB。這只能用于散熱器分析。

(2)、熱系數(shù)符合JEDEC標準51。RθJA是使用JEDEC定義的標準測試PCB測量的封裝的熱阻。此JEDEC測試PCB不一定代表DLPC350 PCB,因此報告的熱阻在實際產(chǎn)品應(yīng)用中可能不準確。雖然實際的熱阻可能不同,但在設(shè)計階段,這是評估熱性能的最佳信息。

(3)、示例:(3 W)x(0.33°C/W)=大約1.00°C溫升。

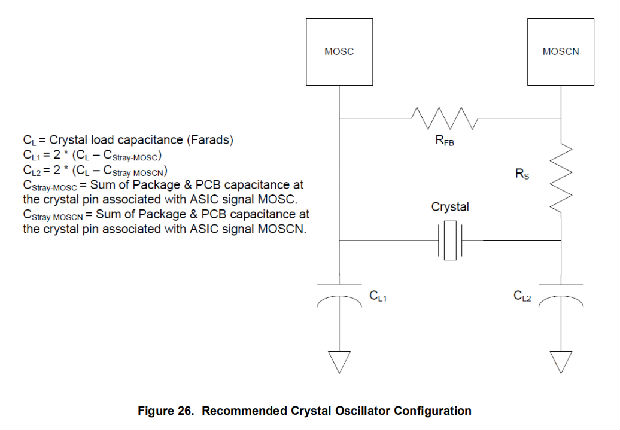

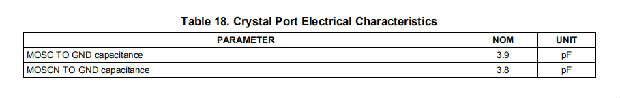

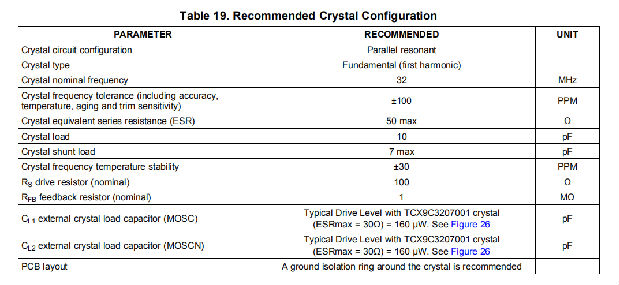

推薦的MOSC晶體振蕩器配置

DLPC350需要一個外部參考時鐘為其內(nèi)部PLL供電。該基準可以通過晶體或振蕩器提供。DLPC350接受32 MHz的參考時鐘,最大頻率變化為100 ppm(包括老化、溫度和微調(diào)元件變化)。當使用晶體時,還需要幾個分立元件,如圖26所示。

如果使用外部振蕩器,則振蕩器輸出必須驅(qū)動DLPC350控制器上的MOSC引腳,且MOSCN引腳應(yīng)保持未連接狀態(tài)。振蕩器的好處是它可以提供一個擴頻時鐘來降低EMI。但是請注意,DLPC350只能接受0%,±0.5%和±1.0%(中心擴展調(diào)制)和三角形波形。

與晶體選項類似,振蕩器輸入頻率限制為32兆赫。

假設(shè)外加穩(wěn)定功率后,外部晶體或振蕩器在50 ms內(nèi)穩(wěn)定。

鎖相環(huán)

建議采用以下指南,以獲得相對于內(nèi)部鎖相環(huán)的理想控制器性能。

DLPC350包含兩個PLL(PLLM和PLLD),每個PLL都有專用的1.2V數(shù)字和1.8V模擬電源。這些1.2V PLL引腳應(yīng)通過鐵氧體磁珠與主1.2V系統(tǒng)電源單獨隔離。鐵氧體磁珠的阻抗應(yīng)遠大于電容器在預(yù)期噪聲頻率下的阻抗。鐵氧體磁珠的阻抗在100-300KHz的頻率范圍內(nèi)必須小于0.5Ω,在頻率大于100MHz時,阻抗必須大于10Ω。

作為最低要求,1.8V模擬PLL電源和接地引腳應(yīng)使用LC濾波器隔離,鐵氧體磁珠用作電感器,0.1μF電容器位于鐵氧體磁珠的DLPC350側(cè)。建議1.8V PLL電源由專用線性調(diào)節(jié)器供電,每個PLL應(yīng)單獨與調(diào)節(jié)器隔離。1.8V模擬PLL電源的相同F(xiàn)erreid建議適用于1.2V數(shù)字PLL電源。

在描述整個供應(yīng)過濾網(wǎng)絡(luò)時,必須注意確保不會發(fā)生共振。在1-2MHz頻段必須特別小心,因為這與PLL自然環(huán)路頻率一致。

1.2V和1.8V PLL電源都需要高頻去耦,并且應(yīng)盡可能靠近每個PLL電源包引腳。建議將去耦電容器放在電路板另一側(cè)的封裝下方。應(yīng)使用高質(zhì)量、低ESR、單片、表面貼裝電容器。每個PLL電源通常為0.1μF。連接跡線的長度增加了安裝的寄生電感,因此,在可能的情況下,不應(yīng)存在任何跡線,從而允許通孔與焊盤本身對接。此外,連接部分應(yīng)盡可能寬。進一步的改進可以通過在電容器的邊上放置過孔或使過孔數(shù)量加倍來實現(xiàn)。

整體解耦的位置取決于系統(tǒng)設(shè)計。通常,10μF范圍內(nèi)的良好陶瓷電容器就足夠了。

板級測試支持

電路內(nèi)三態(tài)使能信號(ICTSEN)是板級測試控制信號。通過驅(qū)動ICTSEN到邏輯高電平狀態(tài),所有控制器輸出(TDO1除外)將為3態(tài)。

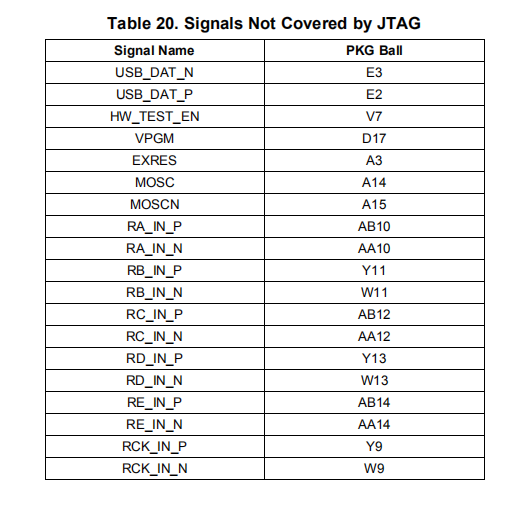

DLPC350還為所有I/O信號、非數(shù)字I/O和一些特殊信號提供JTAG邊界掃描支持。下表定義了這些例外情況。

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍牙WIFI模組、進口芯片替換國產(chǎn)降成本等解決方案,可承接項目開發(fā),以及元器件一站式采購服務(wù),類型有運放芯片、電源芯片、MO芯片、藍牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1