特點(diǎn)

•適合汽車應(yīng)用

•相對(duì)精度(INL):±0.35 LSB

•超低故障能量:0.1 nV-s

•低功率運(yùn)行:2.7 V時(shí)為100μA

•上電復(fù)位至零刻度

•電源:2.7-5.5-V單電源

•斷電:2.7 V時(shí)為0.05μA

•12位線性度和單調(diào)性

•軌間電壓輸出

•沉降時(shí)間:5μs(最大)

•SPI兼容串行接口,帶施密特觸發(fā)器輸入:最高50 MHz

•菊花鏈功能•異步硬件清晰到零刻度

•規(guī)定溫度范圍:–40°C至+105°C

•小型,2-mm×3-mm,12引線USON封裝

•Z-Suffix提供改進(jìn)的分層

應(yīng)用

•便攜式電池供電儀器

•數(shù)字增益和偏移調(diào)整

•可編程電壓和電流源

•可編程衰減器

•工業(yè)過(guò)程控制

•ADAS雷達(dá)應(yīng)用

•碰撞警告

•盲點(diǎn)檢測(cè)

說(shuō)明

DAC7551-Q1器件是一種單通道、電壓輸出的數(shù)模轉(zhuǎn)換器(DAC),具有卓越的線性度和單調(diào)性,以及將故障能量最小化的專有結(jié)構(gòu)。低功耗DAC7551-Q1設(shè)備可從單個(gè)2.7伏到5.5伏電源供電。DAC7551-Q1輸出放大器可驅(qū)動(dòng)2-kΩ、200 pF的軌對(duì)軌負(fù)載,穩(wěn)定時(shí)間為5μs。輸出范圍使用外部參考電壓設(shè)置。

3線串行接口以高達(dá)50兆赫的時(shí)鐘頻率工作,并與SPI兼容™,QSPI™、microwire和DSP接口標(biāo)準(zhǔn)。該設(shè)備包含一個(gè)加電復(fù)位(POR)電路,以確保DAC輸出功率高達(dá)0 V,并保持在該電壓下,直到對(duì)該設(shè)備進(jìn)行有效的寫入循環(huán)。該設(shè)備具有斷電功能,可將設(shè)備的電流消耗降低到2μa以下。

DAC7551-Q1設(shè)備體積小、功耗低,非常適合電池操作的便攜式應(yīng)用。5v時(shí)的功耗通常為0.5mw,3v時(shí)為0.23mw,在斷電模式下功耗降低到1μW。

DAC7551-Q1設(shè)備采用12針USON封裝,規(guī)定溫度為-40°C至+105°C。與標(biāo)準(zhǔn)設(shè)備相比,Z后綴可減少分層。

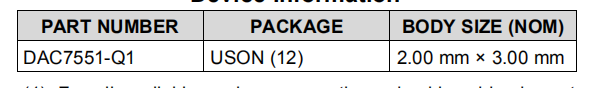

設(shè)備信息

(1)、有關(guān)所有可用的軟件包,請(qǐng)參閱數(shù)據(jù)表末尾的訂購(gòu)附錄。

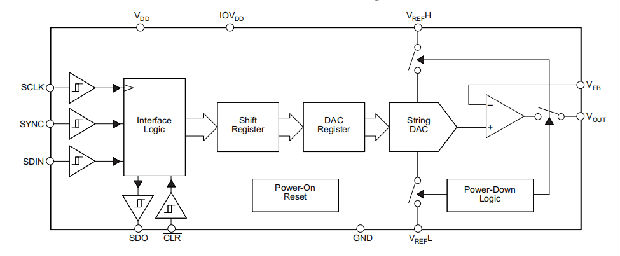

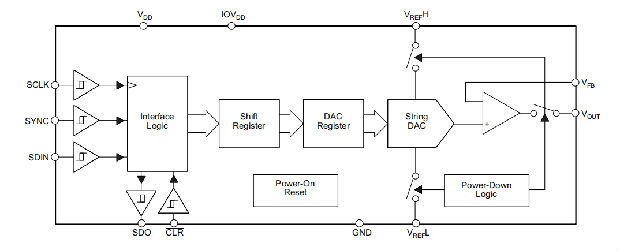

功能框圖

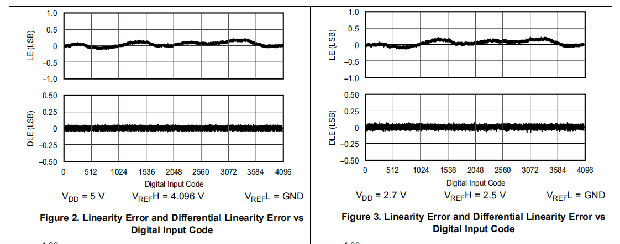

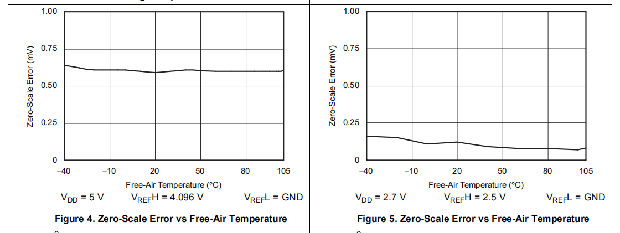

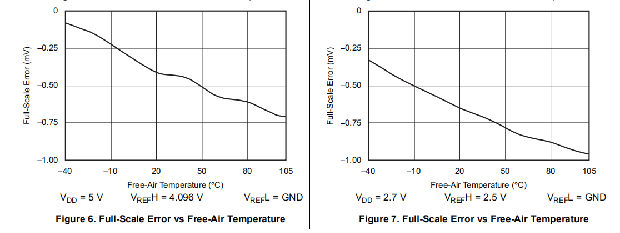

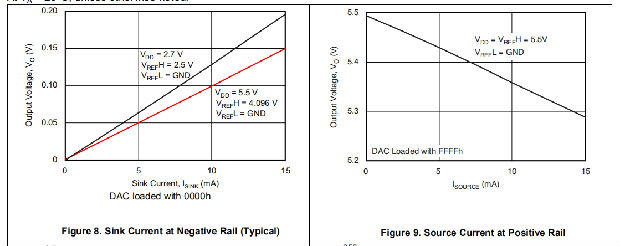

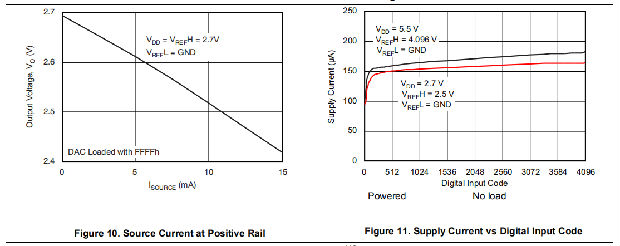

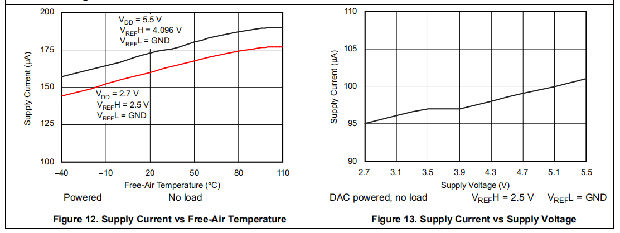

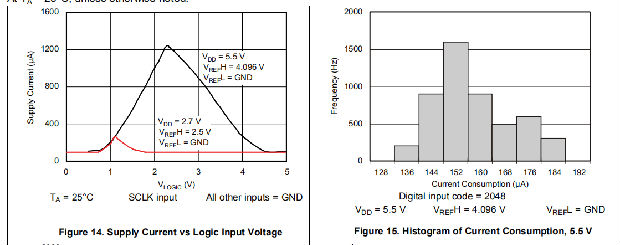

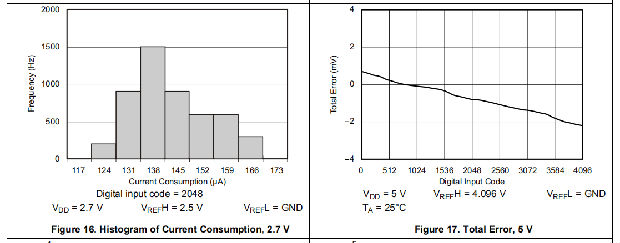

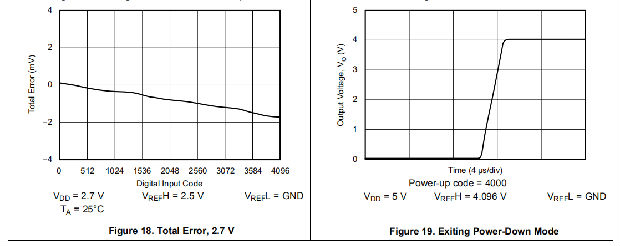

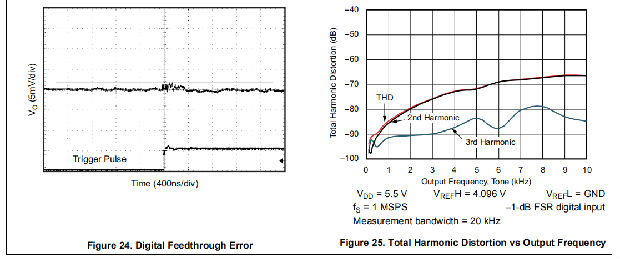

典型特征

TA=25°C時(shí),除非另有說(shuō)明。

詳細(xì)說(shuō)明

概述

DAC7551-Q1設(shè)備是一個(gè)12位電阻串?dāng)?shù)模轉(zhuǎn)換器(DAC)。無(wú)緩沖外部參考輸入允許正電壓參考低至0.25 V,高達(dá)VDD。放大器反饋輸入在負(fù)載點(diǎn)有更好的直流精度。該設(shè)備通過(guò)16位字三線串行外圍接口(SPI)控制,最高可達(dá)50兆赫,并可選擇菊花鏈多個(gè)設(shè)備。異步清除功能和斷電功能允許軟件控制復(fù)位和低功耗。一個(gè)獨(dú)立的邏輯電源輸入意味著該設(shè)備可以在廣泛的電源電壓范圍內(nèi)與不同的邏輯系列一起使用。

功能框圖

特性描述

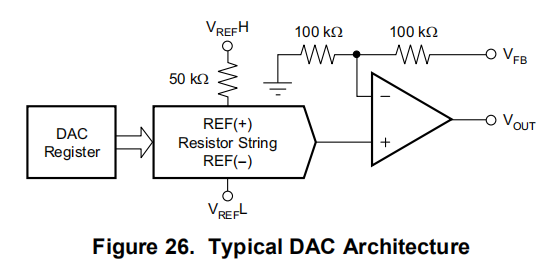

數(shù)模轉(zhuǎn)換器

DAC7551-Q1器件的結(jié)構(gòu)由一個(gè)串DAC和一個(gè)輸出緩沖放大器組成。圖26顯示了DAC體系結(jié)構(gòu)的通用框圖。

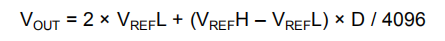

DAC7551-Q1器件的輸入編碼是無(wú)符號(hào)二進(jìn)制,它給出了理想的輸出電壓,如等式1所示。

其中:

•D是加載到DAC寄存器的二進(jìn)制代碼的十進(jìn)制等效值,范圍從0到4095。

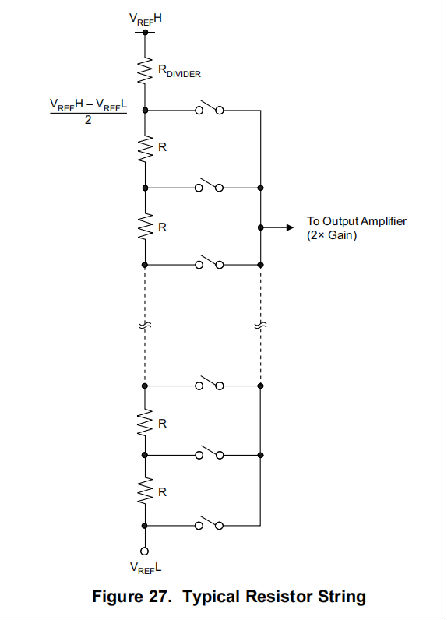

電阻串

圖27顯示了電阻串部分。這個(gè)部分只是一個(gè)電阻串,每個(gè)電阻值為R。加載到DAC寄存器的數(shù)字代碼決定在串上的哪個(gè)節(jié)點(diǎn)上,電壓被分接到輸出放大器中。通過(guò)關(guān)閉一個(gè)連接到放大器的開關(guān),電壓被分接。DAC的輸出是單調(diào)的,因?yàn)樗且淮娮琛?/p>

輸出緩沖放大器

輸出緩沖放大器能夠在輸出端產(chǎn)生軌對(duì)軌電壓,提供0 V到VDD的輸出范圍。該放大器能夠驅(qū)動(dòng)2kΩ的負(fù)載,并對(duì)地高達(dá)1000pf。圖8、圖9和圖10顯示了輸出放大器的匯和源能力。在輸出空載的情況下,轉(zhuǎn)換速率為1.8v/μs,半刻度穩(wěn)定時(shí)間為3μs。

DAC外部參考輸入

DAC7551-Q1設(shè)備包含無(wú)緩沖的VREFH和VREFL參考輸入。VREFH參考電壓可低至0.25V,高達(dá)VDD,因?yàn)闆](méi)有任何參考放大器的凈空和腳部空間限制。

建議在外部電路中使用緩沖基準(zhǔn)(例如,REF3140裝置)。輸入阻抗通常為100kΩ。

放大器檢測(cè)輸入

DAC7551-Q1設(shè)備包含一個(gè)放大器反饋輸入引腳VFB。對(duì)于電壓輸出操作,VFB必須外部連接到VOUT。對(duì)于直流點(diǎn),應(yīng)作更準(zhǔn)確的直流連接。VFB引腳也適用于各種應(yīng)用,包括數(shù)字控制的電流源。反饋輸入引腳通過(guò)100-kΩ電阻器內(nèi)部連接到DAC放大器負(fù)極輸入端子。放大器負(fù)極輸入端子通過(guò)另一個(gè)100-kΩ電阻器內(nèi)部接地(見圖26)。這些連接形成了一個(gè)增益為2的非互易放大器配置。總增益保持為1,因?yàn)殡娮璐谐?的配置。在VFB針腳處看到的接地電阻約為200 kΩ。

上電復(fù)位

通電時(shí),清除所有寄存器,并用零標(biāo)度電壓更新DAC信道。在寫入有效數(shù)據(jù)之前,DAC輸出保持此狀態(tài)。此設(shè)置在設(shè)備通電時(shí)了解DAC輸出狀態(tài)非常重要的應(yīng)用程序中特別有用。為避免開啟ESD保護(hù)裝置,應(yīng)在任何其他引腳(如VREFH)升高之前應(yīng)用VDD和IOVDD。VDD和IOVDD的加電順序無(wú)關(guān)。因此,IOVDD可以在VDD之前提出,或者反過(guò)來(lái)。

斷電

DAC7551-Q1設(shè)備具有靈活的斷電功能。在斷電狀態(tài)下,用戶可以靈活地選擇DAC的輸出阻抗。在斷電操作期間,DAC可以具有1kΩ、100kΩ或Hi-Z輸出對(duì)地阻抗。

異步清除

在CLR引腳降低后,DAC7551-Q1輸出立即異步設(shè)置為零標(biāo)度電壓。CLR信號(hào)重置所有內(nèi)部寄存器,因此其功能類似于上電復(fù)位。DAC7551-Q1設(shè)備在同步信號(hào)的第一個(gè)上升沿進(jìn)行更新,該信號(hào)發(fā)生在CLR引腳回到高電平之后。

IOVDD和電平變換器

DAC7551-Q1器件可用于需要大范圍電源電壓的不同邏輯系列。為了啟用這個(gè)有用的功能,IOVDD引腳必須連接到系統(tǒng)的邏輯電源電壓。所有的DAC7551-Q1數(shù)字輸入和輸出引腳都配有電平轉(zhuǎn)換電路。輸入引腳上的電平移位器確保外部邏輯高壓轉(zhuǎn)換為內(nèi)部邏輯高壓,無(wú)需額外的功耗。類似地,SDO管腳的電平移位器將內(nèi)部邏輯高電壓(VDD)轉(zhuǎn)換為外部邏輯高電平(IOVDD)。對(duì)于單電源操作,IOVDD引腳可連接至VDD引腳。

積分和微分線性度

DAC7551-Q1器件采用精密薄膜電阻,提供卓越的線性度和單調(diào)性。積分線性誤差通常在±0.35 LSBs內(nèi),微分線性誤差通常在±0.08 LSBs內(nèi)。

故障能量

DAC7551-Q1設(shè)備采用專有架構(gòu),最大限度地減少故障能量。碼對(duì)碼的小故障是如此之低,以至于它們通常隱藏在寬帶噪聲中,并且不容易被檢測(cè)出來(lái)。這個(gè)DAC7551-Q1故障通常低于0.1 nV-s。這種低故障能量比工業(yè)替代品提高了10倍以上。

設(shè)備功能模式

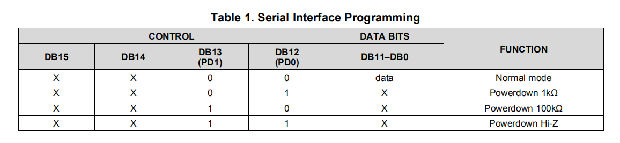

DAC7551-Q1設(shè)備使用四種操作模式。通過(guò)在控制寄存器中設(shè)置位PD0(DB13)和PD1(DB14),可以訪問(wèn)這些模式。表1顯示了如何使用數(shù)據(jù)位PD0(DB13)和PD1(DB14)來(lái)控制操作模式。DAC7551-Q1設(shè)備將斷電情況視為數(shù)據(jù);所有操作模式對(duì)斷電仍然有效。可以向系統(tǒng)中的所有DAC7551-Q1設(shè)備廣播斷電條件。關(guān)閉一個(gè)通道并更新其他通道上的數(shù)據(jù)也是可能的。此外,還可以寫入斷電的DAC信道的DAC寄存器或緩沖器。當(dāng)DAC通電時(shí),DAC包含此新值。

當(dāng)PD0和PD1位都設(shè)置為0時(shí),設(shè)備正常工作,2.7 V下的典型消耗為100μA。對(duì)于三種斷電模式,電源電流在2.7 V時(shí)降至0.05μA。如表1所示,有三種不同的斷電選項(xiàng)。VOUT引腳可以通過(guò)1-kΩ電阻或100-kΩ電阻內(nèi)部連接到GND,也可以是開路的(High-Z)。換句話說(shuō),DB14和DB13=11表示所選信道具有高Z輸出阻抗的斷電條件。DB14和DB13=01和10分別代表1-kΩ和100-kΩ輸出阻抗的斷電條件。

編程

串行接口

DAC7551-Q1設(shè)備通過(guò)多功能3線串行接口控制,該接口以高達(dá)50 MHz的時(shí)鐘速率工作,并與SPI、QSPI、Microwire和DSP接口標(biāo)準(zhǔn)兼容。

16位字和輸入移位寄存器

輸入移位寄存器的寬度為16位。在串行時(shí)鐘輸入SCLK的控制下,DAC數(shù)據(jù)以16位字的形式加載到設(shè)備中,如圖1所示。表1中列出的16位字由4個(gè)控制位和12位DAC數(shù)據(jù)組成。數(shù)據(jù)格式為直接二進(jìn)制,所有0對(duì)應(yīng)0-V輸出,所有1對(duì)應(yīng)滿標(biāo)度輸出(VREF–1 LSB)。數(shù)據(jù)首先加載MSB(位15),其中前兩位(DB15和DB14)是不重要的位。位13和位12(DB13和DB12)確定正常模式操作或斷電模式(見表1)。

同步輸入是一個(gè)電平觸發(fā)輸入,用作幀同步信號(hào)和芯片啟用。數(shù)據(jù)只能在同步管腳低的情況下傳輸?shù)皆O(shè)備中。要開始串行數(shù)據(jù)傳輸,同步引腳應(yīng)取低,觀察最小同步到SCLK下降沿設(shè)置時(shí)間t4。同步引腳變低后,串行數(shù)據(jù)被轉(zhuǎn)移到SCLK下降沿上的設(shè)備輸入移位寄存器中,持續(xù)16個(gè)時(shí)鐘脈沖。

在同步管腳變低后,SPI被啟用,數(shù)據(jù)被連續(xù)地轉(zhuǎn)移到SCLK輸入的每個(gè)下降沿的移位寄存器中。當(dāng)同步管腳被調(diào)高時(shí),存儲(chǔ)在移位寄存器中的最后16位被鎖存到DAC寄存器中,并且DAC更新。

菊花鏈操作

菊花鏈操作用于更新同步輸入上升沿上的串行連接設(shè)備。

只要同步引腳為高電平,SDO引腳就處于高阻抗?fàn)顟B(tài)。當(dāng)同步引腳降低時(shí),內(nèi)部移位寄存器的輸出與SDO引腳相連。只要同步引腳為低電平,SDO引腳就以16周期延遲復(fù)制SDIN信號(hào)。為了支持菊花鏈中的多個(gè)設(shè)備,SCLK和同步信號(hào)在所有設(shè)備之間共享,并且一個(gè)DAC7551-Q1設(shè)備的SDO引腳應(yīng)該綁定到下一個(gè)DAC7551-Q1設(shè)備的SDIN引腳。對(duì)于這種菊花鏈中的n個(gè)設(shè)備,需要16n個(gè)SCLK周期來(lái)移動(dòng)整個(gè)輸入數(shù)據(jù)流。在接收到16n個(gè)SCLK下降沿之后,在下降同步信號(hào)之后,數(shù)據(jù)流變得完整,同步管腳可以被調(diào)高以同時(shí)更新n個(gè)設(shè)備。SDO操作的最大SCLK速度為10 MHz。

在菊花鏈模式下,建議在SDO輸出引腳上使用一個(gè)弱下拉電阻器,該電阻為鏈中的下一個(gè)設(shè)備提供SDIN數(shù)據(jù)。對(duì)于獨(dú)立操作,最大時(shí)鐘速度為50 MHz。對(duì)于菊花鏈操作,最大時(shí)鐘速度為10 MHz。

應(yīng)用與實(shí)施

注意

以下應(yīng)用章節(jié)中的信息不是TI組件規(guī)范的一部分,TI不保證其準(zhǔn)確性或完整性。TI的客戶負(fù)責(zé)確定組件的適用性。客戶應(yīng)驗(yàn)證和測(cè)試其設(shè)計(jì)實(shí)現(xiàn),以確認(rèn)系統(tǒng)功能。

申請(qǐng)信息

波形生成

由于DAC7551-Q1器件具有優(yōu)異的線性度和低故障,因此該器件非常適合于波形生成(從直流到10kHz)。DAC7551-Q1大信號(hào)穩(wěn)定時(shí)間為5μs,支持200ksps的更新速率。然而,如果要生成的波形由連續(xù)DAC更新之間的小電壓階躍組成,則更新速率可以超過(guò)1msps。為了獲得高動(dòng)態(tài)范圍,建議使用REF3140裝置(4.096V)或REF02裝置(5V)來(lái)產(chǎn)生參考電壓。

產(chǎn)生±5-V、±10-V和±12-V輸出,用于精密工業(yè)控制

工業(yè)控制應(yīng)用需要多個(gè)反饋回路,包括傳感器、模數(shù)轉(zhuǎn)換器(ADC)、微控制器(MCU)、DAC和執(zhí)行器。環(huán)路精度和環(huán)路速度是此類控制回路的兩個(gè)重要參數(shù)。

回路精度

DAC偏移、增益和積分線性誤差不是決定環(huán)路精度的因素。只要在單調(diào)數(shù)模轉(zhuǎn)換器的傳輸曲線中存在一個(gè)電壓,環(huán)路就可以找到該電壓并加以調(diào)整。另一方面,DAC分辨率和微分線性度確實(shí)決定了環(huán)路的精度,因?yàn)槊總€(gè)DAC步驟都決定了環(huán)路可以產(chǎn)生的最小增量變化。DNL誤差小于–1 LSB(非單調(diào)性)會(huì)導(dǎo)致環(huán)路不穩(wěn)定。DNL誤差大于1 LSB意味著不必要的大電壓階躍和錯(cuò)過(guò)的電壓目標(biāo)。當(dāng)DNL誤差較大時(shí),回路將失去穩(wěn)定性、分辨率和精度。DAC755x器件具有12位保證的單調(diào)性和±0.08-LSB的典型DNL誤差,是精密控制回路的最佳選擇。

環(huán)路速度

許多因素決定了控制回路的速度,如ADC轉(zhuǎn)換時(shí)間、MCU速度和DAC設(shè)置時(shí)間。通常,ADC轉(zhuǎn)換時(shí)間和MCU計(jì)算時(shí)間是控制環(huán)路時(shí)間常數(shù)的兩個(gè)主要因素。由于ADC轉(zhuǎn)換時(shí)間通常超過(guò)DAC轉(zhuǎn)換時(shí)間,所以DAC的穩(wěn)定時(shí)間很少是主要因素。DAC偏移、增益和線性誤差只能在啟動(dòng)過(guò)程中減慢環(huán)路速度。當(dāng)環(huán)路達(dá)到穩(wěn)態(tài)運(yùn)行時(shí),這些誤差不會(huì)進(jìn)一步影響環(huán)路速度。根據(jù)環(huán)路傳輸函數(shù)的振鈴特性,DAC故障也會(huì)減慢環(huán)路速度。DAC7551-Q1具有1-MSPS(小信號(hào))最大數(shù)據(jù)更新率,可支持高速控制回路。DAC7551-Q1器件的超低故障能量顯著提高了環(huán)路穩(wěn)定性和環(huán)路穩(wěn)定時(shí)間。

典型應(yīng)用

產(chǎn)生工業(yè)電壓范圍

對(duì)于控制回路應(yīng)用,DAC增益和偏移誤差不是重要參數(shù)。這種考慮可以用來(lái)降低高壓控制電路設(shè)計(jì)中的微調(diào)和校準(zhǔn)成本。使用四路運(yùn)算放大器(OPA4130)和電壓基準(zhǔn)(REF3140),DAC7551-Q1可以產(chǎn)生控制回路所需的寬電壓波動(dòng)。

設(shè)計(jì)要求

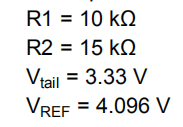

對(duì)于±5-V操作:

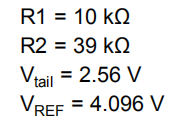

對(duì)于±10-V操作:

對(duì)于±12-V操作:

詳細(xì)設(shè)計(jì)程序

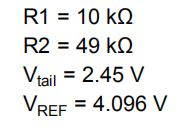

使用方程式2計(jì)算配置的輸出電壓。

固定的R1和R2電阻可用于粗略設(shè)置方程第一項(xiàng)所需的增益。當(dāng)R2和R1將增益設(shè)置為包括一些最小的超量程增益時(shí),可以使用單個(gè)DAC7551-Q1設(shè)備來(lái)設(shè)置所需的偏移電壓。殘余誤差不是環(huán)路精度的問(wèn)題,因?yàn)槠坪驮鲆嬲`差是可以容忍的。一個(gè)DAC7551-Q1設(shè)備可以提供Vtail電壓,而另外四個(gè)DAC7551Q1設(shè)備可以提供Vdac電壓以產(chǎn)生四個(gè)高壓輸出。一個(gè)SPI足以控制菊花鏈配置中的所有五個(gè)DAC7551-Q1設(shè)備。

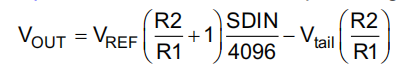

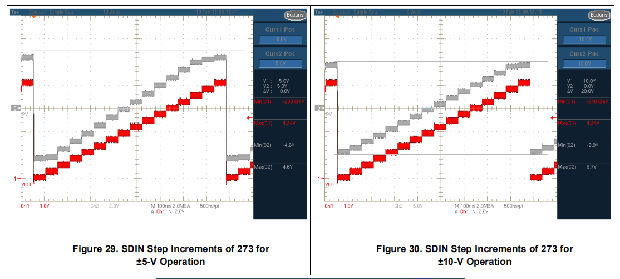

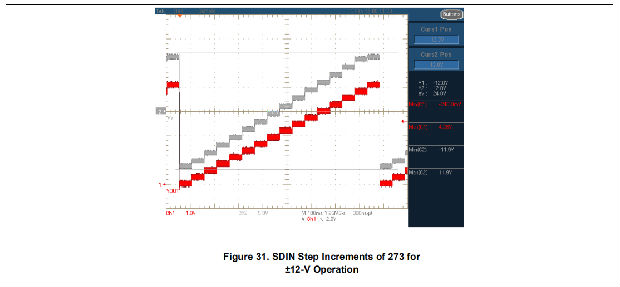

應(yīng)用曲線

電源建議

施加在VDD引腳上的電源應(yīng)調(diào)節(jié)良好,噪音低。開關(guān)電源和DC-DC變換器的輸出電壓經(jīng)常出現(xiàn)高頻故障或尖峰。此外,數(shù)字元件可以產(chǎn)生與內(nèi)部邏輯開關(guān)狀態(tài)類似的高頻尖峰。這種噪聲可以很容易地通過(guò)電源連接和模擬輸出之間的各種路徑耦合到DAC輸出電壓中。與GND連接一樣,VDD引腳應(yīng)連接到與數(shù)字邏輯連接分離的跡線電源平面,直到它們?cè)陔娫慈肟邳c(diǎn)連接。此外,強(qiáng)烈建議使用1-μF和10-μF電容器以及0.1-μF旁路電容器。在某些情況下,可能需要額外的旁路,例如100μF電解電容器,甚至是由電感器和電容器組成的Pi濾波器。這些旁路方法都是為低通濾波電源和消除高頻噪聲而設(shè)計(jì)的。

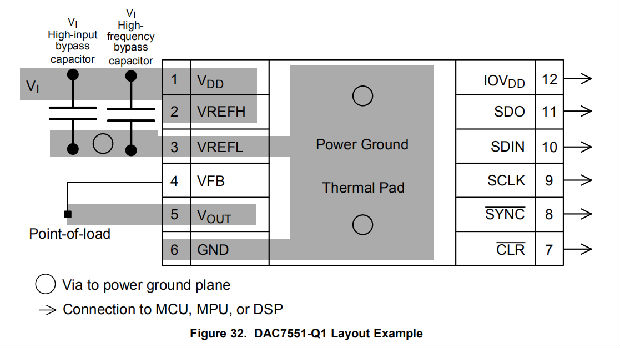

布局

布局指南

一個(gè)精密的模擬元件需要仔細(xì)的布局,足夠的旁路,以及干凈、調(diào)節(jié)良好的電源。DAC7551-Q1設(shè)備提供單電源操作,通常與數(shù)字邏輯、微控制器、微處理器、數(shù)字信號(hào)處理器或組合使用。設(shè)計(jì)中的數(shù)字邏輯越多,開關(guān)速度越高,就越難防止輸出端出現(xiàn)數(shù)字噪聲。由于DAC7551-Q1設(shè)備的單個(gè)接地引腳,所有回路電流(包括DAC的數(shù)字和模擬回路電流)必須流經(jīng)一個(gè)單點(diǎn)。理想情況下,GND應(yīng)直接連接到模擬接地層。該平面應(yīng)與數(shù)字部件的接地連接分開,直到這些部件在系統(tǒng)的電源入口連接。

布局示例

安芯科創(chuàng)是一家國(guó)內(nèi)芯片代理和國(guó)外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國(guó)產(chǎn)降成本等解決方案,可承接項(xiàng)目開發(fā),以及元器件一站式采購(gòu)服務(wù),類型有運(yùn)放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價(jià)格請(qǐng)咨詢?cè)诰€客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國(guó)民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國(guó)泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來(lái)源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號(hào):粵ICP備2023092210號(hào)-1