特征

•14通道伽馬校正

•2個VCOM輸出

•片上OTP存儲器

•10位分辨率

•軌對軌輸出

•低電源電流:1mA/ch

•電源電壓:8.5V至18V

•數(shù)字電源:2.0V至5.5V

•行業(yè)標準,雙線接口:3.4MHz高速模式

•高ESD額定值:4kV HBM,1kV CDM,200V毫米

•提供演示板和軟件

應(yīng)用

•取代基于電阻的伽馬解決方案

•TFT-LCD參考驅(qū)動程序

•動態(tài)伽馬控制

說明

BUF16820是一個可編程基準電壓發(fā)生器,設(shè)計用于TFT-LCD面板中的伽馬校正。它提供14個可編程輸出和兩個VCOM通道,每個通道的分辨率為10位。它提供片上一次性可編程(OTP)存儲器,允許用戶在芯片上存儲伽馬電壓。這樣就不需要外部EEPROM。

這種可編程性取代了傳統(tǒng)的、耗時的改變電阻值以優(yōu)化各種伽馬電壓的過程,并允許設(shè)計者快速確定面板的正確伽馬電壓。也可以在不改變硬件電壓的情況下輕松實現(xiàn)。

BUF16820采用了TI最新的小幾何模擬CMOS工藝,這使得它成為全面生產(chǎn)的一個非常有競爭力的選擇,而不僅僅是評估。

通過工業(yè)標準的兩線串行接口對每個輸出進行編程。與現(xiàn)有的可編程緩沖器不同,BUF16820提供了一種高速模式,允許時鐘速度高達3.4MHz。

對于頻道數(shù)較低或較高的設(shè)備,請聯(lián)系您當?shù)氐匿N售或營銷代表。

BUF16820在HTSSOP-32中提供PowerPAD軟件包。規(guī)定溫度范圍為−40°C至+85°C。

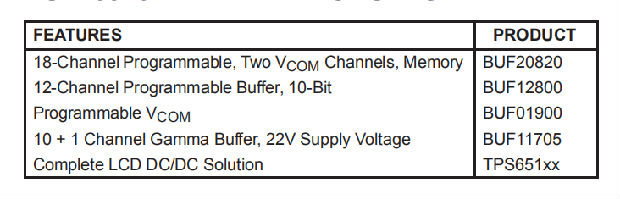

BUF16820相關(guān)產(chǎn)品

典型特征

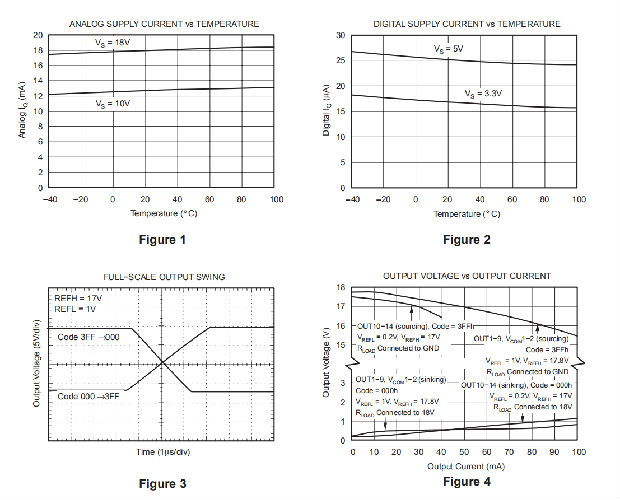

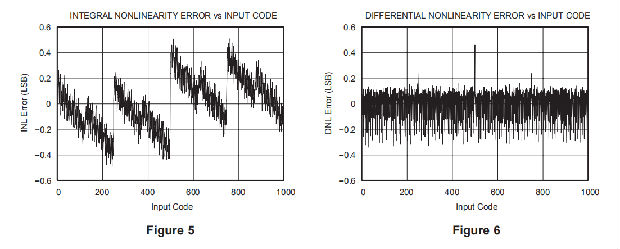

TA=+25°C,VS=18V,VSD=5V,VREFH=17V,VREFL=1V,RL=1.5kΩ接地,CL=200pF時,除非另有說明。

應(yīng)用程序信息

BUF16820可編程基準電壓允許快速方便地調(diào)整14個可編程參考輸出和兩個用于VCOM調(diào)整的通道,每個通道具有10位分辨率。它允許對伽馬基準電壓和VCOM電壓進行非常簡單、高效的調(diào)整。BUF16820是通過高速標準雙線接口編程的。BUF16820為每個DAC通道提供了雙寄存器結(jié)構(gòu),以簡化動態(tài)伽馬控制的實現(xiàn)。這種結(jié)構(gòu)允許預(yù)加載寄存器數(shù)據(jù)和同時快速更新所有通道。

緩沖器1−9能夠在正極供電軌200mV范圍內(nèi)擺動,在負極供電軌0.6V范圍內(nèi)擺動。負向軌10.0伏范圍內(nèi)的正緩沖器向軌10.0伏供電。

BUF16820可以使用8.5V到18V的模擬電源電壓和2V到5.5V的數(shù)字電源供電。數(shù)字電源必須在模擬電源之前或同時使用,以避免過多的電流和功耗;如果長時間只連接模擬電源,可能會損壞設(shè)備。圖7顯示了電源定時要求。

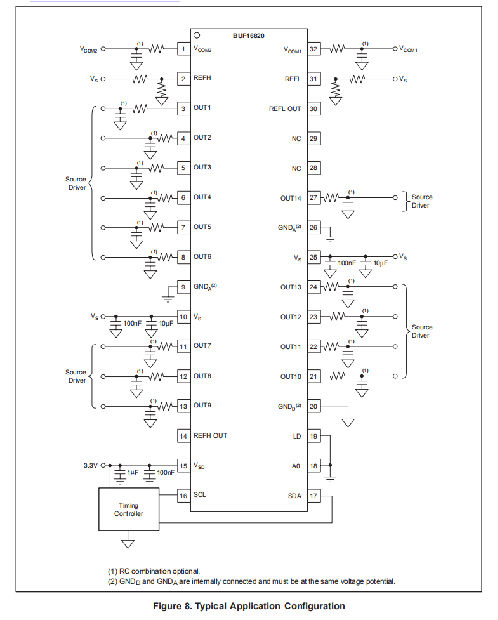

圖8顯示了典型配置中的BUF16820。在這種配置中,BUF16820設(shè)備地址為74h。一旦在相應(yīng)寄存器(LD=0)中接收到數(shù)據(jù),每個數(shù)模轉(zhuǎn)換器(DAC)的輸出立即更新。對于最大動態(tài)范圍,設(shè)置VREFH=VS−0.2V,VREFL=GND+0.2V。

雙線總線概述

BUF16820通過工業(yè)標準雙線接口進行通信,以從模式接收數(shù)據(jù)。本標準使用兩線制開路漏極接口,支持單個總線上的多個設(shè)備。總線只驅(qū)動到邏輯低電平。發(fā)起通信的設(shè)備稱為主設(shè)備,主設(shè)備控制的設(shè)備為奴隸們主機在時鐘信號線(SCL)上生成串行時鐘,控制總線訪問,并生成啟動和停止條件。

為了對特定設(shè)備進行尋址,當SCL處于高電平時,主機通過將數(shù)據(jù)信號線(SDA)從高邏輯電平拉到低邏輯電平來啟動啟動條件。總線上的所有從機都在從機地址字節(jié)中移位,最后一位表示是要進行讀操作還是寫操作。在第9個時鐘脈沖期間,被尋址的從機通過產(chǎn)生一個應(yīng)答并將SDA拉低來響應(yīng)主機。

然后開始數(shù)據(jù)傳輸,發(fā)送8位數(shù)據(jù),然后發(fā)送一個確認位。在數(shù)據(jù)傳輸過程中,當SCL較高時,SDA必須保持穩(wěn)定。當SCL較高時,SDA的任何變化都將被解釋為啟動或停止條件。

一旦所有數(shù)據(jù)都被傳輸,主設(shè)備會生成一個停止條件,在SCL為高時,將SDA從低拉到高。

BUF16820只能作為從設(shè)備;因此,它從不驅(qū)動SCL。SCL引腳只是BUF16820的輸入。表1和表2分別總結(jié)了BUF16820的地址和命令代碼。

處理BUF16820

BUF16820的地址是111010x,其中x是A0引腳的狀態(tài)。當A0引腳低時,設(shè)備將在地址74h(1110100)上確認。如果A0引腳高,設(shè)備將在地址75h(1110101)上確認。

其他有效地址可以通過簡單的掩碼更改來實現(xiàn)。請聯(lián)系您的TI代表以獲取信息。

數(shù)據(jù)速率

雙線總線以三種速度模式之一運行:

*標準——允許時鐘頻率高達100kHz;

*快速——允許時鐘頻率高達400kHz;

*高速——允許時鐘頻率高達3.4MHz。

BUF16820完全兼容所有三種模式。在標準或快速模式下使用設(shè)備無需特殊操作,但必須激活高速(Hs)模式。要激活Hs模式,在啟動條件后發(fā)送一個特殊地址字節(jié)00001xxx,SCL=400kHz;其中xxx是支持Hs的主機的唯一位,可以是任何值。這個字節(jié)稱為Hs主代碼。(請注意,這與正常地址字節(jié)不同,低位不表示讀/寫狀態(tài)。)無論最后三位的值如何,BUF16820都將響應(yīng)Hs命令。BUF16820將不確認該字節(jié);通信協(xié)議禁止確認Hs主代碼。收到主代碼后,BUF16820將打開其Hs模式濾波器,并以高達3.4MHz的頻率進行通信。通過生成無停止的重復(fù)啟動,可以在不重新發(fā)送Hs模式字節(jié)的情況下啟動附加的高速傳輸。BUF16820將在下一個停止條件下退出Hs模式。

一般呼叫重置和通電

BUF16820響應(yīng)一般呼叫重置,即地址字節(jié)00h(0000 0000 0000),后跟數(shù)據(jù)字節(jié)06h(0000 0110)。BUF16820承認這兩個字節(jié)。在接收到一般呼叫重置后,BUF16820會執(zhí)行完全內(nèi)部重置,就好像它已經(jīng)斷電然后再打開一樣。它總是確認00h(0000 0000)的一般呼叫地址字節(jié),但不確認除06h(0000 0110)以外的任何一般呼叫數(shù)據(jù)字節(jié)。

BUF16820通電后自動執(zhí)行復(fù)位。作為重置的一部分,BUF16820配置為所有輸出,以更改為已編程的OTP存儲器值,或在OTP值未編程的情況下更改為0000。

當發(fā)送設(shè)備地址時,BUF16820將所有輸出重置為OTP內(nèi)存值(如果OTP值尚未編程,則重置為0000),然后發(fā)送一個有效的DAC地址,D7到D5位設(shè)置為“100”。如果這些位設(shè)置為'010',則只有在此最高有效字節(jié)和以下最低有效字節(jié)中尋址的DAC將被重置。

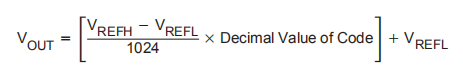

輸出電壓

緩沖器輸出值由參考電壓(VREFH和VREFL)以及用于編程該緩沖器的二進制輸入代碼的十進制值確定。使用方程式(1)計算該值:

參考電壓的有效電壓范圍為:

BUF16820輸出能夠在典型的5μs內(nèi)實現(xiàn)滿量程電壓輸出變化,無需中間步驟。

輸出鎖存器

更新DAC寄存器與更新DAC輸出電壓不同,因為BUF16820具有雙緩沖寄存器結(jié)構(gòu)。有三種方法可以將傳輸?shù)臄?shù)據(jù)從存儲寄存器鎖存到DAC中,以更新DAC輸出電壓。

方法1:需要在外部設(shè)置閂鎖引腳(LD)LOW,LD=LOW,每當其對應(yīng)的寄存器更新時,它就更新每個DAC輸出電壓。

方法2:在外部設(shè)置LD=HIGH,以允許所有DAC輸出電壓在數(shù)據(jù)傳輸期間保持其值,直到LD=LOW,然后同時將所有DAC的輸出電壓更新為新的寄存器值。使用此方法預(yù)先傳輸未來的數(shù)據(jù)集,以準備非常快速的輸出電壓更新。

方法3:采用軟件控制。LD保持為高電平,當主設(shè)備在任何DAC寄存器的第15位寫入“1”和在第14位寫入“0”時,所有的DAC都會更新。更新發(fā)生在接收到當前寫入寄存器的16位數(shù)據(jù)之后。

無論閂鎖引腳的狀態(tài)如何,通電后的一般呼叫重置或重置都會更新DAC。

OTP存儲器的獲取

通用的acquire命令將所有寄存器和DAC輸出更新為存儲在OTP存儲器中的值。

單通道獲取命令只更新與命令中使用的DAC地址對應(yīng)的DAC的寄存器和DAC輸出。

通用獲取命令

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

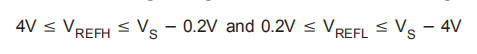

3.發(fā)送一個DAC地址字節(jié)。位D7−D5必須設(shè)置為100。位D4−D0是任何有效的DAC地址。只有地址00000到01101、10010、10011和10100是有效的,并且將被確認。表3顯示了DAC地址。

4.在公共汽車上發(fā)送停車條件。

執(zhí)行此命令后,所有的DAC寄存器和DAC輸出都將更改為OTP內(nèi)存值。

單通道采集命令

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

3.使用與DAC輸出相對應(yīng)的DAC地址發(fā)送一個DAC地址字節(jié),并用OTP內(nèi)存值更新寄存器。位D7−D5必須設(shè)置為010。位D4−D0表示地址。只有地址00000到01101、10010、10011和10100是有效的,并且將被確認。表3顯示了DAC地址。

4.在公共汽車上發(fā)送停車條件。

有關(guān)時序圖,請參見圖12。

讀/寫操作

單個或多個讀寫操作可以在單個通信事務(wù)中完成。寫入DAC寄存器與寫入OTP內(nèi)存不同。數(shù)據(jù)最高有效字節(jié)的位D15−D14確定數(shù)據(jù)將被寫入DAC寄存器還是OTP存儲器。

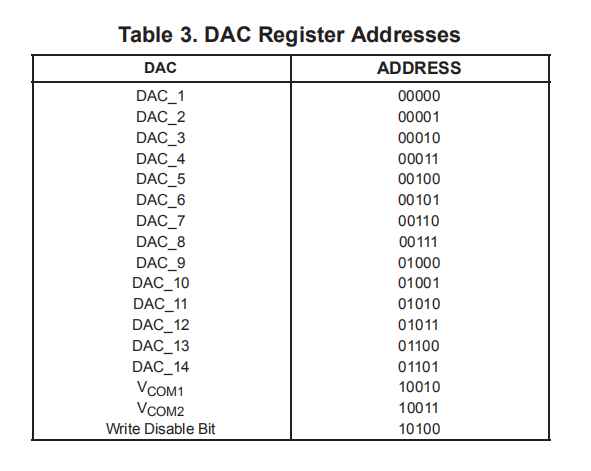

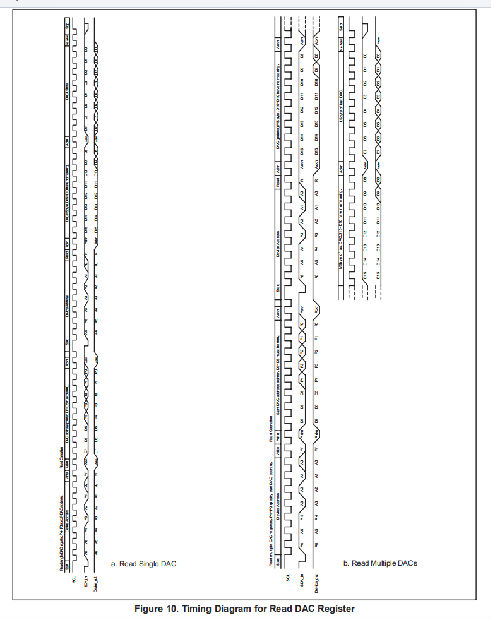

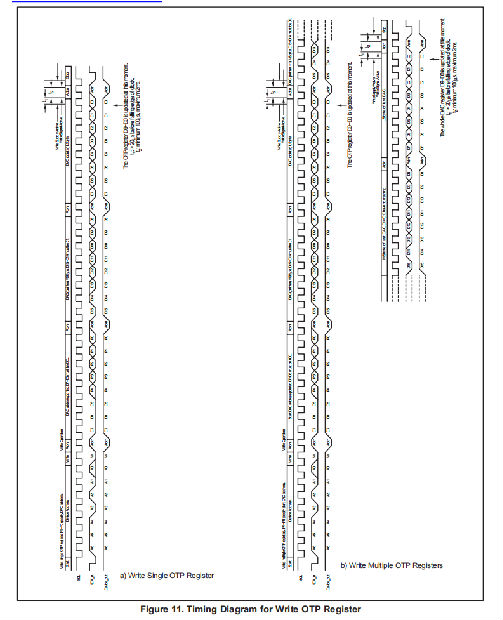

有關(guān)讀/寫命令的時序圖和要求,請參見圖9到圖11。

讀/寫:DAC寄存器

BUF16820能夠在單個通信中從單個DAC或多個DAC讀取,或?qū)懭雴蝹€DAC或多個DAC的寄存器事務(wù)處理.DAC地址以00000開頭(對應(yīng)于DAC_1),一直到01101(對應(yīng)于DAC_14)。地址10010和10011分別對應(yīng)于VCOM1和VCOM2。地址10100對應(yīng)于寫禁用位。

通過將讀/寫位設(shè)置為低位來執(zhí)行寫入命令。將讀/寫位設(shè)置為高位執(zhí)行讀事務(wù)。

寫作:

寫入單個DAC寄存器:

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

3.發(fā)送DAC或?qū)懡梦坏刂纷止?jié)。位D7−D5必須設(shè)置為0。位D4−D0表示地址。只有地址00000到01101、10010、10011和10100是有效的,并且將被確認。表3顯示了DAC地址。

4.為指定的寄存器發(fā)送兩個字節(jié)的數(shù)據(jù)。首先發(fā)送最高有效字節(jié)(位D15−D8,其中僅使用位D9和D8,且位D15−D14不得為01),然后發(fā)送最低有效字節(jié)(位D7−D0)。對于地址10100,只有D0有意義。該位是寫禁用位。寄存器在接收到第二個字節(jié)后被更新。

5.在公共汽車上發(fā)送停車條件。

BUF16820確認每個數(shù)據(jù)字節(jié)。如果主機通過在總線上發(fā)送停止或啟動條件而提前終止通信,則指定的寄存器將不會被更新。更新DAC寄存器與更新DAC輸出電壓不同;請參閱輸出鎖存部分。

更新多個DAC寄存器的過程與更新單個寄存器的過程相同。然而,在寫入尋址寄存器后,主機不再發(fā)送停止條件,而是繼續(xù)為下一個寄存器發(fā)送數(shù)據(jù)。在發(fā)送附加數(shù)據(jù)時,BUF16820會自動并按順序逐步執(zhí)行后續(xù)寄存器。該過程將繼續(xù),直到所有需要的寄存器都已更新或發(fā)出停止條件。

要寫入多個DAC寄存器:

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

3.發(fā)送從第一個DAC開始的DAC_1地址字節(jié),或發(fā)送要更新的DAC序列中第一個DAC的地址字節(jié)。BUF16820將從該DAC開始,并按順序逐步執(zhí)行后續(xù)的DAC。

4.發(fā)送數(shù)據(jù)字節(jié)。首先發(fā)送最高有效字節(jié)(位D15−D8,其中只有位D9和D8有意義,并且位D15−D14不得為01),然后發(fā)送最低有效字節(jié)(位D7−D0)。前兩個字節(jié)用于步驟3中尋址的DAC。它的寄存器在接收到第二個字節(jié)后自動更新。接下來的兩個字節(jié)用于以下DAC;該DAC寄存器在接收到第四個字節(jié)后更新。此過程將繼續(xù),直到以下所有DAC的寄存器都已更新。BUF16820將繼續(xù)接受總共20個DAC的數(shù)據(jù);但是,第14個數(shù)據(jù)集之后的四個數(shù)據(jù)集將毫無意義。第19和第20組數(shù)據(jù)將適用于VCOM1和VCOM2。無法使用此方法訪問寫禁用位。必須使用寫入單個DAC寄存器過程將其寫入。

5.在公共汽車上發(fā)送停車條件。

BUF16820確認每個字節(jié)。要終止通信,請在總線上發(fā)送停止或啟動條件。只有接收到兩個字節(jié)數(shù)據(jù)的DAC寄存器才會被更新。

閱讀:

讀取DAC寄存器返回存儲在DAC中的數(shù)據(jù)。此數(shù)據(jù)可能與存儲在DAC寄存器中的數(shù)據(jù)不同;請參閱輸出鎖存器部分。

要讀取DAC值:

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

3.發(fā)送DAC地址字節(jié)。位D7−D5必須設(shè)置為0;位D4−D0是DAC地址。只有地址00000到01101、10010、10011和10100是有效的,并且將被確認。對于地址10100,只有D0有意義。該位是寫禁用位。

4.發(fā)送啟動或停止/啟動條件。

5.發(fā)送正確的設(shè)備地址,讀/寫位=高。BUF16820將確認該字節(jié)。

6.接收兩個字節(jié)的數(shù)據(jù)。它們用于指定的DAC。第一個接收到的字節(jié)是最高有效字節(jié)(位D15−D8;只有位D9和D8有意義),下一個字節(jié)是最低有效字節(jié)(位D7−D0)。

7.收到第一個字節(jié)后確認。

8.在總線上發(fā)送停止條件或不確認第二個字節(jié)以結(jié)束讀取事務(wù)。

可通過在總線上發(fā)送過早停止或啟動條件或不發(fā)送確認來終止通信。

要讀取多個DAC:

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

3.發(fā)送從第一個DAC開始的DAC_1地址字節(jié),或發(fā)送要讀取的DAC序列中第一個DAC的地址字節(jié)。BUF16820將從該DAC開始,并按順序逐步執(zhí)行后續(xù)的DAC。BUF16820將繼續(xù)接受總共20個DAC的數(shù)據(jù);但是,第14個數(shù)據(jù)集之后的四個數(shù)據(jù)集將毫無意義。第19和第20組數(shù)據(jù)將適用于VCOM1和VCOM2。

4.在總線上發(fā)送啟動或停止/啟動條件。

5.發(fā)送正確的設(shè)備地址,讀/寫位=高。BUF16820將確認該字節(jié)。

6.接收兩個字節(jié)的數(shù)據(jù)。它們用于指定的DAC。第一個接收到的字節(jié)是最高有效字節(jié)(位D15−D8;只有位D9和D8有意義),下一個字節(jié)是最低有效字節(jié)(位D7−D0)。

7.接收到每個字節(jié)后確認。

8.當所有需要的DAC都被讀取后,在總線上發(fā)送一個停止或啟動條件。

可通過在總線上發(fā)送過早停止或啟動條件或不發(fā)送確認來終止通信。

寫入:用于DAC寄存器的OTP內(nèi)存

BUF16820能夠在單個通信事務(wù)中寫入單個DAC或多個DAC的OTP內(nèi)存。DAC地址以00000(對應(yīng)于DAC_1)到01101(對應(yīng)于DAC_14)開頭。地址10010和10011對應(yīng)于分別是VCOM1和VCOM2。地址10100對應(yīng)于寫禁用位。

對OTP存儲器編程時,模擬電源電壓必須在8.5V和18V之間。

通過將讀/寫位設(shè)置為低位來執(zhí)行寫入命令。

寫入單個OTP寄存器:

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

3.發(fā)送DAC地址字節(jié)。位D7−D5必須設(shè)置為0。位D4−D0是DAC地址。只有地址00000到01101、10010、10011和10100是有效的,并且將被確認。表3顯示了DAC地址。

4.為指定DAC的OTP寄存器發(fā)送兩個字節(jié)的數(shù)據(jù)。首先發(fā)送最高有效字節(jié)(位D15−D8,其中只有位D9和D8是數(shù)據(jù)位,位D15−D14必須是01),然后是最低有效字節(jié)(位D7−D0)。對于地址10100,只有D0有意義。該位是寫禁用位。寄存器在接收到第二個字節(jié)后被更新。

5.在公共汽車上發(fā)送停車條件。

BUF16820將確認每個數(shù)據(jù)字節(jié)。如果主機通過在總線上發(fā)送停止或啟動條件而提前終止通信,則指定的OTP寄存器將不會更新。寫入OTP寄存器也會更新DAC寄存器和輸出電壓。

寫入多個OTP寄存器:

1.在總線上發(fā)送啟動條件。

2.發(fā)送設(shè)備地址,讀/寫位=低。BUF16820將確認該字節(jié)。

3.發(fā)送從第一個DAC的OTP寄存器開始的DAC_1地址字節(jié),或發(fā)送要更新序列中第一個DAC的地址字節(jié)。BUF16820將從該DAC的OTP寄存器開始,并按順序逐步執(zhí)行后續(xù)寄存器。

4.發(fā)送數(shù)據(jù)字節(jié)。D0的有效位必須是D0的最低位(D0的有效位必須是D0的最低有效位,D8后面必須是d1的最低位)。前兩個字節(jié)用于在步驟3中尋址的DAC的OTP寄存器。這個OTP寄存器在接收到第二個字節(jié)后自動更新。接下來的兩個字節(jié)用于以下DAC的OTP寄存器(位D15−D14必須再次為01)。該DAC OTP寄存器在接收到第四個字節(jié)后被更新。此過程將繼續(xù),直到以下所有DAC OTP寄存器的寄存器都已更新。BUF16820將繼續(xù)接受總共20個DAC的數(shù)據(jù);但是,第14個數(shù)據(jù)集之后的四個數(shù)據(jù)集將毫無意義。第19和第20組數(shù)據(jù)將適用于VCOM1和VCOM2。無法使用此方法訪問寫禁用位。必須使用寫入單個OTP寄存器過程將其寫入。

5.在公共汽車上發(fā)送停車條件。

BUF16820將確認每個字節(jié)。要終止通信,請在總線上發(fā)送停止或啟動條件。只有接收到兩個字節(jié)數(shù)據(jù)的DAC寄存器才被編程。

OTP寫入禁用

在寄存器10100的位D0中寫入“1”將禁用將來的所有寫入操作。這個位的狀態(tài)可以像任何其他數(shù)據(jù)位一樣被訪問。在對OTP寄存器進行編程后,必須將該位設(shè)置為“1”,以防止對OTP寄存器的意外更改。在寄存器10100的位D0設(shè)置為“1”之前,任何OTP寄存器位都可以從“0”更改為“1”;但是,一旦將某個位設(shè)置為“1”,則不能將其設(shè)置回“0”。

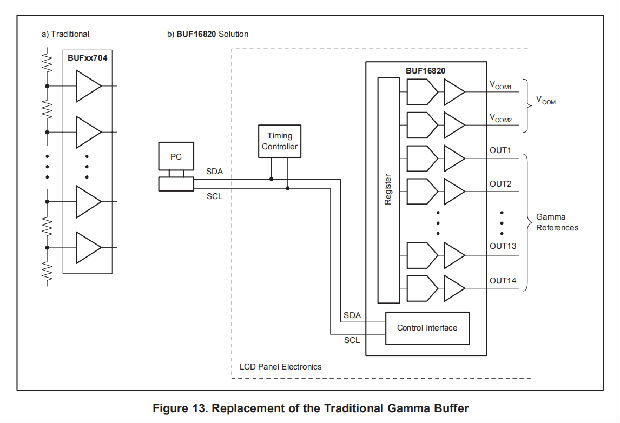

取代傳統(tǒng)的伽馬緩沖器

傳統(tǒng)的gamma緩沖器依靠電阻串(通常使用昂貴的0.1%電阻)來設(shè)置伽馬電壓。在開發(fā)過程中,優(yōu)化這些伽馬電壓可能很耗時。用BUF16820編程這些伽馬電壓可以顯著減少伽馬電壓優(yōu)化所需的時間。最終的gamma值可以寫入內(nèi)部OTP存儲器,以取代傳統(tǒng)的gamma緩沖解決方案。圖13a顯示了傳統(tǒng)的電阻串;圖13b顯示了使用BUF16820的更有效的替代方法。

BUF16820采用當今最先進的高壓CMOS工藝,這使得它能夠與傳統(tǒng)的伽馬緩沖器相競爭。

可編程性具有以下優(yōu)點:

*大大縮短了開發(fā)時間。

*通過消除18個以上的外部組件提高可靠性。

*消除面板之間的制造差異。

*允許客戶在最終生產(chǎn)過程中使用多個伽馬曲線來構(gòu)建客戶相關(guān)曲線。這種方法大大降低了庫存成本和風險,簡化了庫存管理。

*只需上傳一組不同的伽馬值,就可以向液晶顯示器制造商演示各種伽馬曲線。

*允許在生產(chǎn)過程中對伽馬曲線進行簡單調(diào)整,以適應(yīng)面板制造工藝或最終客戶要求的變化。

*降低成本和空間。

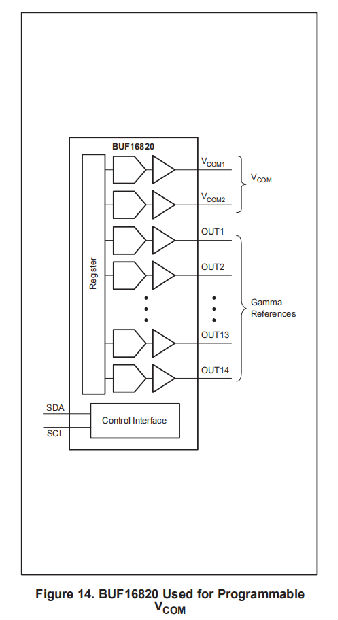

可編程VCOM

BUF16820的VCOM通道可以從正電源線切換到2.5V,而在輸出電流為100mA時,可以從負電源線切換到1V(參見圖4,典型的輸出電壓與輸出電流的關(guān)系)。gamma和VCOM值可以永久存儲在內(nèi)部OTP存儲器中。VCOM通道可獨立于伽馬通道編程。圖14顯示了用于VCOM電壓的BUF16820。

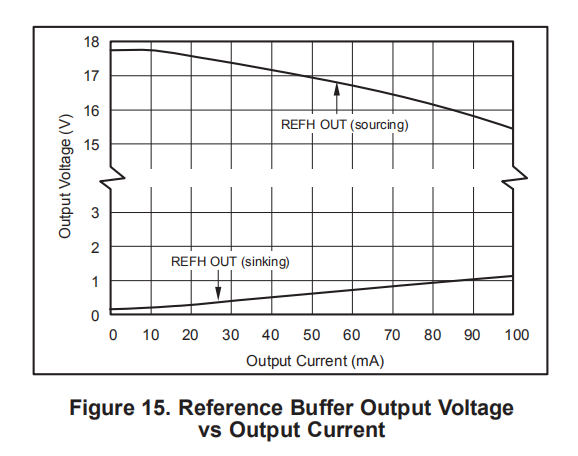

REFH和REFL輸入范圍

BUF16820的最佳性能和輸出擺動范圍是通過施加略低于電源電壓的REFH和REFL電壓實現(xiàn)的。大多數(shù)規(guī)格在REFH=VS−200mV和REFL=GND+200mV下進行了測試。這個REFH內(nèi)部緩沖區(qū)的設(shè)計非常接近VS,REFL internal buffer被設(shè)計成與GND非常接近。然而,它們在飽和前擺動的距離是有限的。為避免內(nèi)部REFH和REFL緩沖器飽和,REFH電壓不得大于VS−100mV,REFL電壓不得低于GND+100mV。圖15顯示了REFH和REFL緩沖區(qū)的擺動能力。

當試圖最大化gamma緩沖器的輸出擺動能力時,另一個考慮因素是輸出緩沖器(OUT1−14、VCOM1和VCOM2)擺動范圍的限制,這取決于負載電流。LCD應(yīng)用中的典型負載是5mA到10mA。例如,如果OUT1的電源是10mA,則擺動通常限制在VS−200mV左右。這同樣適用于OUT14,當下沉10mA時,它通常限制在GND+200mV。輸出擺幅的增加只能在負載較輕的情況下實現(xiàn)。例如,3mA負載通常允許擺動增加到VS−100mV和GND+100mV左右。

將REFH直接連接到VS和REFL直接連接到GND不會損壞BUF16820。但是,如上所述,REFH和REFL緩沖器的輸出級將飽和。這種情況并不理想,可能會導致測量的輸出電壓出現(xiàn)小誤差輸出1−14、VCOM1和VCOM2。如上所述,這種連接REFH和REFL的方法無助于最大化輸出擺動能力。

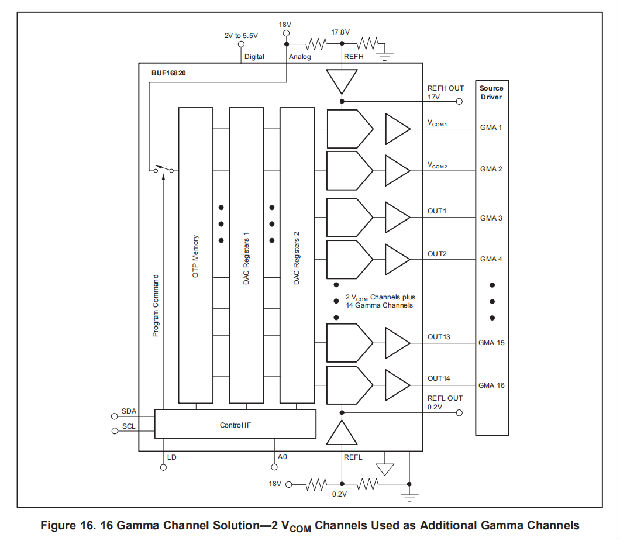

16個伽馬通道的配置

VCOM輸出可作為額外的伽馬參考,以實現(xiàn)兩個額外的伽馬通道(總共16個)。當產(chǎn)生或吸收較小電流時,VCOM輸出將與OUT1−9輸出相同(參見典型特性,圖4)。VCOM輸出能夠更好地擺動到正軌道,而不是反向軌道。因此,最好將VCOM輸出用于更高的參考電壓,如圖16所示。

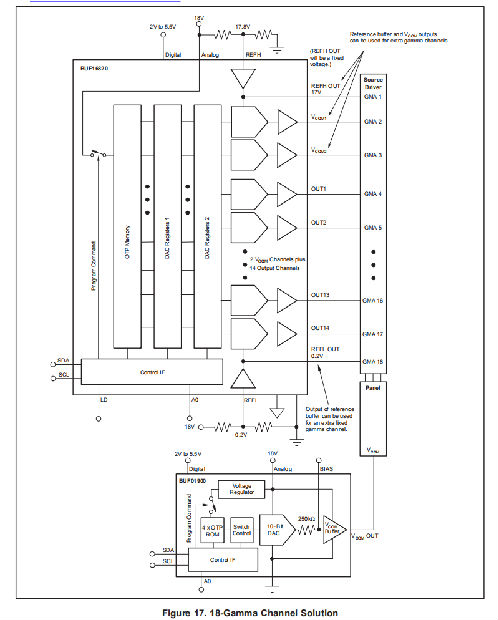

18個伽馬通道的配置

除VCOM輸出外,REFH和REFL OUT輸出也可用作固定伽馬參考。輸出電壓分別由REFH和REFL輸入電壓設(shè)置。因此,REFH OUT應(yīng)用于最高電壓gamma基準,REFL OUT用于最低電壓gamma基準。通過使用所有14個輸出、兩個VCOM輸出和兩個REFH/L OUT輸出,可以創(chuàng)建一個18通道的解決方案;見圖17。然而,REFH和REFL OUT緩沖器設(shè)計為僅驅(qū)動5mA至10mA的輕負載。不建議使用這些緩沖器驅(qū)動電容性負載。此外,REFH和REFL緩沖器不得因REFH OUT或REFL OUT的源極/漏電流過大而飽和。REFH和REFL緩沖器的飽和導致OUT1−14的電壓誤差,VCOM1和VCOM2。BUF01900(預(yù)期于2006年第2季度發(fā)布)可用于提供可編程VCOM輸出。

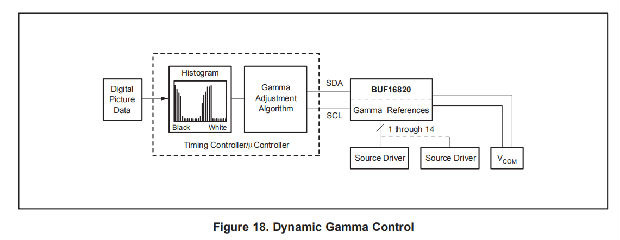

動態(tài)伽馬控制

動態(tài)伽瑪控制是一種用于改善液晶電視圖像質(zhì)量的技術(shù)。分析每個畫面幀中的亮度,并逐幀調(diào)整伽馬曲線。伽馬曲線通常在視頻信號中的短垂直消隱期間更新。圖18顯示了使用BUF16820進行動態(tài)伽馬控制和VCOM輸出的框圖。

由于其獨特的拓撲結(jié)構(gòu),BUF16820非常適合快速改變伽馬曲線:

*DAC的雙寄存器輸入結(jié)構(gòu)。

*快速串行接口。

*通過軟件同步更新所有DAC。請參閱讀/寫操作和輸出鎖存器部分。

雙寄存器輸入結(jié)構(gòu)通過允許將更新的DAC值預(yù)加載到第一寄存器組來節(jié)省編程時間。當圖片仍在顯示時,可以存儲此數(shù)據(jù)。由于數(shù)據(jù)只存儲在第一寄存器組中,所以DAC輸出值保持不變,顯示不受影響。在垂直同步期間,可以通過使用連接到LD管腳的附加控制線或通過軟件在任何DAC寄存器的第15位寫入“1”,來快速更新DAC輸出(因此,伽馬電壓)。有關(guān)雙寄存器輸入結(jié)構(gòu)操作的詳細信息,請參閱輸出鎖存器部分。

例子:通過軟件同時更新所有14個伽馬寄存器。

第1步:檢查LD引腳是否處于高狀態(tài)。

第2步:寫入DAC寄存器1−14,位15始終為“0”。

第3步:用相同的數(shù)據(jù)再次寫入任何DAC寄存器。確保位15為“1”。所有的DAC通道將在接收到最后一位數(shù)據(jù)后同時更新。(注:此步驟可通過在上一步驟中將DAC 14的位15設(shè)置為“1”來消除。)

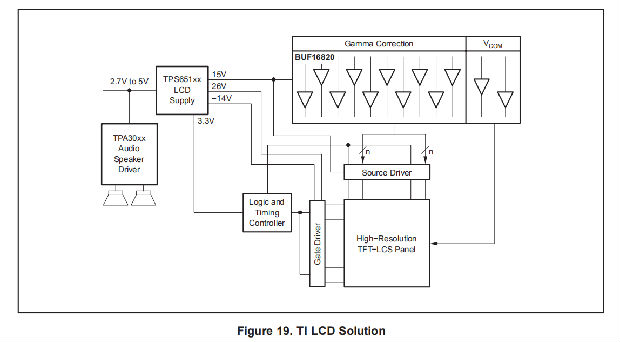

鈦板整體解決方案

除了BUF16820可編程基準電壓源外,TI還為LCD面板市場提供一整套集成電路,包括伽馬校正緩沖器、各種電源解決方案和音頻電源解決方案。TI的總IC溶液見圖19。

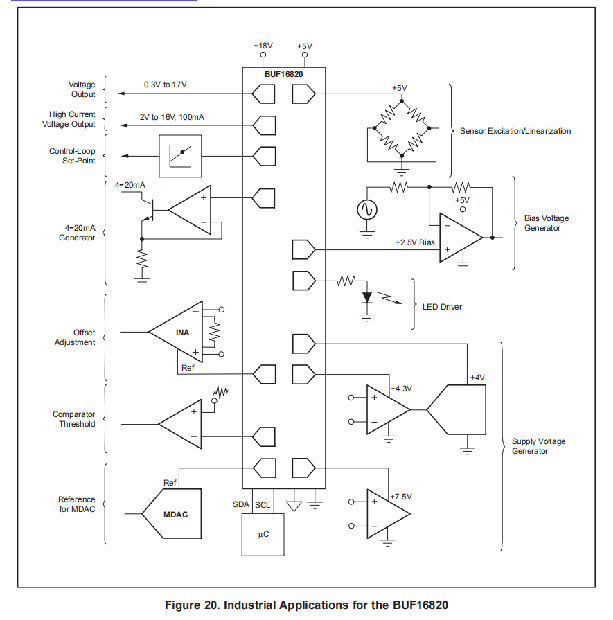

工業(yè)應(yīng)用中的BUF16820

BUF16820電源范圍廣,輸出電流高,成本極低,在可編程電源、多通道數(shù)據(jù)采集系統(tǒng)、數(shù)據(jù)記錄器、傳感器激勵和線性化、電源生成等一系列中等精度工業(yè)應(yīng)用中具有吸引力。每個DAC通道具有1LSB DNL和INL。

許多系統(tǒng)需要不同水平的偏壓和電源,用于不同的部件,以及傳感器勵磁、控制回路設(shè)定點、電壓輸出、電流輸出和其他功能。BUF16820有16個可編程DAC通道,通過允許設(shè)計者通過軟件更改所有這些參數(shù),為整個系統(tǒng)提供了極大的靈活性。

圖20提供了在應(yīng)用程序中如何使用BUF16820的各種示例。帶有兩線串行接口的微控制器控制BUF16820的各種DAC。BUF16820可用于:

*傳感器激勵

*可編程偏置/參考電壓

*可變電源

*高電流電壓輸出

*4-20mA輸出

*控制回路設(shè)定點發(fā)生器

注:通電時,BUF16820 DAC的輸出電壓設(shè)置為已編程的OTP存儲器值,或者如果OTP值尚未編程,則設(shè)置為0000。

評估板和軟件

BUF16820有一個評估委員會,如圖21所示。評估板的特點是易于使用的軟件,可以設(shè)置單獨的通道電壓。可以快速評估配置以確定給定應(yīng)用程序的最佳代碼。有關(guān)評估委員會的更多信息,請聯(lián)系您當?shù)氐腡I代表。

電源板設(shè)計的一般注意事項

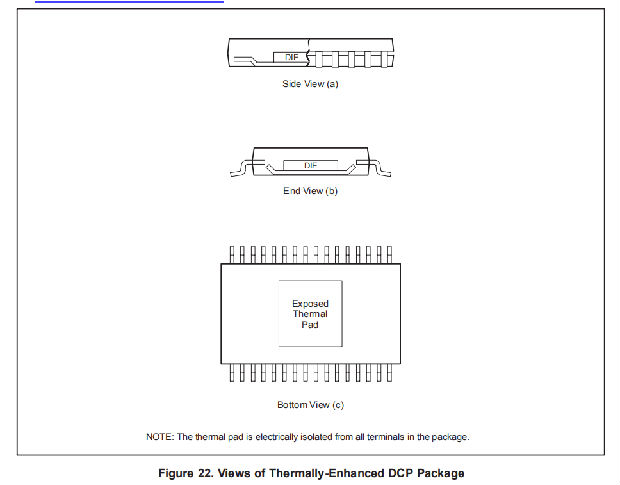

BUF16820提供熱增強型PowerPAD封裝。這個包裝是用一個下裝引線框架構(gòu)造的,模具安裝在上面;見圖22(a)和圖22(b)。這種布置導致引線框架暴露在封裝底部的熱墊上;見圖22(c)。該熱墊與模具直接熱接觸;因此,通過提供遠離熱墊的良好熱路徑,可獲得優(yōu)異的熱性能。

PowerPAD包允許在一個制造操作中同時進行裝配和熱管理。在表面貼裝焊料操作過程中(引線焊接時),必須將熱焊盤焊接到封裝下方的銅區(qū)域。通過在這個銅區(qū)域內(nèi)使用熱路徑,熱量可以從封裝件傳導到接地層或其他散熱裝置中。始終需要將PowerPAD焊接到印刷電路板(PCB),即使在低功耗的應(yīng)用中也是如此。這在引線框架模架墊和PCB之間提供了必要的熱連接和機械連接。

電源板必須連接到設(shè)備上最負的電源電壓,即GNDA和GNDD。

1.準備帶有頂部蝕刻圖案的PCB。導線和熱墊都應(yīng)進行蝕刻。

2.在隔熱墊區(qū)域放置推薦的孔。HTSSOP-32 DAP封裝的理想熱接地尺寸和熱通孔模式(3x6)可在PowerPAD熱增強封裝(SLMA002)技術(shù)摘要中找到,可從以下網(wǎng)址下載:www.ti.com。這些孔的直徑應(yīng)為13密耳。保持它們很小,這樣焊料芯吸通過孔在回流焊期間不是問題。

3.可在熱墊區(qū)域外沿熱平面的任何位置放置額外的通孔。這有助于消散BUF16820 IC產(chǎn)生的熱量。這些額外的通孔可能比熱墊正下方直徑為13密耳的通孔大。它們可以更大,因為它們不在要焊接的熱墊區(qū)域;因此,芯吸不是問題。

4.將所有孔連接到與GND引腳電壓相同的內(nèi)部平面。

5.將這些孔連接到內(nèi)部平面時,不要使用典型的腹板或輪輻連接方法。網(wǎng)絡(luò)連接有一個高熱阻連接,有助于減緩焊接過程中的熱傳遞。這使得具有平面連接的通孔的焊接更加容易。然而,在這種應(yīng)用中,為了實現(xiàn)最有效的熱傳遞,需要低熱阻。因此,BUF16820 PowerPAD組件下的孔應(yīng)與內(nèi)部平面連接,并圍繞電鍍通孔的整個圓周進行完整連接。

6.頂部焊錫面罩應(yīng)使封裝端子和熱墊區(qū)域露出10個孔。底部的焊接面罩應(yīng)覆蓋熱焊盤區(qū)域的孔。這種掩蔽可以防止焊料在回流焊過程中被拉離熱焊盤區(qū)域。

7.將錫膏涂在外露的熱墊區(qū)域和所有IC端子上。

8.有了這些準備步驟,BUF16820集成電路被簡單地放置在適當?shù)奈恢茫⒆鳛槿魏螛藴实谋砻姘惭b組件運行焊料回流焊操作。此準備工作可使零件正確安裝。

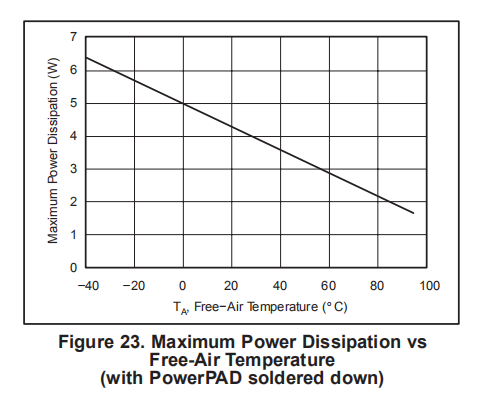

對于給定的θJA,最大功耗如圖23所示,并通過等式3計算:

其中:

PD=最大功耗(W)

TMAX=絕對最高結(jié)溫(+125°C)

TA=自由環(huán)境空氣溫度(°C)

θJA=θJC+θCA

θJC=從接頭到外殼的熱系數(shù)(°C/W)

θCA=從外殼到環(huán)境空氣的熱系數(shù)(°C/W)

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍牙WIFI模組、進口芯片替換國產(chǎn)降成本等解決方案,可承接項目開發(fā),以及元器件一站式采購服務(wù),類型有運放芯片、電源芯片、MO芯片、藍牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導體/HDSC_華大半導體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導體/TD_TECHCODE美國泰德半導體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1