功能應用程序

•12位雙傳輸DAC

•200 MSPS更新率

•單電源:3.0 V-3.6 V

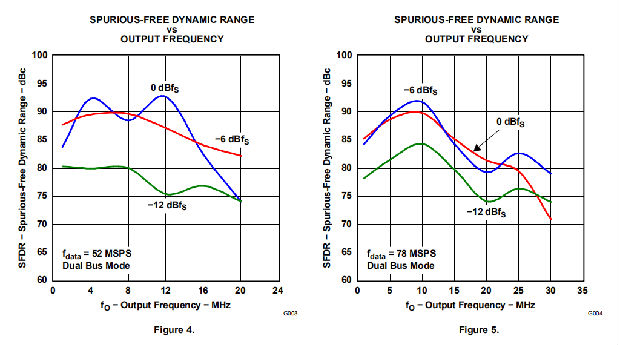

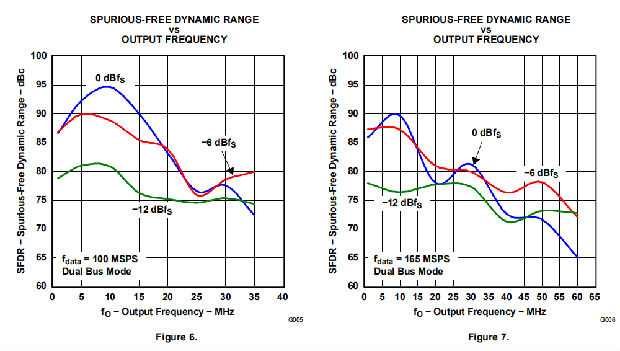

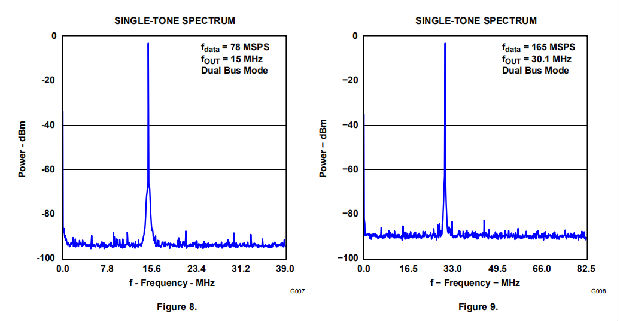

•高SFDR:85 dBc,5 MHz

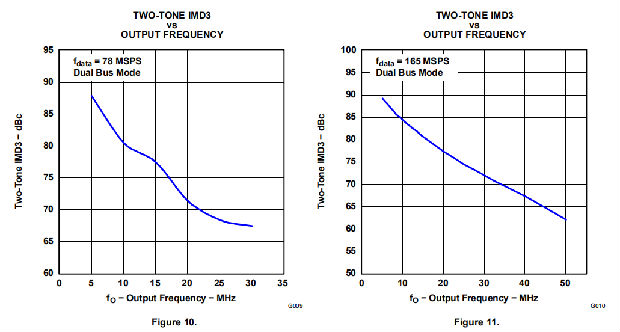

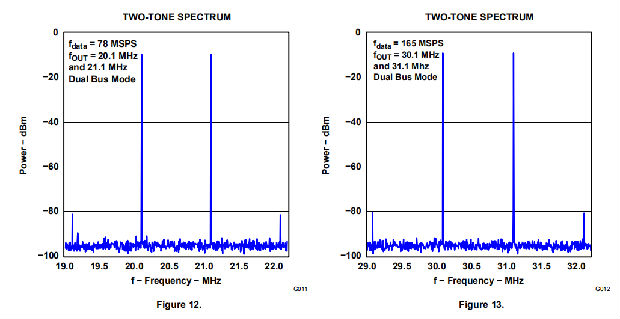

•高IMD3:78 dBc,15.1和16.1 MHz

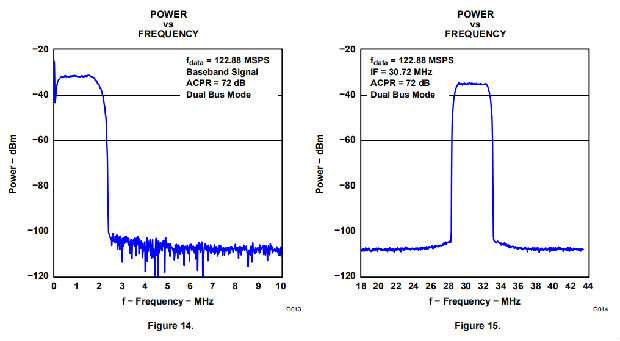

•WCDMA ACLR:30.72 MHz時為70 dB

•獨立或單電阻增益控制

•雙數據或交叉數據

•片上1.2-V基準

•低功率:330兆瓦

•斷電模式:15兆瓦

•包裝:48針TQFP

應用

•蜂窩基站收發(fā)站發(fā)射信道

–CDMA:W-CDMA、CDMA2000、IS-95

–TDMA:GSM、IS-136、EDGE/UWC-136

•醫(yī)療/測試儀器

任意波形發(fā)生器

•直接數字合成(DDS)

•電纜調制解調器終端系統(CMTS)

說明

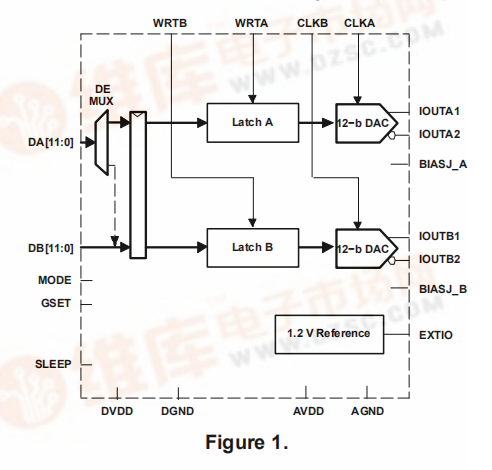

DAC5662是一個單片雙通道12位高速數模轉換器(DAC),具有片內基準電壓。

DAC5662的更新率高達200毫秒/秒,具有卓越的動態(tài)性能和緊密的增益和偏移匹配,這些特性使其適用于I/Q基帶或直接中頻通信應用。

每個DAC具有高阻抗差分電流輸出,適用于單端或差分模擬輸出配置。外部電阻器允許單獨或一起縮放每個DAC的滿標度輸出電流,通常在2 mA和20 mA之間。精確的片內基準電壓經過溫度補償,并提供穩(wěn)定的1.2V參考電壓。或者,可以使用外部參照。

DAC5662有兩個帶獨立時鐘和數據鎖存器的12位并行輸入端口。為了靈活性,DAC5662還支持在交織模式下操作時在一個端口上為每個DAC復用數據。

DAC5662專門設計用于帶有50Ω雙端接負載的差動變壓器耦合輸出。對于20毫安滿標度輸出電流,支持4:1阻抗比(產生4 dBm輸出功率)和1:1阻抗比變壓器(-2 dBm輸出功率)。

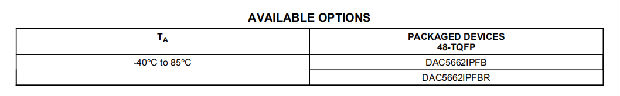

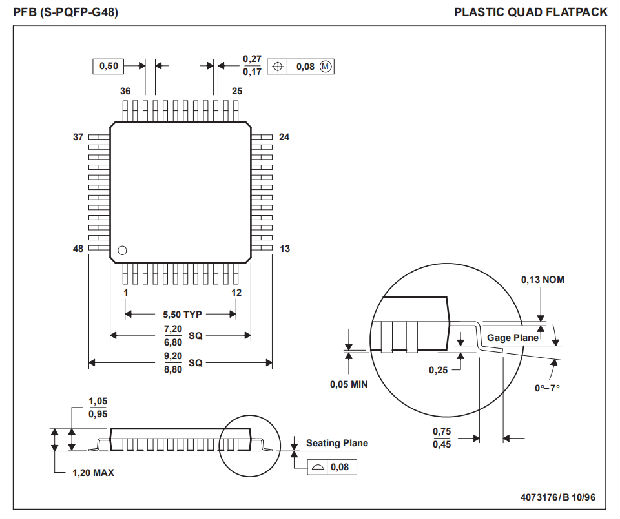

DAC5662提供48針薄方形扁平封裝(TQFP)。系列成員之間的引腳兼容性提供12位(DAC5662)和14位(DAC5672)分辨率。此外,DAC5662與DAC2902和AD9765雙DAC引腳兼容。該裝置的特點是可在-40°C至85°C的工業(yè)溫度范圍內工作。

典型特征

數字輸入和定時

數字輸入

DAC5662的數據輸入端口接受標準的正編碼,數據位D11是最高有效位(MSB)。轉換器輸出支持高達200毫秒/秒的時鐘速率。最佳性能通常是通過對稱的寫入和時鐘占空比實現的;但是,只要滿足定時規(guī)范,占空比可能會有所不同。類似地,設置和保持時間可以在其指定的限制內選擇。

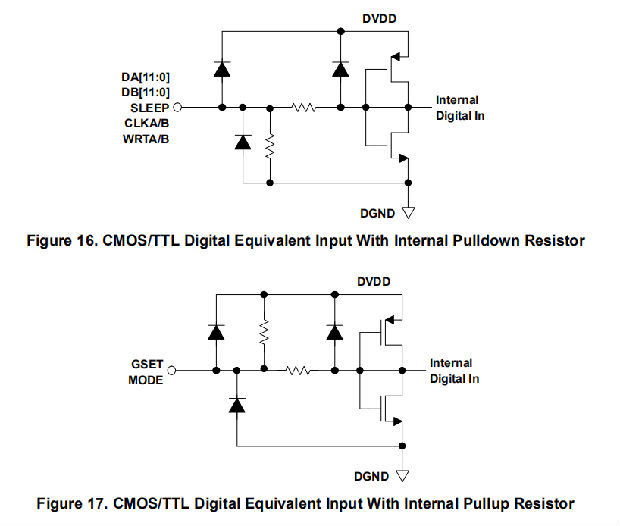

DAC5662的所有數字輸入都與CMOS兼容。圖16和圖17顯示了DAC5662的等效CMOS數字輸入的示意圖。12位數字數據輸入遵循偏移正二進制編碼方案。DAC5662設計用于在3V至3.6V的數字電源(DVDD)下工作。

輸入接口

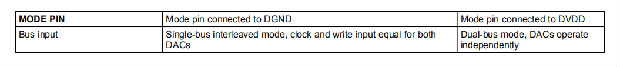

DAC5662具有模式引腳選擇的兩種工作模式,如下表所示:

•對于雙總線輸入模式,該設備基本上由兩個獨立的DAC組成。每個DAC都有自己獨立的數據輸入總線、時鐘輸入和數據寫入信號(數據鎖存)。

•在單總線交叉模式下,數據應在I通道輸入總線處交叉顯示。此模式下不使用Q通道輸入總線。時鐘和寫入輸入現在由兩個DAC共享。

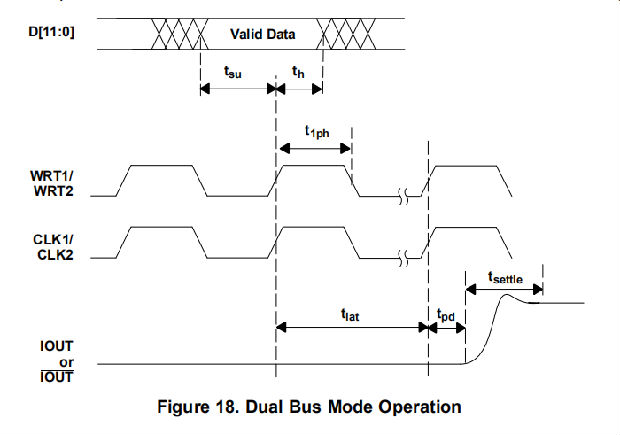

雙總線數據接口和定時

在雙總線模式下,模式引腳連接到DVD。DAC5662內的兩個轉換器通道由兩個獨立的12位并行數據端口組成。每個DAC通道由其自己的一組寫入(WRTA、WRTB)和時鐘(CLKA、CLKB)線控制。WRT線控制信道輸入鎖存器,CLK線路控制DAC鎖存器。數據首先由WRT線的上升沿加載到輸入鎖存器中。

內部數據傳輸需要正確的寫入和時鐘輸入序列,因為實際上兩個具有相同周期(但可能不同相位)的時鐘域被輸入到DAC5662。這是由時鐘上升沿和寫入輸入上升沿之間的最小時間要求來定義的。這實質上意味著CLK的上升沿必須同時出現或在WRT信號的上升沿之前。如果時鐘上升沿發(fā)生在寫入上升沿之后,則應保持至少2 ns的延遲。注意,當時鐘和寫入輸入被外部連接時,這些條件就滿足了。注意,所有的規(guī)格都是在WRT和CLK線路連接在一起的情況下測量的。

單總線交叉數據接口與時序

在單總線交錯模式下,模式引腳連接到DGND。圖19顯示了時序圖。在交錯模式下,I和Q通道共享寫入輸入(WRTIQ)和更新時鐘(CLKIQ和內部CLKDACIQ)。多路復用邏輯將I信道輸入總線上的輸入字定向到I信道輸入鎖存器(SELECTIQ高)或Q信道輸入鎖存器(SELECTIQ低)。當SELECTIQ為高時,通過再次向其輸入呈現鎖存器輸出數據來保留Q通道鎖存器中的數據值。當SELECTIQ較低時,通過向輸入端呈現鎖存器輸出數據來保留I信道鎖存器中的數據值。

在交織模式下,I信道輸入數據速率是DAC核心更新速率的兩倍。在雙總線模式下,保持寫入和時鐘輸入的正確順序很重要。邊緣觸發(fā)觸發(fā)器將LAND和Q通道輸入字鎖定在寫入輸入(WRTIQ)的上升沿。這些數據顯示在寫入輸入的下沿上的I和Q-DAC鎖存器。在將DAC5662時鐘輸入呈現給DAC鎖存器之前,將其除以系數2。

I和Q通道數據的正確配對由RESETIQ完成。在交錯模式下,時鐘輸入CLKIQ被二除,這將轉化為CLKIQ和CLKDACIQ上升沿之間的非確定性關系。然而,RESETIQ確保CLKDACIQ上升沿相對于DAC鎖存器輸入處的數據的正確位置被確定。當RESETIQ高時,CLKDACIQ被禁用(低)。

操作理論

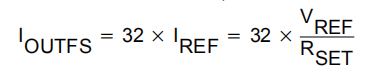

DAC5662的體系結構使用電流控制技術來實現快速切換和高更新率。單片DAC中的核心元件是一個分段電流源陣列,設計用于提供高達20毫安的滿量程輸出電流。內部解碼器在每次DAC更新時尋址差分電流開關,并通過將所有電流轉向輸出求和節(jié)點IOUT1和IOUT2形成相應的輸出電流。互補輸出提供差分輸出信號,與單端操作相比,通過減少偶數次諧波、共模信號(噪聲)和將峰值到峰值輸出信號擺幅增加兩倍來改善動態(tài)性能。

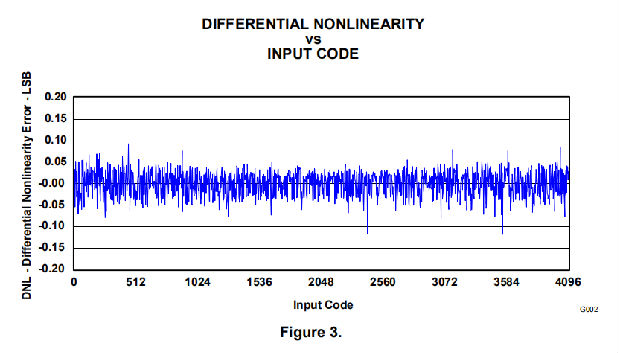

分段結構顯著降低了故障能量,提高了動態(tài)性能(SFDR)和DNL。電流輸出保持一個非常高的輸出阻抗大于300 kΩ。

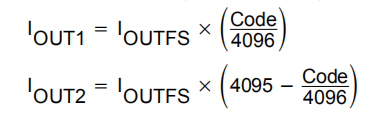

當GSET為高(單電阻模式)時,兩個DAC的滿標度輸出電流由內部參考電壓(1.2 V)和連接到BIASJđA的外部電阻器RSET的比率決定。當GSET較低時(雙電阻模式),每個DAC的滿標度輸出電流由內部參考電壓(1.2 V)和連接到BIASJ_A和BIASJ_B的獨立外部電阻器RSET的比率決定。所得IREF在內部乘以系數32,以產生有效的DAC輸出電流,其范圍可從2 mA到20 mA,具體取決于資源集。

DAC5662分為數字部分和模擬部分,每個部分通過其自己的電源引腳供電。數字部分包括邊緣觸發(fā)的輸入鎖存器和解碼器邏輯,而模擬部分包括電流源陣列及其相關開關和參考電路。

DAC傳遞函數

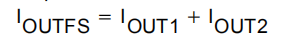

DAC5662中的每個DAC都有一組互補電流輸出,IOUT1和IOUT2。滿標度輸出電流IOUTFS是兩個互補輸出電流的總和:

單個輸出電流取決于DAC代碼,可以表示為:

其中Code是DAC數據輸入字的十進制表示。此外,IOUTFS是參考電流IREF的函數,它由參考電壓和外部設置電阻(RSET)決定。

在大多數情況下,互補輸出驅動電阻負載或終端變壓器。每個輸出端的信號電壓根據:

負載電阻值受DAC5662輸出符合性規(guī)范的限制。為保持規(guī)定的線性性能,IOUT1和IOUT2的電壓不應超過最大允許的合規(guī)范圍。

總差分輸出電壓為:

模擬輸出

DAC5662提供兩個互補電流輸出,IOUT1和IOUT2。圖20所示為表示模擬級輸出的簡化拓撲圖。IOUT1和IOUT2的輸出阻抗由差分開關、電流源和相關寄生電容并聯組合而成。

可能在兩個輸出端IOUT1和IOUT2處產生的信號電壓擺幅受到正負合規(guī)性的限制。負極限-1V是由CMOS工藝的擊穿電壓給出的,超過該限值會損害DAC5662的可靠性,甚至會造成永久性損壞。當滿標度輸出設置為20毫安時,正合規(guī)性等于1.2伏。請注意,對于選定的輸出電流IOUTFS=2毫安,合規(guī)范圍減小到約1伏。應注意,DAC5662的配置不超過柔度范圍,以避免失真性能和積分線性度的退化。

最佳失真性能通常在最大滿標度輸出信號限制在約0.5vpp的情況下實現。對于50Ω雙端接負載和20毫安滿標度輸出電流而言,就是這種情況。通過選擇合適的變壓器,同時保持IOUT1和IOUT2的最佳電壓水平,可以使各種負載適應DAC5662的輸出。此外,將差分輸出配置與變壓器結合使用將有助于實現優(yōu)良的失真性能。共模誤差,如偶數次諧波或噪聲,可以大大減少。在高輸出頻率的情況下尤其如此。

對于需要最佳失真和噪聲性能的應用,建議選擇20毫安的滿標度輸出。對于需要低功耗的應用,可以考慮2毫安的較低滿量程范圍,但可以容忍性能水平的輕微降低。

輸出配置

DAC5662的電流輸出允許多種配置。如前所述,利用轉換器的差分輸出產生最佳的動態(tài)性能。這種差分輸出電路可以由RF變壓器或差分放大器配置組成。變壓器配置是大多數交流耦合應用的理想配置,而運算放大器將適用于直流耦合配置。

對于需要單極輸出電壓的應用,可以考慮單端配置。將一個電阻從任一個輸出端接地,將輸出電流轉換為一個接地參考電壓信號。為了通過保持虛擬接地來改善直流線性,可以考慮I-To-V或運放配置。

變壓器差動

使用射頻變壓器提供了一種將差分輸出信號轉換為單端信號的方便方法,同時實現了優(yōu)異的動態(tài)性能。應根據輸出頻譜和阻抗要求仔細選擇合適的變壓器。

差分變壓器配置的優(yōu)點是顯著減少共模信號,從而改善在較寬頻率范圍內的動態(tài)性能。此外,通過選擇合適的阻抗比(繞組比),變壓器可用于提供最佳阻抗匹配,同時控制轉換器輸出的合規(guī)電壓。

圖21和圖22顯示了阻抗比分別為1:1和4:1的50Ω雙端接變壓器配置。注意,變壓器一次輸入的中心抽頭必須接地,以啟用直流電流。施加20毫安滿標度輸出電流將導致1:1變壓器的0.5-Vpp輸出和4:1變壓器的1-Vpp輸出。一般來說,1:1變壓器配置的輸出失真稍好,但4:1變壓器的輸出功率將高出6dB。

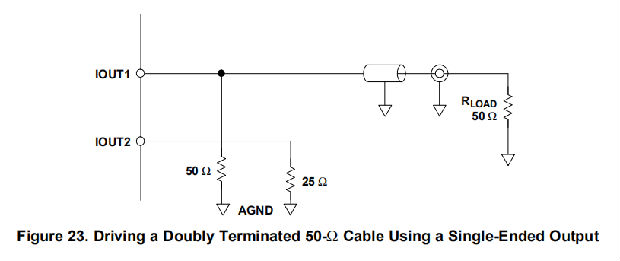

單端配置

圖23顯示了單端輸出配置,其中輸出電流IOUT1流入25Ω的等效負載電阻。節(jié)點IOUT2應連接到AGND或用25Ω的電阻器連接到AGND。當施加20毫安滿標度輸出電流時,25Ω的額定電阻負載產生1vpp的差分輸出擺幅。

參考操作

內部參考

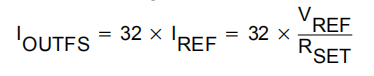

DAC5662具有片上參考電路,該電路包括1.2V帶隙基準和兩個控制放大器,每個DAC一個。DAC5662的滿標度輸出電流IOUTFS由參考電壓VREF和電阻器RSET的值決定。IOUTF可通過以下公式計算:

參考控制放大器作為一個V-I轉換器工作,產生一個參考電流IREF,IREF由VREF和RSET的比值決定(見等式9)。滿標度輸出電流IOUTFS是由IREF乘以一個固定因子32得到的。

使用內部參考時,2-kΩ電阻值可產生大約20 mA的滿標度輸出。應考慮公差為1%或更高的電阻器。選擇更高的值,輸出電流可以從20毫安調整到2毫安。出于降低總功耗、改善失真性能或觀察給定負載條件下的輸出順應性電壓限制的原因,在低于20毫安的輸出電流下操作DAC5662可能是可取的。

建議使用0.1μF或更高的陶瓷芯片電容器繞過EXTIO引腳。控制放大器內部補償,其小信號帶寬約為300 kHz。

外部參考

只需在EXTIO引腳上施加一個外部參考電壓,就可以禁用內部基準,在這種情況下,EXTIO引腳起到輸入的作用。對于需要更高精度和漂移性能或增加動態(tài)增益控制能力的應用,可以考慮使用外部基準。

雖然建議將0.1-μF電容器用于內部基準,但對于外部基準操作,電容器是可選的。參考輸入EXTIO具有高輸入阻抗(1 MΩ),可以很容易地由各種電源驅動。注意,外部基準的電壓范圍應保持在參考輸入的符合性范圍內。

增益設置選項

DAC5662上的滿標度輸出電流可以通過兩種方式設置:單獨為兩個DAC通道中的每一個通道設置,或者同時為兩個通道設置。對于獨立增益設置模式,GSET引腳(引腳42)必須低(即連接到AGND)。在這種模式下,需要兩個外部電阻器-一個RSET連接到BIASJ U A引腳(引腳44),另一個連接到BIASJ U B引腳(引腳41)。在這種配置中,用戶能夠靈活地獨立地設置和調整每個DAC的滿標度輸出電流,允許補償發(fā)射信號路徑內其他地方可能的增益不匹配。

或者,使GSET引腳高(即連接到AVDD),DAC5662切換到同步增益設置模式。現在,兩個DAC通道的滿標度輸出電流僅由一個連接到BIASJ U A引腳的外部RSET電阻器決定。BIASJ_2引腳處的電阻器可以被移除,但是這不是必需的,因為該引腳在這種模式下不起作用,并且電阻器對增益方程沒有影響。

睡眠模式

DAC5662具有斷電功能,如果不存在時鐘,可以使用該功能在指定的電源范圍內將總電源電流降低到3.5 mA以下。在休眠引腳上應用邏輯高啟動掉電模式,而邏輯低啟用正常操作。當保持不連接時,內部有源下拉電路可使轉換器正常工作。

機械數據

注:A、所有線性尺寸單位均為毫米。

B、 本圖紙如有更改,恕不另行通知。

C、 屬于JEDEC MS-026

安芯科創(chuàng)是一家國內芯片代理和國外品牌分銷的綜合服務商,公司提供芯片ic選型、藍牙WIFI模組、進口芯片替換國產降成本等解決方案,可承接項目開發(fā),以及元器件一站式采購服務,類型有運放芯片、電源芯片、MO芯片、藍牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍牙模組、WI模組及各類模組等電子元器件銷售。(關于元器件價格請咨詢在線客服黃經理:15382911663)

代理分銷品牌有:ADI_亞德諾半導體/ALTBRA_阿爾特拉/BARROT_百瑞互聯/BORN_伯恩半導體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導體/HDSC_華大半導體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術/NEXPERIA_安世半導體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導體/TD_TECHCODE美國泰德半導體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責聲明:部分圖文來源網絡,文章內容僅供參考,不構成投資建議,若內容有誤或涉及侵權可聯系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權所有 備案號:粵ICP備2023092210號-1