特征

■實(shí)時(shí)時(shí)鐘以BCD格式記錄數(shù)秒數(shù)

–bq4802Y:5-V操作

–bq4802LY:3.3-V操作

■外部SRAM的片上備用電池切換電路,帶非易失性控制

■備用模式下時(shí)鐘工作電流小于500毫安

■帶按鈕超控的微處理器復(fù)位

■具有可編程超時(shí)時(shí)間的獨(dú)立看門狗定時(shí)器

■電源故障中斷警告

■備用電池模式下的可編程時(shí)鐘報(bào)警中斷激活

■周期性可編程中斷

■電池電量低警告

■ 28針SOIC、TSSOP和SNAPHAT封裝選項(xiàng)

應(yīng)用

■電信基站

■服務(wù)器

■手持?jǐn)?shù)據(jù)采集設(shè)備

■醫(yī)療設(shè)備

■手持儀器

■測試設(shè)備

說明

bq4802Y/bq4802LY實(shí)時(shí)時(shí)鐘是一種低功耗微處理器外圍設(shè)備,集成了日時(shí)時(shí)鐘、基于世紀(jì)的日歷和CPU管理器,其封裝選項(xiàng)包括28針SOIC、TSSOP或SNAPHAT,需要bq48SH-28x6來完成兩件式模塊。bq4802Y/bq4802LY是傳真機(jī)、復(fù)印機(jī)、工業(yè)控制系統(tǒng)、銷售點(diǎn)終端、數(shù)據(jù)記錄器和計(jì)算機(jī)的理想選擇。

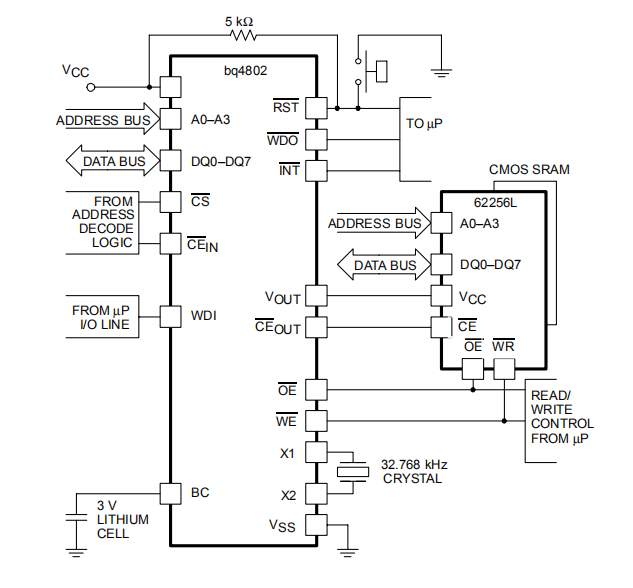

典型應(yīng)用

bq4802Y/bq4802LY為32.768 kHz石英晶體和3V備用電池提供直接連接。通過使用條件芯片使能輸出(CEOUT)和電池電壓輸出(VOUT)引腳,bq4802Y/bq4802LY可以寫保護(hù)并制作非易失性外部sram。備用單元為實(shí)時(shí)時(shí)鐘供電,并在沒有系統(tǒng)電壓的情況下維護(hù)SRAM信息。晶體和電池包含在模塊內(nèi),以實(shí)現(xiàn)更為集成的解決方案。

bq4802Y/bq4802LY包含一個(gè)溫度補(bǔ)償參考和比較器電路,用于監(jiān)控其電壓供應(yīng)的狀態(tài)。當(dāng)bq4802Y/bq4802LY檢測到超差情況時(shí),它會生成中斷警告,隨后微處理器復(fù)位。在VCC上升到允許范圍內(nèi)后,復(fù)位保持激活200毫秒,以允許電源供應(yīng)和處理器穩(wěn)定。復(fù)位功能還允許外部按鈕超控。

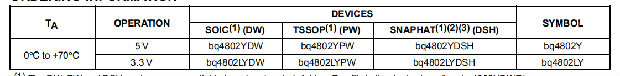

訂購信息

(1)、DW、PW和DSH包裝可提供磁帶和卷盤。在設(shè)備類型中添加一個(gè)R后綴(即bq4802YDWR)。

(2)、DSH軟件包僅提供磁帶。

(3)、應(yīng)訂購bq48SH–28x6以完成SNAPHAT模塊,并且3.3-V和5-V模塊的零件號相同。

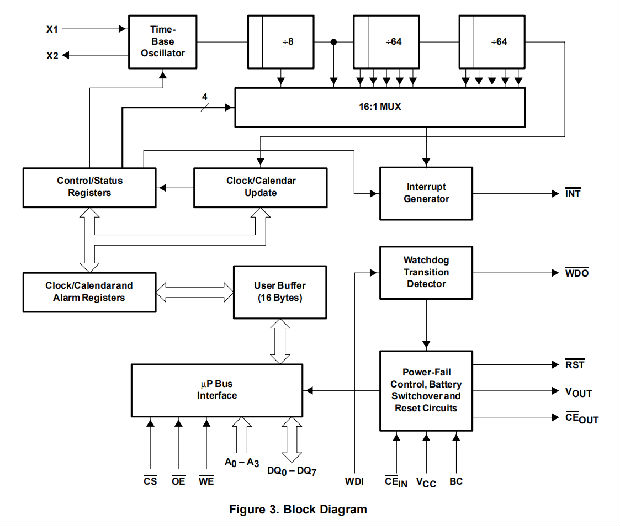

功能框圖

圖3是bq4802Y/bq4802LY的框圖。以下各節(jié)描述bq4802Y/bq4802LY功能操作,包括時(shí)鐘接口、數(shù)據(jù)保留模式、上電復(fù)位定時(shí)、看門狗定時(shí)器激活和中斷生成。

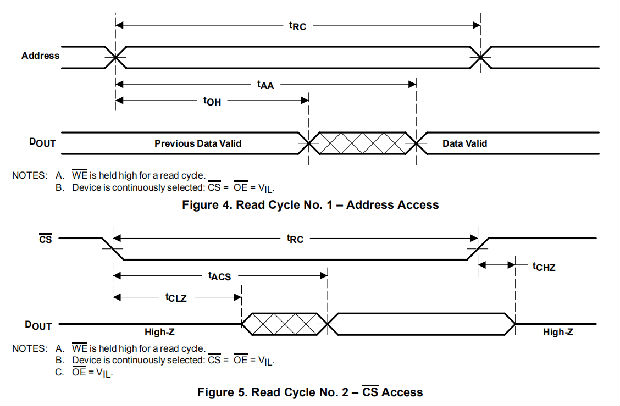

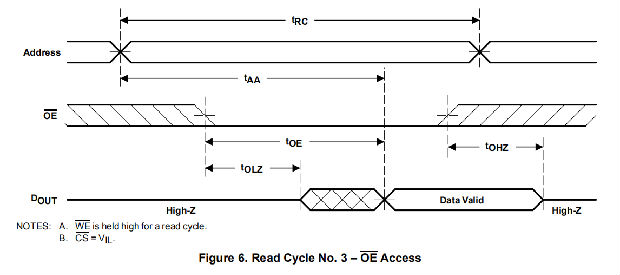

閱讀循環(huán)時(shí)序圖

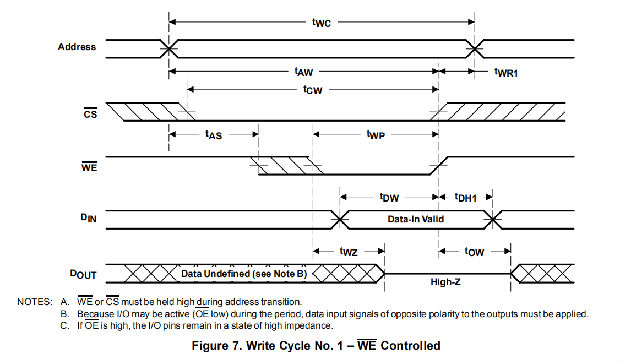

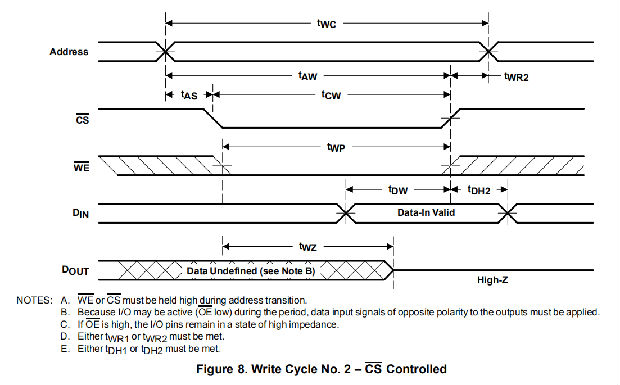

寫循環(huán)時(shí)序圖

功能描述

時(shí)鐘存儲器接口

bq4802Y/bq4802LY與標(biāo)準(zhǔn)SRAM具有相同的時(shí)鐘/日歷和控制信息接口。要對這些位置進(jìn)行讀寫操作,用戶必須將bq4802Y/bq4802LY置于適當(dāng)?shù)哪J剑M足定時(shí)要求。

讀取模式

每當(dāng)OE(輸出啟用)低且CS(芯片選擇)低時(shí),bq4802Y/bq4802LY處于讀取模式。由四個(gè)地址輸入指定的唯一地址定義了訪問16個(gè)時(shí)鐘/日歷字節(jié)中的哪一個(gè)。bq4802Y/bq4802LY使有效數(shù)據(jù)在tAA(地址訪問時(shí)間)內(nèi)在數(shù)據(jù)I/O引腳處可用。在最后一個(gè)地址輸入信號穩(wěn)定,并且滿足CS和OE(輸出啟用)訪問時(shí)間。如果未滿足CS和OE訪問時(shí)間,則在芯片選擇訪問時(shí)間(tACS)或輸出啟用訪問時(shí)間(tOE)后,有效數(shù)據(jù)可用。

CS和OE控制八個(gè)三態(tài)數(shù)據(jù)I/O信號的狀態(tài)。如果在tAA之前激活輸出,數(shù)據(jù)線將被驅(qū)動到一個(gè)不確定的狀態(tài),直到tAA。如果在CS和OE保持低位時(shí)更改地址輸入,則輸出數(shù)據(jù)在tOH(輸出數(shù)據(jù)保持時(shí)間)內(nèi)保持有效,但在下一次訪問地址之前不確定。

寫入模式

每當(dāng)WE和CS處于活動狀態(tài)時(shí),bq4802Y/bq4802LY都處于寫入模式。寫操作的開始是從WE或CS的下降沿引用的。寫入被WE或CS的早期上升沿終止。地址必須在整個(gè)周期內(nèi)保持有效。否則,在開始另一個(gè)讀或?qū)懷h(huán)之前,必須從CS返回至少tWR2或從WE返回tWR1的high。

在寫入結(jié)束之前,中的數(shù)據(jù)必須是有效的tDW,之后對于tDH1或tDH2仍然有效。在寫周期中,OE應(yīng)該保持在高電平,以避免總線爭用;盡管,如果輸出總線被CS和OE的低電平激活,那么在我們下降后,low on WE將禁用輸出tWZ。

讀時(shí)鐘

每隔一秒,用戶可訪問的時(shí)鐘/日歷位置會從內(nèi)部實(shí)時(shí)計(jì)數(shù)器同時(shí)更新。為防止在轉(zhuǎn)換過程中讀取數(shù)據(jù),應(yīng)停止對bq4802Y/bq4802LY時(shí)鐘寄存器的更新。通過設(shè)置控制寄存器E的更新傳輸禁止(UTI)位D3停止更新。只要UTI位為1,則禁止對用戶可訪問時(shí)鐘位置的更新。一旦通過讀取適當(dāng)?shù)臅r(shí)鐘存儲器位置來檢索凍結(jié)的時(shí)鐘信息,UTI位應(yīng)重置為0,以便允許從內(nèi)部計(jì)數(shù)器進(jìn)行更新。由于內(nèi)部計(jì)數(shù)器不會通過設(shè)置UTI位而暫停,因此讀取時(shí)鐘位置對時(shí)鐘精度沒有影響。一旦UTI位重置為0,內(nèi)部寄存器在一秒鐘內(nèi)以正確的時(shí)間更新用戶可訪問的寄存器。時(shí)鐘更新期間發(fā)出的暫停命令允許在凍結(jié)數(shù)據(jù)之前進(jìn)行更新。

設(shè)置時(shí)鐘

UTI位還必須用于設(shè)置bq4802Y/bq4802LY時(shí)鐘。一旦設(shè)置好,位置就可以用BCD格式的所需信息寫入。將UTI位重置為0將導(dǎo)致寫入的值傳輸?shù)絻?nèi)部時(shí)鐘計(jì)數(shù)器,并允許在一秒鐘內(nèi)恢復(fù)對用戶可訪問寄存器的更新。

停止和啟動時(shí)鐘振蕩器

bq4802Y/bq4802LY時(shí)鐘可編程為在部件進(jìn)入備用電池模式時(shí)關(guān)閉,方法是在斷電前將停止設(shè)置為0。如果使用bq4802Y/bq4802LY的電路板要在存儲器中花費(fèi)相當(dāng)長的時(shí)間,則可以使用停止位來保留一些電池容量。當(dāng)VCC降至VSO以下時(shí),STOP設(shè)置為1可保持時(shí)鐘運(yùn)行。當(dāng)VCC大于VSO時(shí),無論停止?fàn)顟B(tài)如何,bq4802Y/bq4802LY時(shí)鐘都會運(yùn)行。

斷電/上電循環(huán)

bq4802Y/bq4802LY連續(xù)監(jiān)控VCC是否超出公差。在電源故障期間,當(dāng)VCC低于VPFD時(shí),bq4802Y/bq4802LY寫保護(hù)時(shí)鐘和存儲寄存器。當(dāng)VCC小于VPFD且BC大于PFD時(shí),或當(dāng)VCC小于VBC且VBC小于VPFD時(shí),電源切換至BC。RTC操作和存儲數(shù)據(jù)由有效的備用能源維持。當(dāng)VCC高于VPFD時(shí),電源為VCC。在VCC上升到VPFD以上后,寫保護(hù)將持續(xù)tCSR時(shí)間。

外部CMOS靜態(tài)RAM由電池支持,使用來自bq4802Y/bq4802LY的VOUT和芯片啟用輸出引腳。當(dāng)電壓輸入VCC在電源故障期間下降時(shí),芯片啟用輸出CEOUT被強(qiáng)制停用,獨(dú)立于芯片啟用輸入CEIN。

當(dāng)VCC低于VPFD時(shí),此活動無條件寫入保護(hù)外部SRAM。如果在電源故障檢測期間正在對外部SRAM進(jìn)行內(nèi)存訪問,則在內(nèi)存被寫保護(hù)之前,該內(nèi)存周期將繼續(xù)完成。如果存儲器周期未在時(shí)間tWPT內(nèi)終止,則芯片使能輸出無條件地高電平驅(qū)動,對受控SRAM進(jìn)行寫保護(hù)。

當(dāng)電源繼續(xù)通過VPFD時(shí),內(nèi)部開關(guān)設(shè)備將VOUT強(qiáng)制轉(zhuǎn)換為外部備用能源。CEOUT被VOUT能源高舉。

在通電期間,當(dāng)VCC高于備用單元輸入電壓源VOUT時(shí),VOUT切換回主電源。如果bq4802Y/bq4802LY上的VPFD<VBC,則在VPFD處切換至主電源。在電源達(dá)到VPFD后,CEOUT保持非活動狀態(tài)的時(shí)間tCER(最長200毫秒),與CEIN輸入無關(guān),以允許處理器穩(wěn)定。

在功率有效運(yùn)行期間,CEIN輸入通過傳輸延遲小于12ns的CEOUT輸出。圖2顯示了外部RAM、電池和crystal的硬件連接。

在bq4802Y/bq4802LY上提供一個(gè)主備用能源輸入。BC輸入接受一個(gè)3V的主電池,通常是某種鋰化學(xué)物質(zhì)。因?yàn)閎q4802Y/bq4802LY提供蓄電池反向充電保護(hù),不需要二極管或限流電阻與電池串聯(lián)。在沒有有效數(shù)據(jù)可保留時(shí),為了防止電池耗盡,VOUT和CEOUT通過a的初始連接與BC內(nèi)部隔離電池。跟隨VCC在VPFD之上的第一次應(yīng)用,這種隔離被打破,備用單元為外部SRAM的VOUT和CEOUT供電。晶體應(yīng)盡可能靠近X1和X2,并符合電氣特性表晶體規(guī)格部分的規(guī)格。使用指定的晶體,bq4802Y/bq4802LY RTC在室溫下每月精確到1分鐘以內(nèi)。在沒有晶體的情況下,一個(gè)32.768-kHz的波形可以在X2接地的情況下輸入X1。電源和晶體集成在SNAPHAT模塊中。

上電復(fù)位

bq4802Y/bq4802LY提供上電復(fù)位功能,在VCC通過VPFD后,會將RST引腳拉低,并在tRST通電時(shí)保持低電平。在BC上的有效電池電壓下,RST對于VCC=VSS仍然有效。

按鈕復(fù)位

當(dāng)設(shè)備尚未處于復(fù)位循環(huán)時(shí),bq4802Y/bq4802LY還提供一個(gè)按鈕超控復(fù)位。當(dāng)RST引腳在被拉低1μs后被釋放,則RST在低位保持200 ms(典型)。

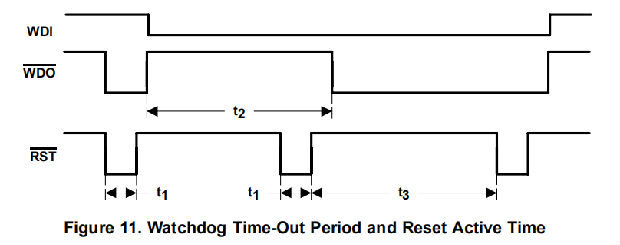

看門狗定時(shí)器

看門狗通過看門狗輸入(WDI)監(jiān)視微處理器活動。要使用看門狗功能,請將WDI連接到總線或微處理器I/O線路。如果WDI保持高或低的時(shí)間超過看門狗超時(shí)時(shí)間(默認(rèn)為1.5秒),bq4802Y/bq4802LY會斷言WDO和RST。

看門狗輸入

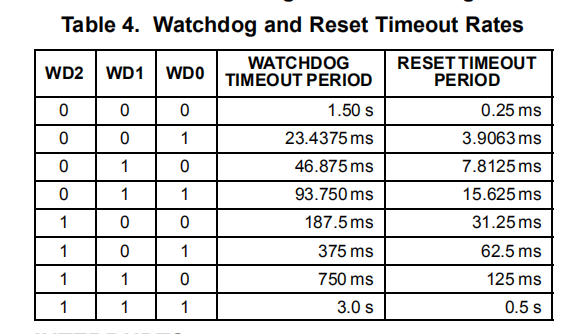

如果在看門狗期間看門狗輸入(WDI)發(fā)生狀態(tài)變化(從高到低、從低到高或最小100納秒脈沖),bq4802Y/bq4802LY重置看門狗定時(shí)器。看門狗超時(shí)由寄存器B中的WD0–WD2設(shè)置。bq4802Y/bq4802LY通過電源循環(huán)維護(hù)看門狗超時(shí)編程。WD0–WD2的默認(rèn)狀態(tài)(沒有有效的電池電量)是通電時(shí)的000或1.5秒。表3顯示了可編程的看門狗超時(shí)率。重置后的看門狗超時(shí)時(shí)間等于編程的看門狗超時(shí)。

要禁用看門狗功能,請保持WDI浮動。內(nèi)部電阻網(wǎng)絡(luò)(WDI處的100-kΩ等效阻抗)將WDI偏置至約1.6 V。內(nèi)部比較器檢測該電平并禁用看門狗定時(shí)器。當(dāng)V低于電源故障閾值時(shí),bq4802Y/bq4802LY將禁用看門狗功能,并將WDI從其內(nèi)部電阻網(wǎng)絡(luò)斷開,從而使其具有高阻抗。

看門狗輸出

如果在看門狗超時(shí)期間WDI處存在轉(zhuǎn)換或脈沖,則看門狗輸出(WDO)將保持高。當(dāng)VCC低于電源故障閾值、啟用電池備用模式或WDI開路時(shí),bq4802Y/bq4802LY禁用看門狗功能,WDO為邏輯高電平。在看門狗模式下,如果在看門狗超時(shí)期間WDI沒有發(fā)生轉(zhuǎn)換,則bq4802Y/bq4802LY將對重置超時(shí)時(shí)段t1重新斷言。WDO變低,并在WDI下一次轉(zhuǎn)換前保持低水平。如果WDI無限期地保持高或低,RST每3秒產(chǎn)生一次脈沖(t1秒寬)。圖11顯示了看門狗的計(jì)時(shí)。

中斷

bq4802Y/bq4802LY允許三個(gè)單獨(dú)選擇的中斷事件在INT引腳上生成一個(gè)中斷請求。這三個(gè)中斷事件是:

*周期性中斷,可編程為每30.5μs至500 ms發(fā)生一次。

*報(bào)警中斷,可編程為每秒一次到每月一次。

*電源故障中斷,可在bq4802Y/bq4802LY檢測到電源故障時(shí)啟用該中斷。

寄存器C(中斷寄存器)中的一個(gè)單獨(dú)的中斷啟用位啟用周期性、報(bào)警和電源故障中斷。當(dāng)一個(gè)事件發(fā)生時(shí),它在標(biāo)志寄存器寄存器寄存器D中的事件標(biāo)志位被設(shè)置。如果也設(shè)置了相應(yīng)的事件啟用位,則生成一個(gè)中斷請求。讀取標(biāo)志寄存器清除所有標(biāo)志位并使INT高阻抗。要重置標(biāo)志寄存器,bq4802Y/bq4802LY地址必須在寄存器D保持穩(wěn)定至少50納秒,以避免意外重置。

周期性中斷

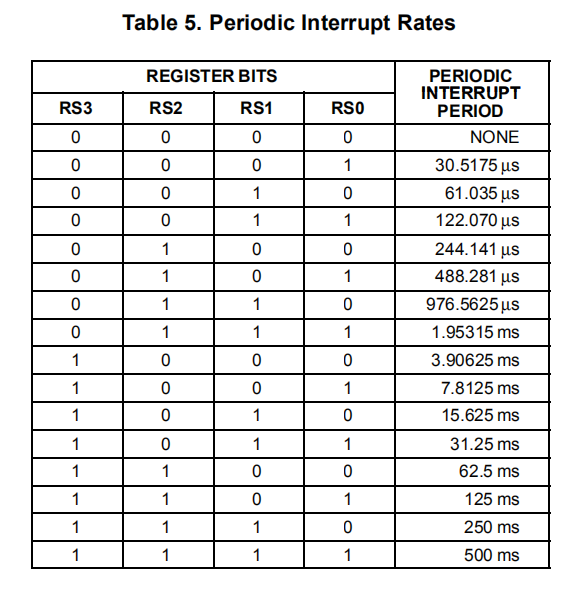

中斷寄存器中的位RS3–RS0編程周期性中斷的速率。用戶可以用兩種方式解釋中斷,或者通過輪詢或者通過設(shè)置PIE使INT在bq4802Y/bq4802LY設(shè)置周期標(biāo)志時(shí)變?yōu)榛顒印Wx取標(biāo)志寄存器將重置PF位并將INT返回到高阻抗?fàn)顟B(tài)。表5顯示了周期率。

報(bào)警中斷

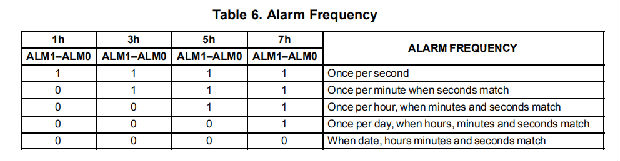

寄存器1、3、5和7對實(shí)時(shí)時(shí)鐘鬧鐘進(jìn)行編程。在每個(gè)更新周期中,bq4802Y/bq4802LY將時(shí)鐘寄存器中的日期、小時(shí)、分鐘和秒與相應(yīng)的報(bào)警寄存器進(jìn)行比較。如果在寄存器中找到一個(gè)對應(yīng)的標(biāo)志,則所有的AF標(biāo)志都是匹配的。如果使用AIE啟用報(bào)警中斷,則中斷請求為通過讀取標(biāo)志寄存器清除警報(bào)條件。ALM1–ALM0在報(bào)警寄存器中,屏蔽每個(gè)報(bào)警比較字節(jié)。將ALM1(D7)和ALM0(D6)設(shè)置為1將屏蔽報(bào)警字節(jié)。根據(jù)表6,報(bào)警字節(jié)屏蔽可用于選擇報(bào)警中斷的頻率。當(dāng)bq4802Y/bq4802LY處于電池備份模式時(shí),通過在中斷寄存器中設(shè)置ABE,可以激活報(bào)警中斷。

正常情況下,INT引腳在電池期間會出現(xiàn)高阻抗備份。在設(shè)置ABE的情況下,如果出現(xiàn)報(bào)警條件并且設(shè)置了AIE位,則INT被驅(qū)動為低電平。

電源-故障中斷

當(dāng)VCC下降到電源故障檢測點(diǎn)時(shí),設(shè)置電源故障標(biāo)志PWRF。如果還設(shè)置了電源故障中斷啟用位(PWRIE),則斷言INT低。那個(gè)電源故障中斷發(fā)生在bq4802Y/bq4802LY生成重置并取消選擇之前。

電池電量低警告

bq4802Y/bq4802LY在通電時(shí)檢查電池。當(dāng)電池電壓約為2.1 V時(shí),標(biāo)志寄存器中的電池有效標(biāo)志BVF被設(shè)置為0,表示時(shí)鐘和RAM數(shù)據(jù)可能無效。

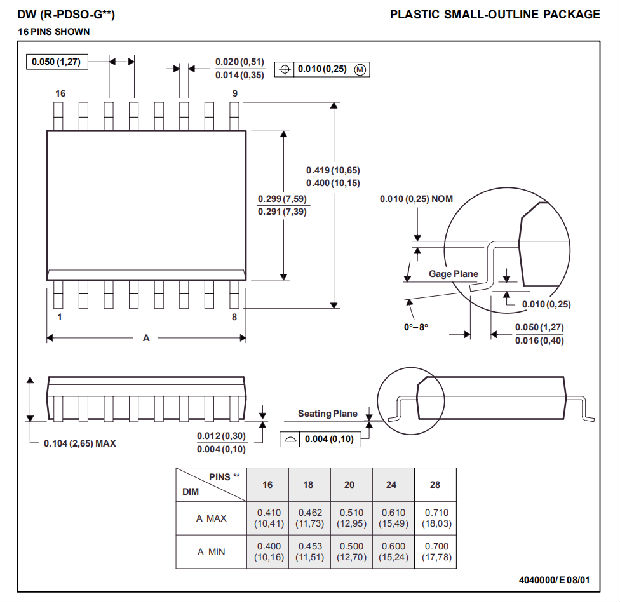

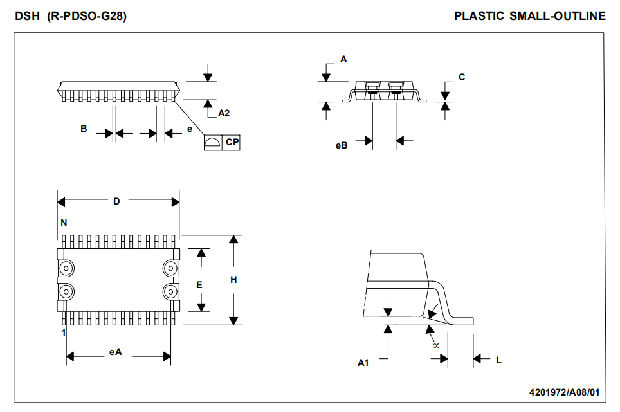

機(jī)械數(shù)據(jù)

注:A、全部線性尺寸單位為英寸(毫米)。

B、 本圖紙如有更改,恕不另行通知。

C、 主體尺寸不包括不超過0.006(0.15)的模具飛邊或突出物。

D、 屬于JEDEC MS-013。

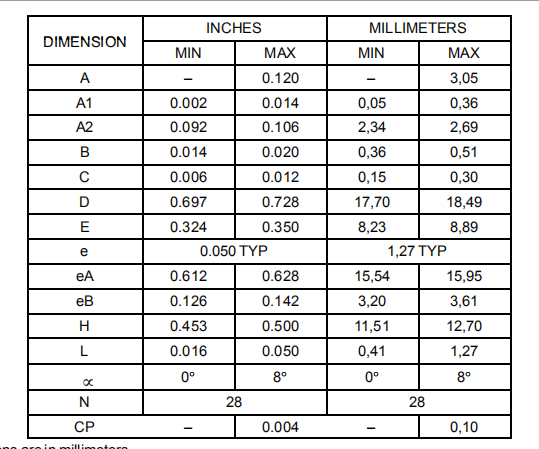

注:A、所有線性尺寸單位均為毫米。

B、 本圖紙如有更改,恕不另行通知。

C、 主體尺寸不包括不超過0.15的模具飛邊或突出物。

D、 屬于JEDEC MO-153。

注:A、全部線性尺寸單位為毫米。

B、 本圖紙如有更改,恕不另行通知。

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國產(chǎn)降成本等解決方案,可承接項(xiàng)目開發(fā),以及元器件一站式采購服務(wù),類型有運(yùn)放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價(jià)格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1