特征

■V2TM控制拓?fù)?/p>

■雙N通道設(shè)計

■125ns控制器瞬態(tài)響應(yīng)

■超過1Mhz運行

■公差為1%的5位DAC

■具有內(nèi)部延遲的功率良好輸出

■可調(diào)Hiccup模式過電流保護(hù)

■完整的奔騰II系統(tǒng)只需要21個組件

■5V和12V操作

■自適應(yīng)電壓定位

■遙感能力

■均流能力

■VCC監(jiān)視器

■過壓保護(hù)(OVP)

■可編程軟啟動

■200ns脈寬調(diào)制消隱

■65ns場效應(yīng)晶體管非重疊

■40ns閘門升降時間(3.3nF負(fù)載)

說明

CS5166是一個同步雙NFET降壓調(diào)節(jié)器控制器。它旨在激發(fā)最新高性能CPU的核心邏輯。它使用V2TM控制方法來實現(xiàn)最快的瞬態(tài)響應(yīng)和最佳的整體調(diào)節(jié)。它包含許多附加功能,以確保CPU和電源系統(tǒng)的正常運行和保護(hù)。CS5166提供了業(yè)界集成度最高的解決方案,最大限度地減少了外部組件數(shù)量、解決方案總規(guī)模和成本。

CS5166是專門為英特爾奔騰II處理器設(shè)計的,它包括以下功能:5位DAC,1%的容差,功率良好的輸出,可調(diào)hiccup模式過流保護(hù),VCC監(jiān)視器,軟啟動,自適應(yīng)電壓定位,過壓保護(hù),遠(yuǎn)程感應(yīng)和均流能力。

CS5166將在4.15至14V的電壓范圍內(nèi)工作,并提供16導(dǎo)聯(lián)寬體表面安裝封裝。

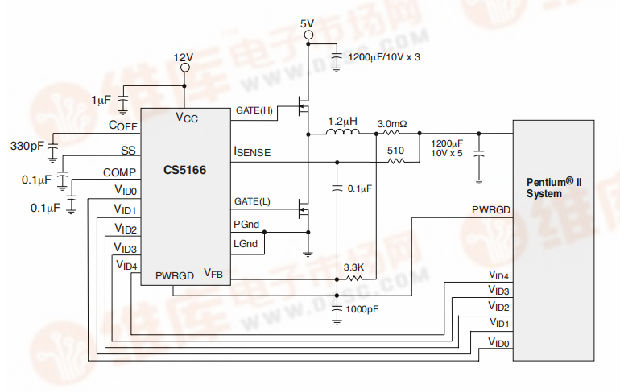

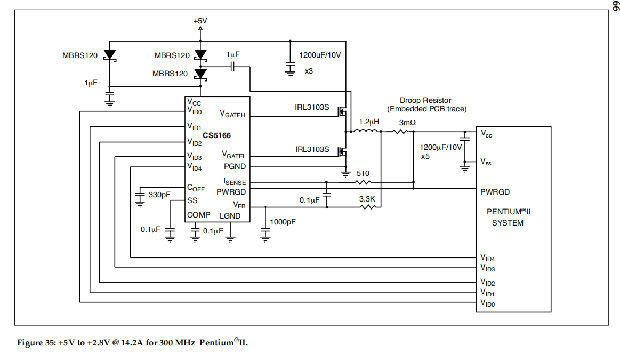

應(yīng)用程序圖

300MHz奔騰II在14.2A時為5V至2.8V

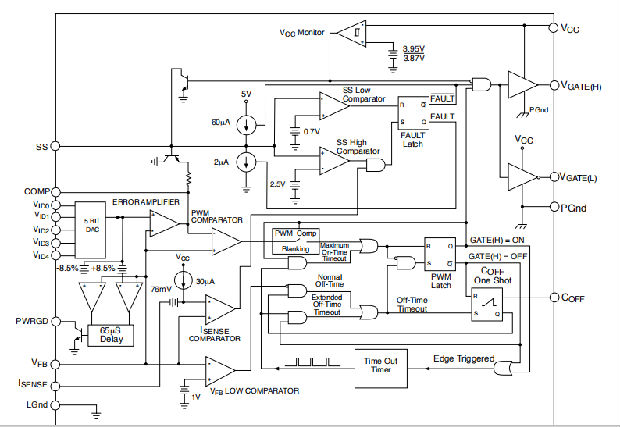

方塊圖

操作理論

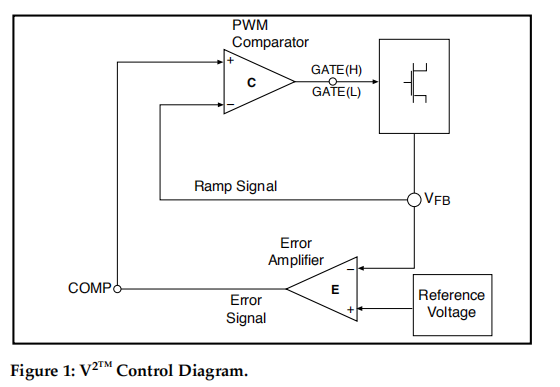

V2TM控制方法

V2TM控制方法使用由輸出電容器的ESR產(chǎn)生的斜坡信號。這個斜坡與通過主電感器的交流電流成比例,并被直流輸出電壓的值抵消。由于斜坡信號是由輸出電壓本身產(chǎn)生的,因此這種控制方案固有地補償線路或負(fù)載條件的變化。該控制方案不同于傳統(tǒng)的技術(shù),如電壓模式,它產(chǎn)生一個人工斜坡,電流模式,產(chǎn)生一個斜坡電感電流。

V2TM控制方法如圖1所示。輸出電壓用于產(chǎn)生誤差信號和斜坡信號。由于斜坡信號只是輸出電壓,所以它會受到輸出中的任何變化的影響,而不管這種變化的來源是什么。斜坡信號還包含輸出電壓的直流部分,允許控制電路根據(jù)需要將主開關(guān)驅(qū)動到0%或100%的占空比。

線路電壓的變化會改變電感器中的電流斜坡,從而影響斜坡信號,從而使V2TM控制方案補償占空比。由于電感器電流的變化會改變斜坡信號,因此V2TM控制方案在線路瞬態(tài)響應(yīng)方面具有相同的優(yōu)勢。

負(fù)載電流的變化會對輸出電壓產(chǎn)生影響,從而改變斜坡信號。加載步驟立即改變比較器輸出的狀態(tài),比較器輸出控制主開關(guān)。負(fù)載瞬態(tài)響應(yīng)僅由比較器響應(yīng)時間和主開關(guān)的轉(zhuǎn)換速度決定。與傳統(tǒng)控制方法一樣,輸出負(fù)載階躍的反應(yīng)時間與誤差信號環(huán)的交叉頻率無關(guān)。

由于瞬態(tài)響應(yīng)由斜坡信號環(huán)路處理,因此誤差信號環(huán)路可能具有較低的交叉頻率。這種“慢”反饋回路的主要目的是提供直流精度。噪聲抗擾度顯著提高,因為誤差放大器的帶寬可以在低頻下滾動。增強的抗擾度提高了對輸出電壓的遙感,因為與長反饋軌跡相關(guān)的噪聲可以有效地過濾。

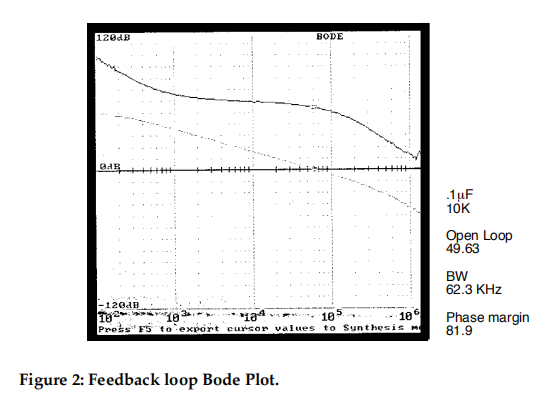

圖2中的Bode圖顯示了CS5166單極反饋回路的增益和相位裕度,并展示了基于CS5166的調(diào)節(jié)器的整體穩(wěn)定性。

由于有兩個獨立的電壓回路,線路和負(fù)荷調(diào)節(jié)得到了極大的改善。電壓模式控制器依靠誤差信號的變化來補償線路或負(fù)載電壓的偏差。誤差信號的這種變化導(dǎo)致輸出電壓與誤差放大器的增益相對應(yīng),誤差放大器通常被指定為線路和負(fù)載調(diào)節(jié)。

電流模式控制器在線路電壓偏差下保持固定的誤差信號,因為斜坡信號的斜率改變,但是仍然依賴誤差信號的變化來獲得負(fù)載偏差。V2TM控制方法為線路和負(fù)載變化保持固定的誤差信號,因為斜坡信號受線路和負(fù)載的影響。

恒定關(guān)閉時間

為了最大限度地提高瞬態(tài)響應(yīng),CS5166使用了一個恒定的關(guān)閉時間方法來控制輸出脈沖的速率。在正常運行期間,高壓側(cè)開關(guān)的斷開時間在由關(guān)斷電容器設(shè)置的固定時間后終止。為了保持調(diào)節(jié),V2TM控制回路改變接通時間。PWM比較器監(jiān)測輸出電壓斜坡,并終止開關(guān)接通時間。

恒定的關(guān)閉時間有很多優(yōu)點。當(dāng)響應(yīng)瞬態(tài)條件時,開關(guān)占空比可以逐脈沖從0調(diào)整到100%。0%和100%的占空比運行都可以長時間保持,以響應(yīng)負(fù)載或線路瞬態(tài)。避免了PWM斜率補償,以避免高占空比下的次諧波振蕩。

通電時間由內(nèi)部30μs(典型)定時器限制,最大限度地減少了對電源部件的壓力。

可編程輸出

CS5166旨在提供兩種方法來編程電源的輸出電壓。一個五位板載數(shù)模轉(zhuǎn)換器(DAC)用于編程兩個不同范圍內(nèi)的輸出電壓。

可編程輸出

CS5166設(shè)計用于提供兩種編程電源輸出電壓的方法。一個五位板載數(shù)模轉(zhuǎn)換器(DAC)用于編程兩個不同范圍內(nèi)的輸出電壓。

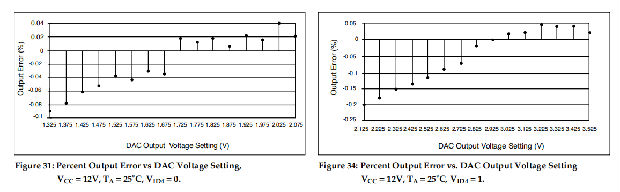

第一個范圍是2.125V到3.525V,步長為100mV,第二個范圍是1.325V到2.075V,步長為50mV,具體取決于數(shù)字輸入代碼。如果所有五位都保持打開,CS5166進(jìn)入調(diào)整模式。在調(diào)整模式下,設(shè)計者可以像傳統(tǒng)控制器一樣,通過使用電阻分壓器反饋到VFB引腳來選擇任何輸出電壓。專為滿足英特爾奔騰或CS5166規(guī)格而設(shè)計。

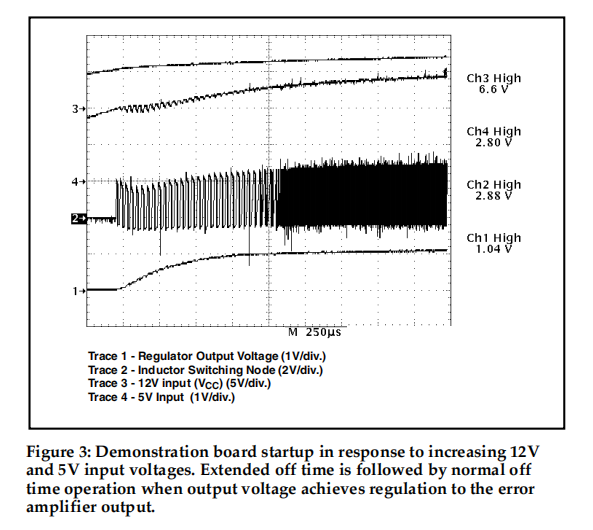

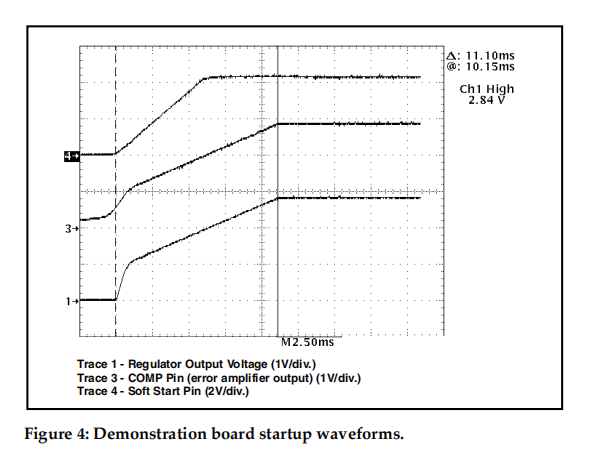

啟動

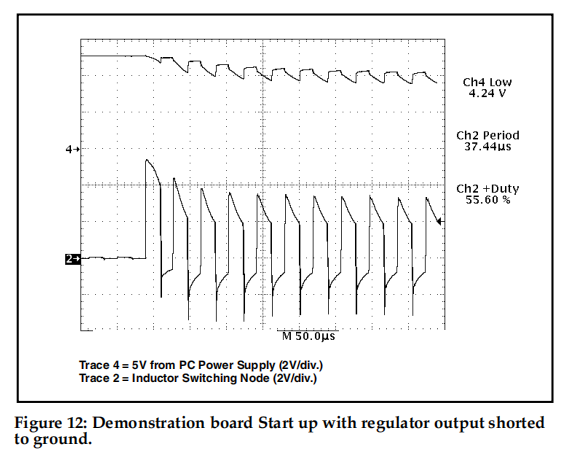

直到VCC電源引腳上的電壓超過3.95V監(jiān)視器閾值,軟啟動和柵極引腳保持在低水平。故障閂鎖復(fù)位(無故障狀態(tài))。誤差放大器(補償)的輸出被補償鉗拉高到1V。當(dāng)VCC引腳超過監(jiān)視器閾值時,門(H)輸出被激活,軟啟動電容器開始充電。門(H)輸出將保持打開,啟用NFET開關(guān),直到由PWM比較器或最大接通時間計時器終止。

如果在調(diào)節(jié)器輸出電壓達(dá)到1V電平之前超過最大接通時間,脈沖終止。在延長的關(guān)閉時間內(nèi),柵極(H)引腳驅(qū)動低電平,柵極(L)引腳驅(qū)動高電平。此時間由超時計時器設(shè)置,大約等于最大接通時間,從而產(chǎn)生50%的占空比。然后,柵極(L)引腳將驅(qū)動低電平,柵極(H)引腳將驅(qū)動高電平,并且循環(huán)重復(fù)。

當(dāng)調(diào)節(jié)器輸出電壓達(dá)到在補償引腳處預(yù)先發(fā)送的1V電平時,調(diào)節(jié)已經(jīng)實現(xiàn),隨后將出現(xiàn)正常的關(guān)閉時間。PWM比較器終端用于開關(guān)接通時間,關(guān)斷時間由COFF設(shè)置電容器。V2TM控制回路將根據(jù)需要調(diào)整開關(guān)占空比,以確保調(diào)節(jié)器輸出電壓跟蹤誤差放大器的輸出。

軟啟動和補償電容器將充電至最終水平,提供調(diào)節(jié)器輸出的受控開啟。調(diào)節(jié)器的開啟時間由補償電容器充電到其最終值來決定。其電壓受軟起動補償鉗位和軟起動引腳上的電壓限制。

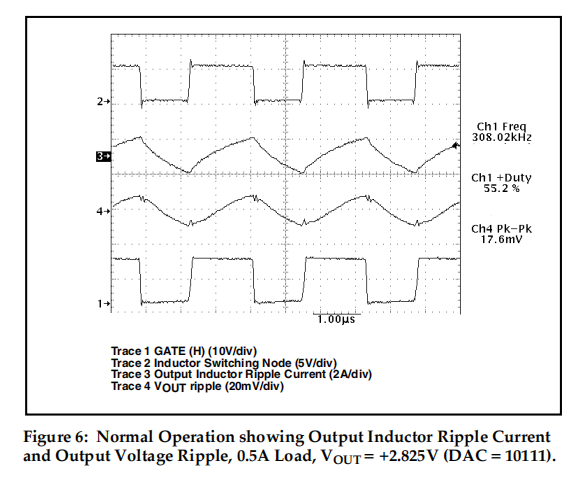

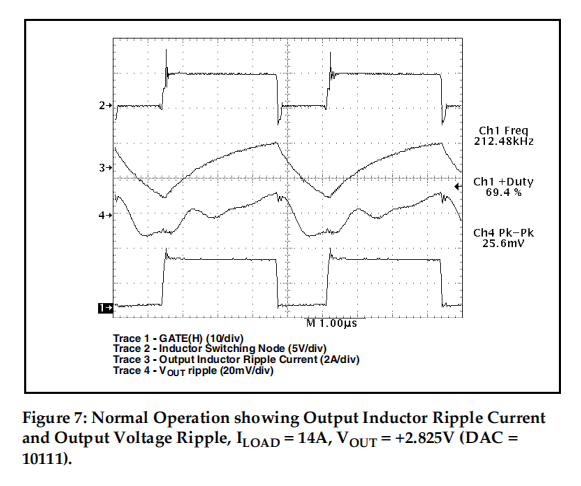

正常運行

在正常運行期間,關(guān)閉時間是恒定的,由COFF電容器設(shè)置。通電時間由V2TM控制回路調(diào)節(jié),以保持調(diào)節(jié)。這會導(dǎo)致調(diào)節(jié)器開關(guān)頻率、占空比和輸出紋波隨負(fù)載和線路輸出電壓紋波將由電感器跳閘電流和輸出電容器的ESR決定(見圖6和圖7)。

瞬態(tài)響應(yīng)

CS5166 V2TM控制回路的150ns反應(yīng)時間對輸入電壓或輸出電流的變化提供了前所未有的瞬態(tài)響應(yīng)。提供一個脈沖一個脈沖地調(diào)整占空比,以快速將電感器電流提升到所需水平。由于電感器電流不能瞬時改變,因此在需要轉(zhuǎn)換電感器電流的時間內(nèi),輸出電容器維持調(diào)節(jié)。

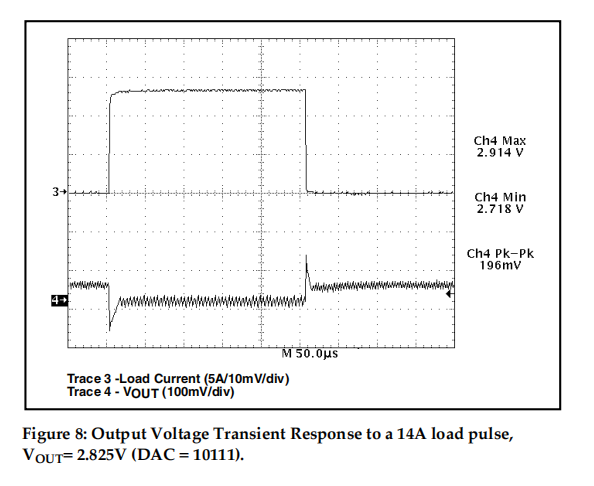

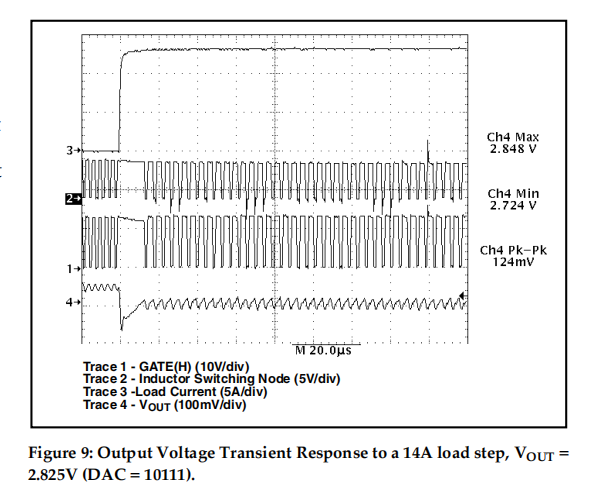

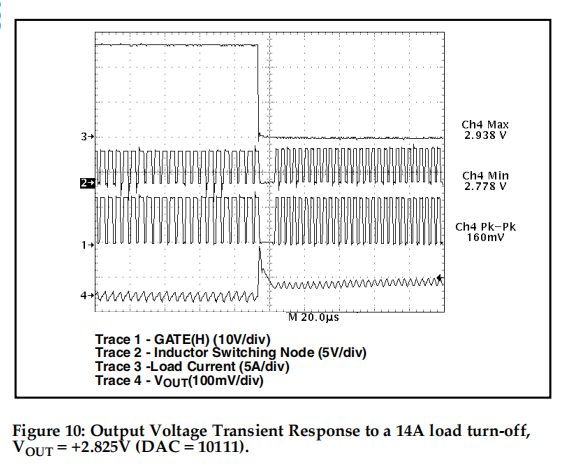

通過稱為“自適應(yīng)電壓定位”的功能,整體負(fù)載瞬態(tài)響應(yīng)得到進(jìn)一步改善。這種技術(shù)預(yù)先定位輸出電容器的電壓,以減少負(fù)載變化期間的總輸出電壓偏移。

保持公差為1%允許誤差放大器的參考電壓在不影響直流精度的情況下達(dá)到+25mV高。一個“下垂電阻器”,通過一個PC板軌跡實現(xiàn),將誤差電流反饋引腳(VFB)連接到輸出電容器和負(fù)載,并攜帶輸出電流。在無負(fù)載的情況下,電阻上沒有直流電壓降,產(chǎn)生跟蹤誤差電流的輸出電壓,包括+25mV偏移。當(dāng)滿負(fù)荷電流被輸送時,電阻上會產(chǎn)生50mV的壓降。這導(dǎo)致輸出電壓偏移25毫伏低。

自適應(yīng)電壓定位的結(jié)果是,在達(dá)到輸出電壓規(guī)范限值之前,為負(fù)載瞬態(tài)提供了額外的裕度。當(dāng)負(fù)載電流突然從其最小水平增加時,輸出電容器被預(yù)先定位為+25mV。相反,當(dāng)負(fù)載電流突然從其最大水平下降時,輸出電容器被預(yù)先定位為-25mV(見圖8、9和10)。為了獲得最佳的瞬態(tài)響應(yīng),通常使用一些高頻和大容量輸出電容器的組合。

如果在響應(yīng)負(fù)載電流突然增加時超過了最大接通時間,則會出現(xiàn)正常的斷開時間,以防止輸出電感器飽和。

電源排序

CS5166提供固有的保護(hù),不受未定義的啟動條件的影響,無論12V和5V供電順序如何。12V和5V電源的開啟轉(zhuǎn)換率可以在很大范圍內(nèi)變化,而不會影響輸出電壓或?qū)祲赫{(diào)節(jié)器造成不利影響。

保護(hù)和監(jiān)控功能

過電流保護(hù)

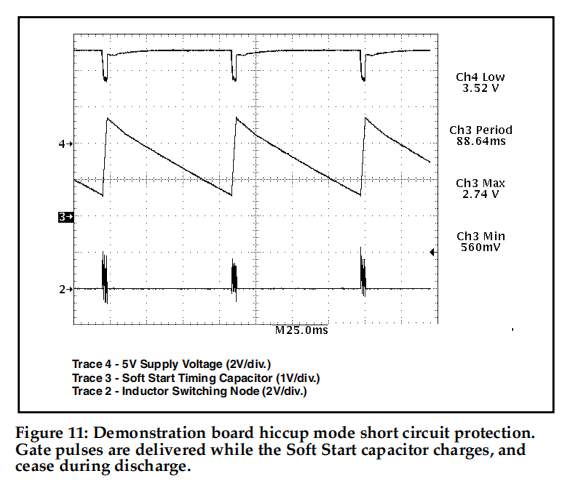

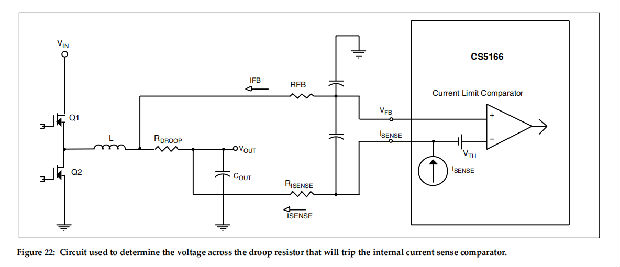

提供了一種無損耗的小干擾模式限流保護(hù)功能,只需要軟啟動電容器即可實現(xiàn)。CS5166通過使用內(nèi)部電流檢測比較器,通過“降速”電阻器感測電流,提供過電流保護(hù)。比較器將此電壓降與76mV(典型)的內(nèi)部參考電壓進(jìn)行比較。

如果“降速”電阻器上的電壓降超過此閾值,電流感應(yīng)比較器允許設(shè)置故障鎖存器。這會導(dǎo)致調(diào)節(jié)器停止切換。在這種過電流情況下,CS5166在軟啟動電容器通過2μa電流源緩慢放電的時間內(nèi)保持關(guān)閉,直到達(dá)到其較低的0.7V閾值。

此時,調(diào)節(jié)器通過向兩個fet發(fā)送短的柵極脈沖來嘗試正常重啟。CS5166最初將以50%占空比的延長關(guān)閉時間模式運行,而軟啟動電容器則以60μa的充電電流充電。當(dāng)軟啟動電容器充電到其上限2.7V時,門將打開。在過載條件下,軟啟動充放電電流比設(shè)置脈沖的占空比(2μA/60μA=3.3%),當(dāng)VFB小于1V時,實際占空比為延長關(guān)閉時間模式(1.65%)的一半。軟啟動中斷脈沖持續(xù)3ms,當(dāng)檢測到故障時,占空比重復(fù),否則恢復(fù)正常運行。

由于過電流情況持續(xù)存在,該保護(hù)方案可將調(diào)節(jié)器組件、輸入電源和PC板痕跡的熱應(yīng)力降至最低。過載解除后,故障鎖閂被清除,允許恢復(fù)正常操作。電流限制跳閘點可通過外部電阻器進(jìn)行調(diào)整,為用戶提供電流限制設(shè)定點的靈活性。

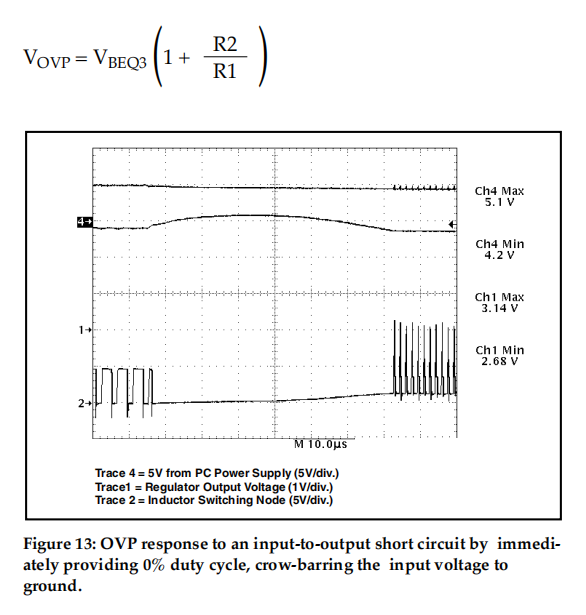

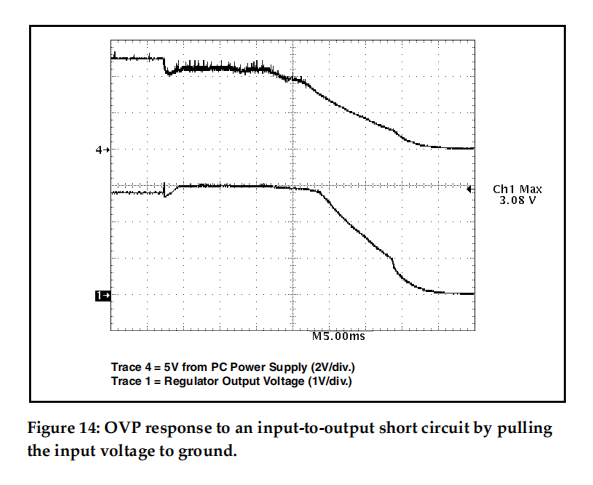

過電壓保護(hù)

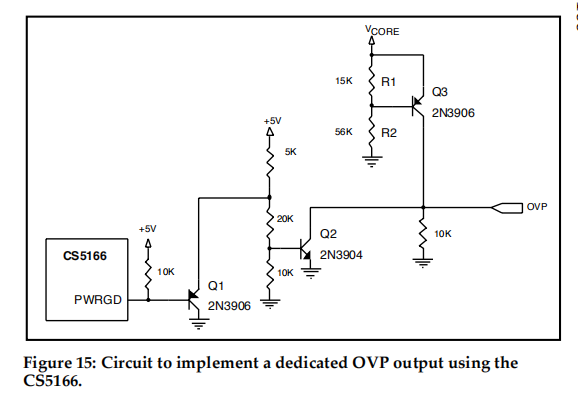

過電壓保護(hù)(OVP)是V2TM控制拓?fù)湔_\行的結(jié)果,不需要額外的外部組件。控制回路對100ns內(nèi)的過電壓條件做出響應(yīng),導(dǎo)致頂部MOSFET關(guān)閉,從而將調(diào)節(jié)器與其輸入電壓斷開。底部MOSFET隨后被激活,產(chǎn)生一個“撬桿”動作,以鉗制輸出電壓并防止對負(fù)載的損壞(見圖13和14)。調(diào)節(jié)器將保持此狀態(tài),直到過電壓條件停止或輸入電壓被拉低。底部FET和板跟蹤必須正確設(shè)計以實現(xiàn)OVP功能。如果需要專用的OVP輸出,可以使用圖15中的電路實現(xiàn)。在此圖中,如果輸出電壓(VCORE)超過特定DAC代碼設(shè)置的電壓的20%,OVP信號將變高(過壓條件)如果PWRGD較低。還要求過電壓條件至少在激活OVP信號的PWRGD延遲時間內(nèi)存在。圖15中顯示的電阻值適用于VDAC=+2.8V(DAC=10111)。VOVP(過電壓跳閘點)可使用以下等式進(jìn)行設(shè)置:

電源良好電路

電源良好引腳(引腳13)是一個開路集電極信號,符合TTL DC規(guī)格。當(dāng)調(diào)節(jié)器輸出電壓通常超過標(biāo)稱輸出電壓的±8.5%時,它被外部拉上,并被拉低(低于0.3V)。功率良好拉低前的最大輸出電壓偏差為±12%。

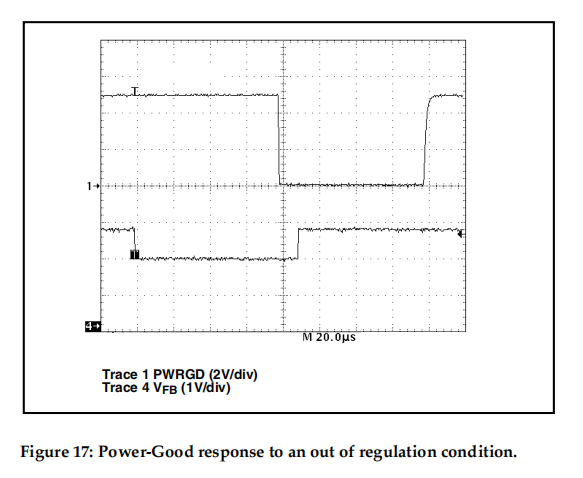

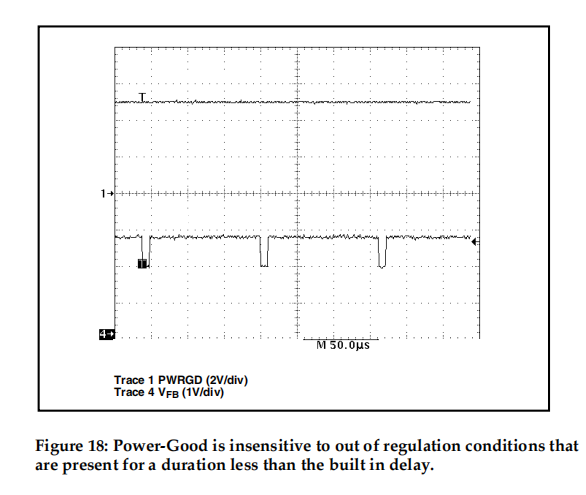

圖17顯示了穩(wěn)壓輸出電壓VFB和功率良好信號之間的關(guān)系。為了防止Power Good不必要地中斷CPU,CS5166有一個內(nèi)置的延遲,以防止VFB引腳處的噪聲切換到Power Good。內(nèi)部時間延遲設(shè)計為功耗良好時約為75微秒,恢復(fù)為65微秒。這使得功率良好信號對持續(xù)時間小于內(nèi)置延遲的不規(guī)則條件完全不敏感(見圖18)。

因此,在功率良好信號改變狀態(tài)之前,要求輸出電壓至少在內(nèi)置延遲時間內(nèi)達(dá)到不調(diào)節(jié)或處于調(diào)節(jié)水平。

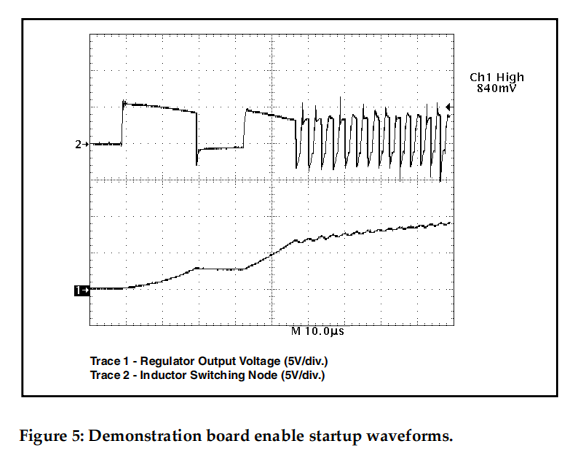

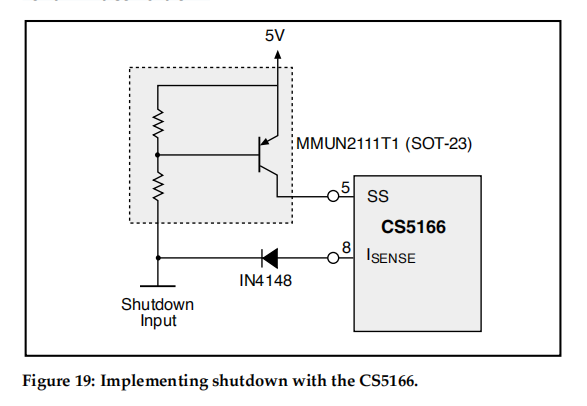

外部輸出使能電路

調(diào)節(jié)器的開/關(guān)控制可通過添加兩個額外的分立元件來實現(xiàn)(見圖19)。該電路通過將軟啟動引腳拉高,將ISENSE引腳拉低,模擬電流極限條件來運行。

選擇外部組件

CS5166降壓調(diào)節(jié)器可與各種外部電源元件一起使用,以優(yōu)化特定設(shè)計的成本和性能。以下信息可作為一般指南,以幫助選擇它們。

NFET功率晶體管

邏輯電平和標(biāo)準(zhǔn)場效應(yīng)晶體管都可以使用。參考設(shè)計從12V電源得到柵極驅(qū)動,12V電源通常在大多數(shù)計算機系統(tǒng)中可用,并利用邏輯級FET。電荷泵可以很容易地實現(xiàn)為僅支持5V的系統(tǒng)。多個場效應(yīng)晶體管可以并聯(lián),以減少損耗,提高效率和熱管理。

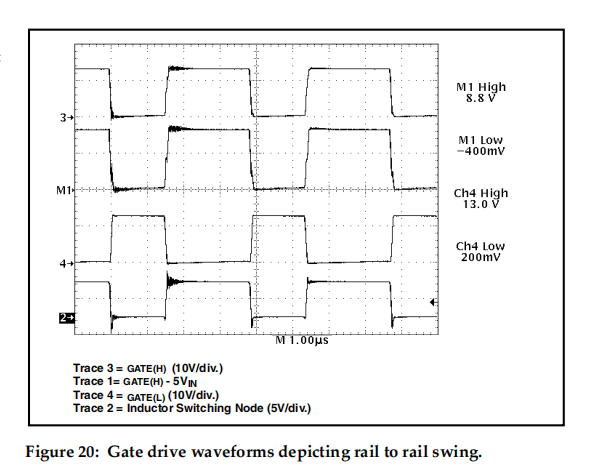

施加到FET柵極的電壓取決于所用的應(yīng)用電路。當(dāng)處于低狀態(tài)時,上下柵極驅(qū)動器輸出都被指定驅(qū)動到離地1.5V以內(nèi),在高狀態(tài)時驅(qū)動到各自偏置電源的2V以內(nèi)。實際上,由于FET柵極給控制器IC帶來的電容性負(fù)載引起的過沖,F(xiàn)ET門將被逐條驅(qū)動。對于使用VCC=12V和5V作為調(diào)節(jié)器輸出電流源的典型應(yīng)用,提供以下柵極驅(qū)動:

(見圖20)。

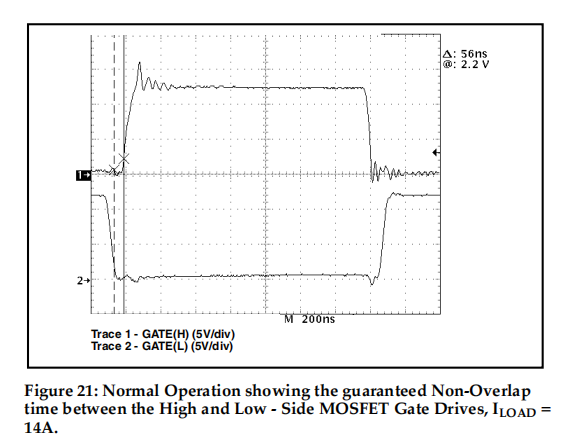

CS5166通過保證上下MOSFET柵極驅(qū)動脈沖之間典型的65ns不重疊(如圖21所示),提供外部NFET傳導(dǎo)時間的自適應(yīng)控制。這種特性消除了“穿透電流”的潛在災(zāi)難性影響,在這種情況下,兩個fet都會傳導(dǎo),導(dǎo)致過熱、自毀,并可能對處理器造成不可逆轉(zhuǎn)的損害。

場效應(yīng)管性能最重要的方面是RDSON,它影響調(diào)節(jié)器效率和FET熱管理要求。

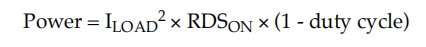

MOSFET消耗的功率可估算如下:

開關(guān)MOSFET:

同步MOSFET:

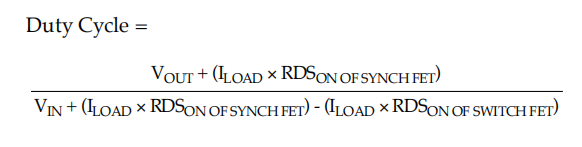

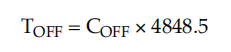

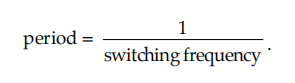

關(guān)斷時間電容器

COFF定時電容器設(shè)置調(diào)節(jié)器關(guān)閉時間:

上述占空比公式也可用于計算調(diào)節(jié)器開關(guān)頻率和選擇COFF定時電容器:

其中

同步場效應(yīng)晶體管肖特基二極管

對于同步操作,可以將肖特基二極管與同步場效應(yīng)晶體管并聯(lián),以便在開關(guān)場效應(yīng)晶體管關(guān)斷時導(dǎo)通電感電流,以提高效率。CS5166參考電路由于其出色的設(shè)計而不使用該器件。相反,采用同步場效應(yīng)晶體管的體二極管來降低成本并傳導(dǎo)電感電流。對于在200kHz左右工作的設(shè)計,低的非重疊時間與Schottky正向恢復(fù)時間相結(jié)合可能使該裝置的優(yōu)點不值得額外的費用。同步MOSFET中由于體二極管傳導(dǎo)而產(chǎn)生的功率損耗可通過以下等式估算:

功率=Vbd×ILOAD×傳導(dǎo)時間×開關(guān)頻率,其中Vbd=MOSFET體二極管的正向壓降。

對于CS5166演示板:功率=1.6V×14.2A×100ns×200kHz=0.45W

這僅僅是40W的1.1%被輸送到負(fù)載上。

用于自適應(yīng)電壓定位的“下垂”電阻器

自適應(yīng)電壓定位用于幫助在負(fù)載瞬態(tài)期間保持輸出電壓在規(guī)格范圍內(nèi)。為了實現(xiàn)自適應(yīng)電壓定位,必須在輸出電感器和輸出電容器以及負(fù)載之間連接一個“下垂電阻器”。該電阻器承載滿載電流,應(yīng)選擇這樣的電阻,以滿足直流和交流公差限制。嵌入式PC跟蹤電阻具有成本接近零的顯著優(yōu)勢。然而,這種下垂電阻的變化有三個原因:1)片材電阻率的變化導(dǎo)致PCB層的厚度變化。2) L/W不匹配,以及3)溫度變化。

1) 薄片電阻率

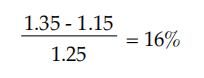

對于1盎司的銅,厚度變化通常為1.15密耳至1.35密耳。因此,由片材電阻率引起的誤差為:

2) L/W不匹配

L/W的變化由PCB制造工藝引起的變化控制,這些變化會影響下垂電阻器。由于L/W不匹配導(dǎo)致的誤差通常為1%。

3) 熱因素

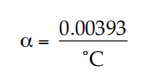

由于I2×R功率損耗,下垂電阻器的表面溫度將升高,導(dǎo)致電阻增大。此外,根據(jù)以下公式,環(huán)境溫度變化將有助于增加電阻:

式中:R20=20℃時的電阻

T=工作溫度;

R=期望的降阻值溫度T=50°C時,%R變化=12%

下垂電阻公差片材電阻率變化引起的公差:16%

L/W誤差引起的公差:1%

溫度變化引起的公差:12%

下垂電阻器的總公差:29%

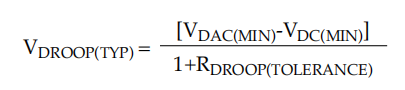

為了確定降阻電阻值,必須計算滿載時通過它的標(biāo)稱電壓降。該電壓降必須確保輸出電壓滿載高于最小直流公差規(guī)范。

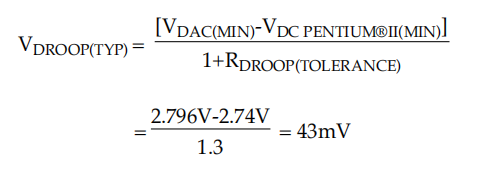

示例:對于300MHz Pentium®II,直流精度規(guī)格為2.74<VCC(核心)<2.9V,交流精度規(guī)格為2.67V<VCC(核心)<2.93V。CS5166 DAC輸出電壓為+2.796V<VDAC<+2.853V。為了不超過直流精度規(guī)范,電阻上產(chǎn)生的電壓降必須計算如下:

在CS5166的DAC精度為1%的情況下,對內(nèi)部誤差放大器的參考電壓進(jìn)行了微調(diào),使輸出電壓在空載時達(dá)到25mV高。在無負(fù)載的情況下,電阻上沒有直流壓降,產(chǎn)生一個跟蹤誤差放大器輸出電壓的輸出電壓,包括偏移量。當(dāng)滿負(fù)荷電流被輸送時,電阻上會產(chǎn)生-43mV的壓降。因此,在負(fù)載接通之前,調(diào)節(jié)器輸出預(yù)先定位在高于標(biāo)稱輸出電壓25毫伏的位置。由于負(fù)載階躍引起的總電壓降為∆V-25mV,與標(biāo)稱輸出電壓的偏差為25mV,比沒有降速電阻器時的偏差小25 mV。同樣,在滿載時,在負(fù)載關(guān)閉之前,調(diào)節(jié)器輸出預(yù)先定位在低于標(biāo)稱電壓18mV的位置。由于負(fù)載關(guān)閉導(dǎo)致的總電壓增加為∆V-18mV,與標(biāo)稱輸出電壓的偏差為18mV,比沒有降阻電阻時的偏差小18mV。這是因為輸出電容器在負(fù)載接通前預(yù)先充電至高于標(biāo)稱輸出電壓25毫伏或低于額定輸出電壓18毫伏的值(見圖8)。

很明顯,壓降電阻上的壓降越大(電阻越大),直流和負(fù)載調(diào)節(jié)越差,但交流瞬態(tài)響應(yīng)越好。

電流限制設(shè)定值計算

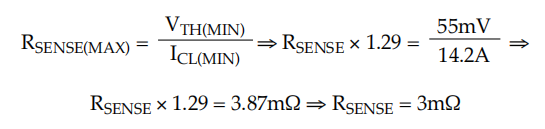

以下是通過確定用作電流傳感元件的嵌入式PCB跡線的值來設(shè)置電流限制跳閘點的設(shè)計公式。電流限制設(shè)定值必須高于正常滿載電流。必須注意外部電源部件的額定電流,因為這些部件在過載條件下首先發(fā)生故障。在設(shè)置限流觸發(fā)點時,必須考慮給定外殼溫度下的MOSFET連續(xù)和脈沖漏極電流額定值。例如,IRL 3103S(D2-PAK)MOSFET在VGS=10V和TC=100˚C時的連續(xù)漏極電流額定值為45A。MOSFET制造商數(shù)據(jù)表上的溫度曲線允許設(shè)計者確定特定VGS和TJ(結(jié)溫)下的MOSFET漏電流。反過來,這將有助于設(shè)計者設(shè)置適當(dāng)?shù)碾娏飨拗疲粫谶^載情況下造成設(shè)備故障。對于300MHz Pentium®II CPU,滿載為14.2A。內(nèi)部電流檢測比較器電流極限電壓限值為:55mV<VTH<130mV。此外,如前一節(jié)所述,RSENSE的總變異率為29%。

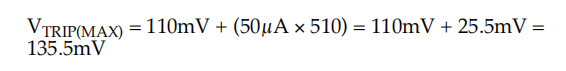

我們選擇電流傳感元件(嵌入式PCB跟蹤)的值作為最小電流限制設(shè)定值:

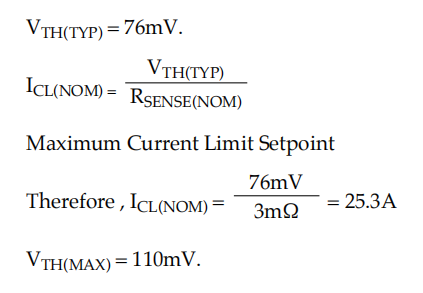

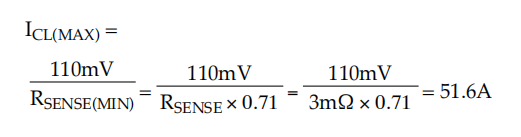

我們計算負(fù)載電流的范圍,這將導(dǎo)致內(nèi)部電流檢測比較器檢測過載情況。

來自過電流檢測數(shù)據(jù)段,額定電流限制設(shè)定值

因此,

因此,導(dǎo)致內(nèi)部電流檢測比較器通過3mΩ嵌入式PCB軌跡檢測過載條件的負(fù)載電流范圍為:14.2A<ICL<51.6A,25.3A為標(biāo)稱過載條件。

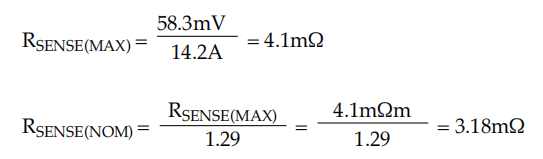

有些應(yīng)用的布局可能需要使用兩個額外的濾波器組件,一個510Ω電阻器與ISENSE引腳串聯(lián),以及一個0.1μF電容器在ISENSE和VFB引腳之間。這些是正確的限流操作所需的,電阻值取決于布局。該串聯(lián)電阻器影響電流限值設(shè)定值的計算,在確定有效電流限值時必須將其考慮在內(nèi)。

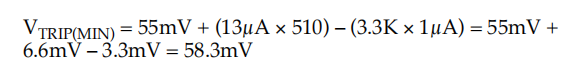

下面的計算顯示了考慮510Ω時如何確定電流限制設(shè)定值。

NSE×IFISeB(垂直強度×垂直強度)

式中,VTRIP=通過使ISENSE比較器跳閘的下降電阻器上的電壓

VTH=內(nèi)部ISENSE比較器閾值

ISENSE=ISENSE偏置電流

RISENSE=ISENSE引腳510Ω濾波電阻

RFB=VFB引腳3.3K濾波電阻

IFB=VFB偏置電流

使用RISENSE時,電流限制所需的最小電流感應(yīng)電阻(降阻器)電壓降

額定電流檢測電阻器(降阻器)使用RISENSE時電流限制所需的電壓降

當(dāng)使用RISENSE時,電流限制所需的最大電流感應(yīng)電阻(降阻電阻)電壓降

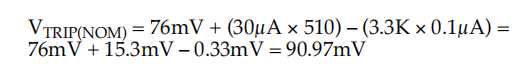

然后計算RSENSE(電流檢測PCB跟蹤)的值:

使內(nèi)部電流感應(yīng)比較器檢測過載情況的負(fù)載電流范圍如下:

額定電流限制設(shè)定值

因此,

最大電流限制設(shè)定值

因此,

因此,導(dǎo)致內(nèi)部電流檢測比較器通過3mΩ嵌入式PCB軌跡檢測過載條件的負(fù)載電流范圍為:14.2A<ICL 60A,28.6A為標(biāo)稱過載條件。

使用下垂電阻器的設(shè)計規(guī)則

埋置電阻器的基本方程為:

或

或

式中:

A=W×t=橫截面積

ρ=銅電阻率(μΩ-mil)

L=長度(密耳)

W=寬度(mils)

t=厚度(mils)

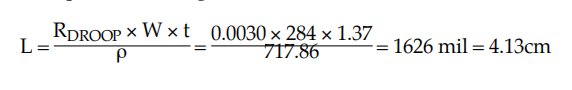

對于大多數(shù)多氯聯(lián)苯,一盎司銅的銅厚度t為35μm(1.37 mils)。ρ=717.86μΩ-密耳。

對于14.2A的奔騰II負(fù)載,在滿載時產(chǎn)生43mV壓降所需的電阻為:

根據(jù)以下準(zhǔn)則,銅的電阻率將隨溫度變化:

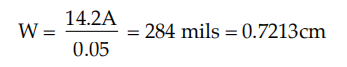

下垂電阻器寬度計算

下垂電阻器必須能夠處理負(fù)載電流,因此需要最小寬度,其計算如下(假設(shè)銅厚度為1盎司):

其中:

W=適當(dāng)功率耗散所需的最小寬度(單位:mils),以及ILOAD負(fù)載電流安培數(shù)。

奔騰II的最大負(fù)載電流為14.2A。

因此:

下垂電阻長度計算

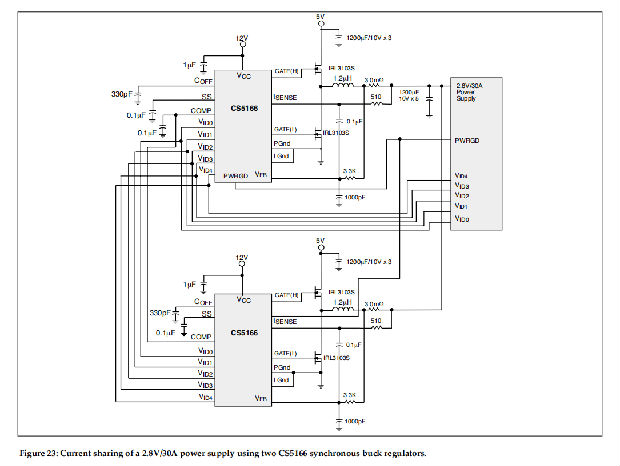

利用“下垂電阻器”實現(xiàn)均流

除了提高負(fù)載瞬態(tài)性能外,SCS5166 V2TM控制方法還允許下垂電阻器提供額外的能力,以方便地實現(xiàn)均流。圖23顯示了兩個均流同步降壓調(diào)節(jié)器的簡化示意圖。每個降壓調(diào)節(jié)器的下垂電阻器在負(fù)載端接。來自每個誤差放大器的PWM控制信號連接在一起,使內(nèi)部PWM回路調(diào)節(jié)到一個共同的電壓。由于每個電阻器端子上的電壓是相同的,這種配置導(dǎo)致在每個匹配的下垂電阻器上施加相同的電壓。結(jié)果是流過每個降壓調(diào)節(jié)器的電流相等。另一個好處是,由于每個調(diào)節(jié)器共享一個公共的PWM斜坡信號,所以趨向于實現(xiàn)到公共開關(guān)頻率的同步。

實際上,由于PWM比較器的失配、PWM斜坡(輸出電壓紋波)的斜率和傳播延遲,每個buck調(diào)節(jié)器將調(diào)節(jié)到稍有不同的輸出電壓。在輕負(fù)載下,結(jié)果可能是非常差的均流。在輸出電流為零的情況下,一些調(diào)節(jié)器可能是源電流,而另一些調(diào)節(jié)器可能是陷波電流。

這會導(dǎo)致額外的功耗和較低的效率比單一的調(diào)節(jié)器。這通常不是一個問題,因為效率是最重要的時候,供應(yīng)是滿負(fù)荷的。

這種效應(yīng)類似于同步和非同步降壓調(diào)節(jié)器之間的效率差異。同步降壓調(diào)節(jié)器在輕負(fù)載時效率較低,因為電感電流總是連續(xù)的,在關(guān)斷期間通過同步整流器從負(fù)載流向地面。在滿負(fù)荷條件下,由于同步整流器的壓降較低,同步設(shè)計更有效。同樣,由于降阻電阻器中的持續(xù)電流,在輕負(fù)載下降速共享調(diào)節(jié)器的效率將更低。由于減少了I2R損耗,重載時的效率往往更高。

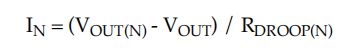

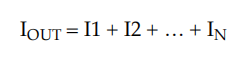

每個調(diào)節(jié)器的輸出電流可根據(jù)以下公式計算:

其中:VOUT(N)和RDROOP(N)是特定調(diào)節(jié)器的輸出電壓和下垂電阻,VOUT是系統(tǒng)輸出電壓。輸出電流是每個調(diào)節(jié)器電流的總和:

均流性能隨著負(fù)載電流的增加而提高。

由于負(fù)載電流的增加,通過降阻器的電壓降不斷增加,最終淹沒了調(diào)節(jié)器輸出電壓的差異。如果可以在下垂電阻器上形成足夠大的電壓,則均流精度將完全由它們的匹配決定。要實現(xiàn)電流共享的好處,不需要獲得完美匹配。保持輸出電流在+/-10%范圍內(nèi)通常是可以接受的。

對于微處理器應(yīng)用,必須選擇下垂電阻的值來優(yōu)化自適應(yīng)電壓定位、均流、限流和效率。電流共享是通過簡單地連接各個降壓調(diào)節(jié)器的COMP引腳來實現(xiàn)的,如圖23所示。

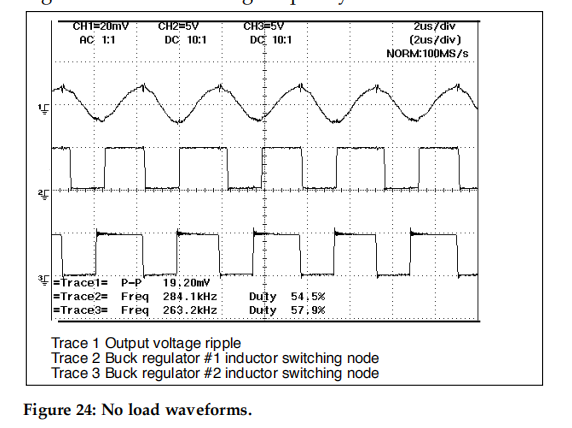

圖24顯示了空載運行。在這種情況下,沒有足夠的輸出電壓紋波跨越降阻產(chǎn)生完全同步。占空比接近理論56%(VOUT/VIN),開關(guān)頻率約為275kHz。

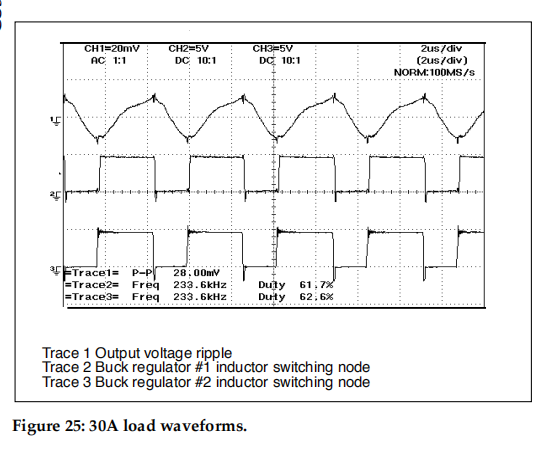

圖25顯示了30安培負(fù)載下的操作。由于紋波電壓增加,兩個調(diào)節(jié)器之間的同步現(xiàn)在得到了。損耗增加會導(dǎo)致V2TM控制回路增加補償?shù)慕油〞r間。這會導(dǎo)致更大的占空比,開關(guān)頻率相應(yīng)降低至233kHz。

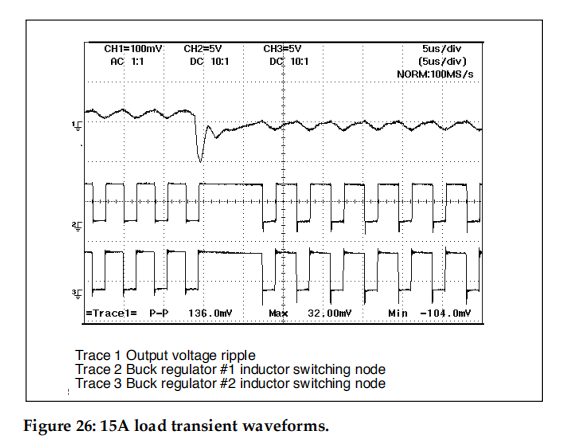

圖26顯示了在30A/μs轉(zhuǎn)換率下對15A負(fù)載階躍的電源響應(yīng)。V2TM控制回路立即強制占空比達(dá)到100%,使兩個電感器中的電流上升。由于輸出電容器阻抗,電壓尖峰為136mV。由ESL引起的尖峰的感應(yīng)分量在幾微秒內(nèi)恢復(fù)。當(dāng)電感器電流代替電容器電流時,由于電渣重熔而產(chǎn)生的電阻分量減小。

自適應(yīng)電壓定位在降低電壓尖峰方面的好處顯而易見。還可以觀察到直流電壓和占空比的差異。這種特殊的瞬態(tài)發(fā)生在調(diào)節(jié)器關(guān)閉時間的開始,導(dǎo)致恢復(fù)時間更長,電壓尖峰增大。

輸出電感器

選擇電感時,應(yīng)根據(jù)其直流電阻和電感容量來選擇。增大電感值會降低輸出電壓紋波,但會降低瞬態(tài)響應(yīng)。

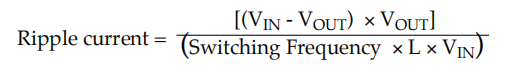

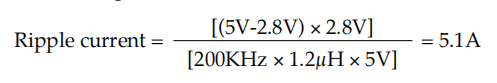

電感紋波電流

示例:VIN=+5V,VOUT=+2.8V,ILOAD=14.2A,L=1.2μH,頻率=200kHz

與輸出紋波電壓

VRIPPLE=電感紋波電流×輸出電容ESR

例子:VIN=+5V,VOUT=+2.8V,ILOAD=14.2A,L=1.2μH,開關(guān)頻率=200kHz

輸出紋波電壓=5.1A×輸出電容器ESR(根據(jù)制造商規(guī)范)

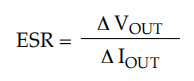

限制輸出電壓尖峰的輸出電容器ESR

這適用于比調(diào)節(jié)器響應(yīng)時間快的電流峰值。印刷電路板電阻會增加輸出電容器的ESR。

為了將14.2A負(fù)載階躍的峰值限制在100毫伏,ESR=0.1/14.2=0.007Ω。

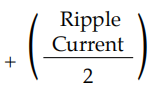

電感峰值電流

峰值電流=最大負(fù)載電流

示例:VIN=+5V,VOUT=+2.8V,ILOAD=14.2A,L=1.2μH,頻率=200kHz

峰值電流=14.2A+(5.1/2)=16.75A

一個關(guān)鍵的考慮是,電感器必須能夠在不飽和的情況下以開關(guān)頻率傳輸峰值電流。

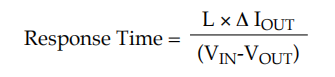

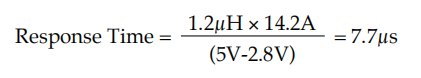

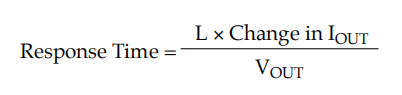

負(fù)載增加的響應(yīng)時間

(除非超過最大接通時間,否則受感應(yīng)器值限制)

示例:VIN=+5V,VOUT=+2.8V,L=1.2μH,14.2A

負(fù)載電流變化

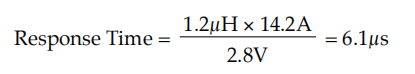

負(fù)載降低響應(yīng)時間(受電感器值限制)

示例:VOUT=+2.8V,負(fù)載電流變化14.2A,L=1.2μH

輸入和輸出電容器

必須仔細(xì)選擇和放置這些組件,以獲得最佳結(jié)果。電容器的選擇應(yīng)能在輸入電源線和調(diào)節(jié)器輸出電壓上提供可接受的紋波。輸入電容器的關(guān)鍵技術(shù)指標(biāo)是其紋波額定值,而ESR對于輸出電容器很重要。為了獲得最佳瞬態(tài)響應(yīng),需要將低值/高頻和大容量電容器放在靠近負(fù)載的位置。

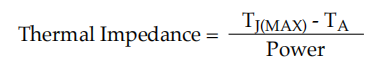

熱管理

功率mosfet和二極管的熱考慮

為了保持良好的可靠性,半導(dǎo)體元件的結(jié)溫應(yīng)保持在最高150℃或更低。可根據(jù)以下要求計算環(huán)境阻抗:

可在to-220組件上添加散熱片,以降低其熱阻抗。許多PC板布局技術(shù),如熱通孔和額外的銅箔面積可以用來提高表面貼裝元件的功率處理能力。

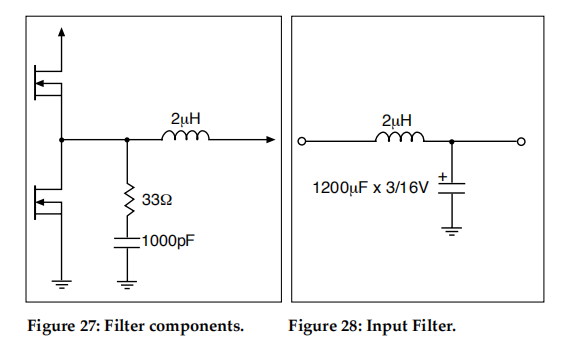

電磁干擾管理

由于在高頻下打開和關(guān)閉大電流,開關(guān)穩(wěn)壓器在正常工作時會產(chǎn)生噪聲。當(dāng)設(shè)計符合EMI/EMC法規(guī)時,可添加額外組件以減少噪聲排放。調(diào)節(jié)器運行時不需要這些部件,實驗結(jié)果可能允許消除它們。可能不需要輸入濾波器電感器,因為大容量濾波器和旁路電容器以及電路板上的其他負(fù)載會降低調(diào)節(jié)器di/dt對電路板和輸入電源的影響。放置功率元件以最小化布線距離也有助于減少排放。

布局指南

在印刷電路板上布置CPU降壓調(diào)節(jié)器時,應(yīng)使用以下檢查表來確保CS5166的正常運行。

1).寄生電容器電壓的快速變化和寄生電感器電流的突然變化是良好布局的主要考慮因素。

2).保持高電流遠(yuǎn)離敏感接地連接。避免將IC Gnd(LGnd)連接在下部FET源和輸入電容器Gnd之間。

3).避免接地回路產(chǎn)生噪音。使用星形或單點接地。

4).對于雙面PCB上的大功率降壓調(diào)節(jié)器,建議使用一個大接地層(通常是底部)。

5).盡管雙面印刷電路板通常足以構(gòu)成一個良好的布局,但四層印刷電路板是降低噪聲敏感性的最佳方法。使用兩個內(nèi)部層作為+5V和Gnd平面,頂層用于電源連接和組件過孔,底層用于噪聲敏感跡線。

6).通過將輸出電感器、開關(guān)管和同步fet放在一起,使電感器的開關(guān)節(jié)點小。

7).到集成電路的場效應(yīng)晶體管柵極軌跡必須盡可能短、直、寬。理想情況下,集成電路必須放置在fet旁邊。

8).使用更少但更大的輸出電容器,使電容器聚集在一起,并使用帶有重銅的多層線路來保持低寄生電阻。

9).將開關(guān)場效應(yīng)晶體管盡可能靠近+5V輸入電容器。

10).將輸出電容器盡可能靠近負(fù)載。

11).將VFB濾波器電阻器與VFB引腳(引腳16)串聯(lián)在引腳上。

12).將VFB濾波器電容器放在VFB引腳(引腳16)上。

13).“降速”電阻器(嵌入PCB軌跡)必須足夠大以承載滿載電流。

14).將VCC旁路電容器盡可能靠近VCC引腳,并將其連接至IC的PGnd引腳。將PGnd引腳直接連接到Gnd平面。

15).最好在PCB頂層和IC控制器下創(chuàng)建一個子地面(本地Gnd)平面。將所有邏輯電容回路和IC的LGnd引腳連接到該平面。使用至少四(4)個通孔將次地平面連接到主Gnd平面。

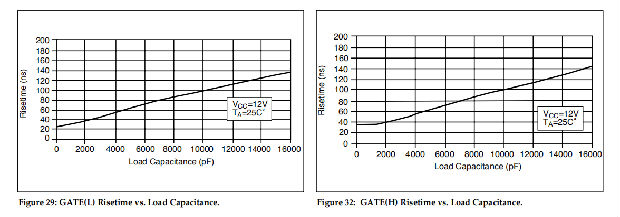

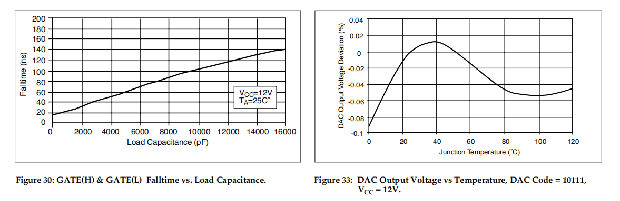

典型性能特征

附加應(yīng)用電路

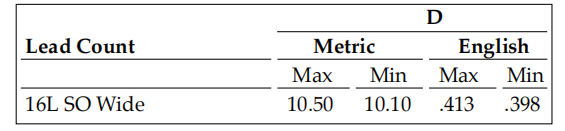

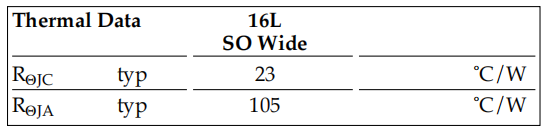

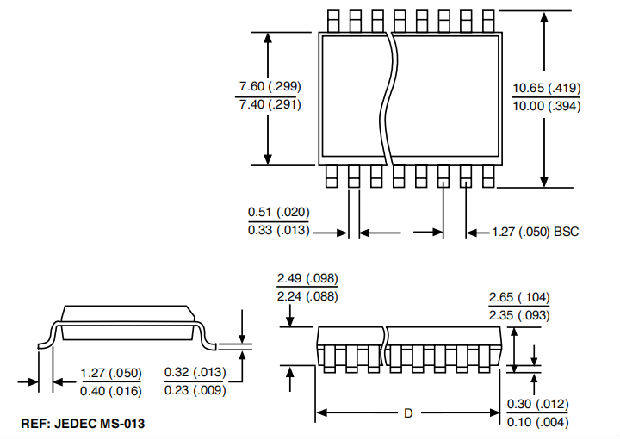

包裝規(guī)格

包裝尺寸mm(英寸)

包裝熱工數(shù)據(jù)

表面貼裝寬體(DW);300密耳寬

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國產(chǎn)降成本等解決方案,可承接項目開發(fā),以及元器件一站式采購服務(wù),類型有運放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價格請咨詢在線客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號:粵ICP備2023092210號-1