特點(diǎn)

•適合汽車應(yīng)用

•AEC-Q100測(cè)試結(jié)果如下:

–設(shè)備溫度等級(jí)1:–40°C至125°C環(huán)境工作溫度范圍

–設(shè)備HBM ESD等級(jí)H2

–設(shè)備CDM ESD分類等級(jí)C4A

•工作電源電壓6V–60V

•2.3A水槽和1.7A源極驅(qū)動(dòng)電流能力

•具有可調(diào)增益和偏移的集成雙并聯(lián)電流放大器

•集成降壓轉(zhuǎn)換器,可支持高達(dá)1.5A的外部負(fù)載

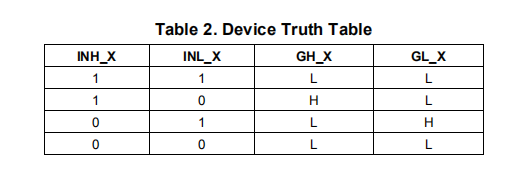

•3或6個(gè)PWM輸入的獨(dú)立控制

•具有100%占空比支持的引導(dǎo)門驅(qū)動(dòng)器

•可編程死區(qū)時(shí)間,以保護(hù)外部FET不被射穿

•用于減少電磁干擾的轉(zhuǎn)換速率控制

•外部MOSFET的可編程過(guò)電流保護(hù)

•支持3.3V和5V數(shù)字接口

•SPI接口

•熱增強(qiáng)型56針TSSOP襯墊式DCA封裝

應(yīng)用

•汽車三相無(wú)刷直流電動(dòng)機(jī)和永磁同步電動(dòng)機(jī)

•水、油、燃油泵

說(shuō)明

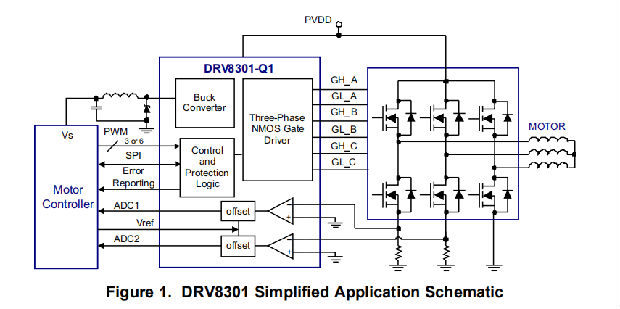

DRV8301-Q1是一種用于三相電機(jī)驅(qū)動(dòng)應(yīng)用的汽車門驅(qū)動(dòng)器IC。它提供了三個(gè)半橋驅(qū)動(dòng)器,每個(gè)驅(qū)動(dòng)器都能驅(qū)動(dòng)兩個(gè)N型mosfet,一個(gè)用于高側(cè),一個(gè)用于低側(cè)。它支持高達(dá)2.3A sink和1.7A源峰值電流能力,只需要一個(gè)從6V到60V的寬范圍電源。DRV8301-Q1使用帶涓流充電電路的引導(dǎo)柵極驅(qū)動(dòng)器,以支持100%的占空比。當(dāng)高邊場(chǎng)效應(yīng)晶體管或低邊場(chǎng)效應(yīng)晶體管切換時(shí),柵極驅(qū)動(dòng)器使用自動(dòng)握手來(lái)防止電流擊穿。在過(guò)電流情況下,感測(cè)FET的Vds以保護(hù)外部功率級(jí)。

DRV8301-Q1包括兩個(gè)電流分流放大器,用于精確的電流測(cè)量。電流放大器支持雙向電流感應(yīng),并提供高達(dá)3V的可調(diào)輸出偏移。

DRV8301-Q1也有一個(gè)集成開(kāi)關(guān)模式降壓轉(zhuǎn)換器,輸出和開(kāi)關(guān)頻率可調(diào),以支持MCU或其他系統(tǒng)電源需求。巴克能夠驅(qū)動(dòng)高達(dá)1.5A負(fù)載。

SPI接口提供詳細(xì)的故障報(bào)告和靈活的參數(shù)設(shè)置,如電流分流放大器的增益選項(xiàng)、門驅(qū)動(dòng)器的轉(zhuǎn)換速率控制等。

這些設(shè)備具有有限的內(nèi)置ESD保護(hù)。在儲(chǔ)存或搬運(yùn)過(guò)程中,應(yīng)將引線短接在一起,或?qū)⒃O(shè)備放置在導(dǎo)電泡沫中,以防止對(duì)MOS門造成靜電損傷。

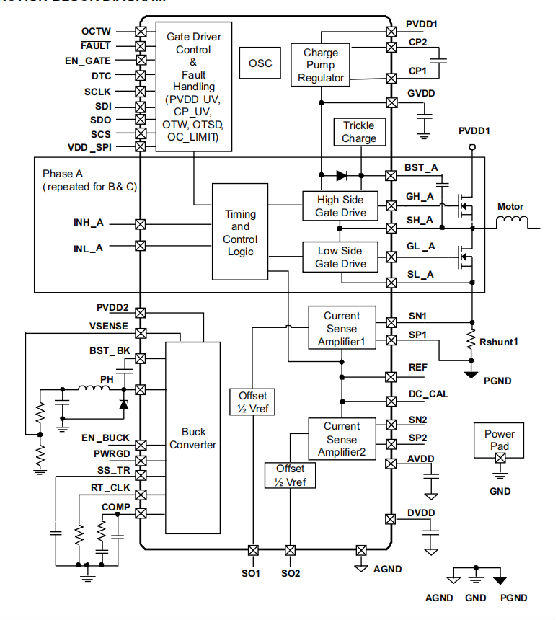

功能框圖

功能描述

三相門驅(qū)動(dòng)器

DRV8301-Q1提供了三個(gè)半橋驅(qū)動(dòng)器,每個(gè)驅(qū)動(dòng)器都能夠驅(qū)動(dòng)兩個(gè)N型MOSFET,一個(gè)用于高壓側(cè),一個(gè)用于低壓側(cè)。

門驅(qū)動(dòng)器具有以下特點(diǎn):

•開(kāi)關(guān)轉(zhuǎn)換期間,高壓側(cè)和低壓側(cè)FET之間的內(nèi)部握手,以防止電流擊穿。

•通過(guò)SPI接口可編程轉(zhuǎn)換速率或電流驅(qū)動(dòng)能力。

•支持高達(dá)200kHz的開(kāi)關(guān)頻率,Qg(TOT)=25nC或總30mA柵極驅(qū)動(dòng)平均電流

•提供外部FET的逐周期電流限制和閂鎖過(guò)電流(OC)關(guān)閉。電流通過(guò)FET漏源電壓感應(yīng),過(guò)電流水平可通過(guò)SPI接口編程

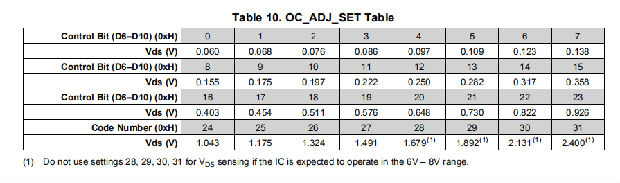

•Vds傳感范圍可從0.060V編程至2.4V,并通過(guò)SPI具有5位可編程分辨率。

•高壓側(cè)柵極驅(qū)動(dòng)將承受半橋負(fù)輸出,最高-10V,持續(xù)10ns

•在EN_柵極引腳低和故障情況下,柵極驅(qū)動(dòng)器將保持外部FET處于高阻抗模式。

•通過(guò)DTC引腳可編程死區(qū)時(shí)間。死區(qū)時(shí)間控制范圍:50ns到500ns。短DTC針腳對(duì)地將提供最短的死區(qū)時(shí)間(50ns)。只要外部死區(qū)時(shí)間長(zhǎng)于死區(qū)時(shí)間設(shè)置,外部死區(qū)時(shí)間將覆蓋內(nèi)部死區(qū)時(shí)間(為了防止擊穿電流,不能縮短最小握手時(shí)間)。

•引導(dǎo)帶用于三相預(yù)柵驅(qū)動(dòng)器的高側(cè)場(chǎng)效應(yīng)晶體管。涓流充電電路用于補(bǔ)充自舉閥蓋的電流泄漏,并支持100%的占空比運(yùn)行。

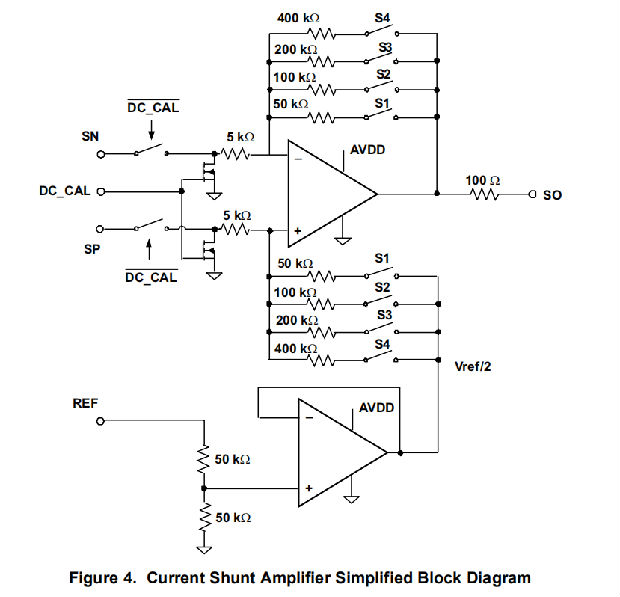

電流分流放大器

DRV8301-Q1包括兩個(gè)高性能電流分流放大器,用于精確的電流測(cè)量。

電流放大器提供高達(dá)3V的輸出偏移,以支持雙向電流感應(yīng)。

電流分流放大器具有以下特點(diǎn):

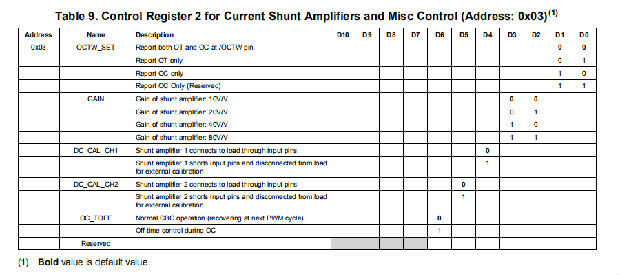

•可編程增益:通過(guò)SPI命令設(shè)置4個(gè)增益

•通過(guò)參考引腳的可編程輸出偏移(Vref的一半)

•通過(guò)SPI命令或直流校準(zhǔn)引腳進(jìn)行直流校準(zhǔn),使直流偏移和溫度漂移最小化。當(dāng)直流校準(zhǔn)啟用時(shí),裝置將短路電流分流放大器的輸入并斷開(kāi)負(fù)載。直流校準(zhǔn)可以在任何時(shí)候進(jìn)行,即使當(dāng)FET開(kāi)關(guān),因?yàn)樨?fù)載斷開(kāi)。為了獲得最佳結(jié)果,在無(wú)負(fù)載的情況下,在關(guān)閉期間執(zhí)行直流校準(zhǔn),以減少對(duì)放大器的潛在噪聲影響。

電流分流放大器的輸出可計(jì)算為:

其中,Vref是參考電壓,G是放大器的增益;SNx和SPx是通道x的輸入。SPx應(yīng)連接到電阻接地,以獲得最佳共模抑制。

圖4顯示了電流放大器的簡(jiǎn)化框圖。

BUCK變換器

DR8301中的buck轉(zhuǎn)換器與TPS54160 buck轉(zhuǎn)換器相同。盡管集成在同一個(gè)器件中,buck變換器的設(shè)計(jì)完全獨(dú)立于其余的柵極驅(qū)動(dòng)電路。由于buck將支持外部MCU或其他外部電源需求,buck操作的獨(dú)立性對(duì)于一個(gè)可靠的系統(tǒng)來(lái)說(shuō)是非常關(guān)鍵的;這將使buck從門驅(qū)動(dòng)器操作中受到的影響最小。例如:當(dāng)門驅(qū)動(dòng)器因任何故障而關(guān)閉時(shí),buck仍將工作,除非故障是buck本身造成的。buck保持在3.5V的低PVDD下工作,這將確保當(dāng)柵極驅(qū)動(dòng)器由于低PVDD而無(wú)法工作時(shí),系統(tǒng)能夠平穩(wěn)地上電和斷電。

buck有一個(gè)集成的高邊n溝道MOSFET。為了提高線路和負(fù)載瞬變期間的性能,該裝置實(shí)現(xiàn)了恒定頻率、電流模式控制,減少了輸出電容,簡(jiǎn)化了外部頻率補(bǔ)償設(shè)計(jì)。

在選擇輸出濾波器組件時(shí),300kHz到2200kHz的寬開(kāi)關(guān)頻率允許效率和尺寸優(yōu)化。開(kāi)關(guān)頻率通過(guò)RT峎CLK引腳上的接地電阻進(jìn)行調(diào)整。該設(shè)備在RT_ck引腳上有一個(gè)內(nèi)部鎖相環(huán)(PLL),用于將電源開(kāi)關(guān)接通與外部系統(tǒng)時(shí)鐘的下降沿同步。

buck轉(zhuǎn)換器的默認(rèn)啟動(dòng)電壓約為2.5V。EN_buck引腳有一個(gè)內(nèi)部上拉電流源,可用于通過(guò)兩個(gè)外部電阻器調(diào)整輸入電壓欠壓鎖定(UVLO)閾值。此外,上拉電流提供了一個(gè)默認(rèn)條件。當(dāng)EN_BUCK引腳浮動(dòng)時(shí),設(shè)備將運(yùn)行。在不切換和空載時(shí),工作電流為116μA。當(dāng)設(shè)備被禁用時(shí),電源電流為1.3μA。

集成的200mΩ高側(cè)MOSFET允許高效率的電源設(shè)計(jì),能夠向負(fù)載提供1.5安培的連續(xù)電流。集成高壓側(cè)MOSFET的偏置電壓由啟動(dòng)端到PH引腳上的電容器提供。啟動(dòng)電容電壓由一個(gè)UVLO電路監(jiān)控,當(dāng)啟動(dòng)電壓低于預(yù)設(shè)閾值時(shí),將關(guān)閉高壓側(cè)MOSFET。由于啟動(dòng)UVLO,buck可以在高占空比下工作。輸出電壓可以降低到0.8V參考電壓。

BUCK有一個(gè)功率良好的比較器(PWRGD),當(dāng)調(diào)節(jié)輸出電壓小于標(biāo)稱輸出電壓的92%或大于109%時(shí),該比較器會(huì)進(jìn)行判斷。PWRGD引腳是一個(gè)開(kāi)路漏極輸出,當(dāng)VSENSE引腳電壓在標(biāo)稱輸出電壓的94%和107%之間時(shí),該引腳會(huì)斷開(kāi),允許引腳在使用上拉電阻器時(shí)轉(zhuǎn)換為高電平。

該BUCK通過(guò)利用OV功率良好比較器來(lái)最小化過(guò)電壓(OV)瞬態(tài)。當(dāng)OV比較器被激活時(shí),高側(cè)MOSFET被關(guān)閉并屏蔽,直到輸出電壓低于107%。

SS_-TR(慢啟動(dòng)/跟蹤)引腳用于最小化涌入電流或在通電期間提供電源順序。一個(gè)小值電容器應(yīng)耦合到引腳上,以調(diào)整慢啟動(dòng)時(shí)間。電阻分壓器可與引腳耦合,以滿足關(guān)鍵電源排序要求。在輸出通電之前,SS_TR引腳被放電。這種放電確保了超溫故障后可重復(fù)重啟,

此外,在過(guò)載情況下,BUCK通過(guò)過(guò)載恢復(fù)電路對(duì)慢啟動(dòng)電容器進(jìn)行放電。一旦故障條件消除,過(guò)載恢復(fù)電路將緩慢啟動(dòng)從故障電壓到標(biāo)稱調(diào)節(jié)電壓的輸出。頻率折疊電路在啟動(dòng)和過(guò)電流故障條件下降低開(kāi)關(guān)頻率,以幫助控制電感器電流。

保護(hù)特性

功率級(jí)保護(hù)

DRV8301-Q1為MOSFET功率級(jí)提供過(guò)流和欠壓保護(hù)。在故障關(guān)閉條件下,所有門驅(qū)動(dòng)器輸出將保持低,以確保外部FET處于高阻抗?fàn)顟B(tài)。

過(guò)電流保護(hù)(OCP)和報(bào)告

為了保護(hù)功率級(jí)不受大電流的損壞,在DRV8301-Q1中安裝了VDS傳感電路。基于功率mosfet的RDS(on)和最大允許id,可以計(jì)算出一個(gè)電壓閾值,當(dāng)超過(guò)該閾值時(shí),觸發(fā)OC保護(hù)特性。該電壓閾值水平可通過(guò)SPI命令進(jìn)行編程。

SPI中共有4個(gè)OC_模式設(shè)置。

1.模式限流

當(dāng)電流限制模式被啟用時(shí),設(shè)備在OC事件期間操作電流限制而不是OC關(guān)閉。過(guò)電流事件通過(guò)OCTW引腳報(bào)告。在同一個(gè)PWM周期內(nèi)或在最大64μs的時(shí)間段(內(nèi)部計(jì)時(shí)器)內(nèi),OCTW報(bào)告應(yīng)保持低水平,以便外部控制器有足夠的時(shí)間對(duì)警告信號(hào)進(jìn)行采樣。如果在報(bào)告過(guò)程中,其他FET獲得OC,則OCTW報(bào)告將保持低并重新計(jì)數(shù)另一個(gè)64μs,除非兩個(gè)FET上的PWM周期結(jié)束。

在電流限制模式下有兩個(gè)電流控制設(shè)置(在SPI中按一位選擇,默認(rèn)為CBC模式)。

–設(shè)置1(CBC模式):在OC事件期間,檢測(cè)到OC的FET將關(guān)閉,直到下一個(gè)PWM周期。

–設(shè)置2(關(guān)閉時(shí)間控制模式):

–在OC事件期間,如果PWM信號(hào)仍然保持高電平,則檢測(cè)到OC的FET將關(guān)閉64us作為關(guān)閉時(shí)間,然后恢復(fù)正常(因此相同的FET將再次打開(kāi))。由于所有三相或6個(gè)FET共用一個(gè)定時(shí)器,如果不止一個(gè)FET發(fā)生OC,那么在發(fā)生OC事件的所有FET通過(guò)64μs之前,F(xiàn)ET不會(huì)恢復(fù)正常。

–如果在定時(shí)器運(yùn)行期間切換了該場(chǎng)效應(yīng)晶體管的脈寬調(diào)制信號(hào),則該開(kāi)關(guān)場(chǎng)效應(yīng)晶體管的設(shè)備將恢復(fù)正常運(yùn)行。所以在這種情況下,實(shí)時(shí)關(guān)閉時(shí)間可能小于64uS。

–如果在定時(shí)器運(yùn)行期間,兩個(gè)FET獲得OC,而一個(gè)FET的PWM信號(hào)被切換,則該FET將恢復(fù)正常,而另一個(gè)FET將關(guān)閉直到計(jì)時(shí)器結(jié)束(除非其PWM也被切換)

2.OC閂鎖關(guān)閉模式

當(dāng)發(fā)生OC時(shí),如果同一相的任何一個(gè)FET中有OC,則該器件將同時(shí)關(guān)閉該相的高側(cè)和低壓側(cè)FET。

3.僅報(bào)告模式

在此模式下不會(huì)執(zhí)行任何保護(hù)操作。OC檢測(cè)將通過(guò)OCTW引腳和SPI狀態(tài)寄存器報(bào)告。外部MCU應(yīng)根據(jù)其自身的控制算法采取行動(dòng)。將在OCTW管腳上實(shí)現(xiàn)64μS的脈沖拉伸,以便控制器有足夠的時(shí)間來(lái)檢測(cè)OC信號(hào)。

4.OC禁用模式

設(shè)備將忽略所有OC檢測(cè),也不會(huì)報(bào)告它們。

欠壓保護(hù)(UVP)

為了在啟動(dòng)、關(guān)閉和其他可能的電壓條件下保護(hù)功率輸出級(jí)DRV8301-Q1通過(guò)在PVDD低于6V(PVDD_-UV)或GVDD低于7.5V(GVDD_-UV)時(shí)驅(qū)動(dòng)其低輸出,提供功率級(jí)欠壓保護(hù)。當(dāng)UVP被觸發(fā)時(shí),DRV8301-Q1輸出被驅(qū)動(dòng)低,外部mosfet將進(jìn)入高阻抗?fàn)顟B(tài)。

過(guò)電壓保護(hù)(GVDD_-OV)

如果GVDD電壓超過(guò)16V,裝置將關(guān)閉柵極驅(qū)動(dòng)器和充電泵,以防止與GVDD或充電泵相關(guān)的潛在問(wèn)題(例如,外部GVDD蓋或充電泵短路)。該故障為鎖定故障,只能通過(guò)EN_門引腳上的轉(zhuǎn)換復(fù)位。

過(guò)熱保護(hù)

實(shí)現(xiàn)了兩級(jí)超溫檢測(cè)電路:

•1級(jí):超溫警告(OTW)

OTW通過(guò)OCTW引腳(過(guò)流溫度警告)報(bào)告,用于默認(rèn)設(shè)置。OCTW引腳只能通過(guò)SPI命令設(shè)置為報(bào)告OTW或OCW。參見(jiàn)SPI寄存器部分。

•2級(jí):門驅(qū)動(dòng)器和電荷泵(OTSD_gate)的超溫(OT)鎖定關(guān)閉

故障將報(bào)告給故障引腳。這是一個(gè)閉鎖關(guān)閉,因此即使OT狀態(tài)不再存在,門驅(qū)動(dòng)器也不會(huì)自動(dòng)恢復(fù)。在溫度低于預(yù)設(shè)值tOTSD\U CLR后,需要通過(guò)引腳或SPI(復(fù)位門)復(fù)位門驅(qū)動(dòng)器,使其恢復(fù)正常運(yùn)行。

SPI操作仍然可用,只要PVDD仍在定義的操作范圍內(nèi),OTSD操作期間寄存器設(shè)置將保留在設(shè)備中。

故障及保護(hù)處理

故障引腳指示發(fā)生了關(guān)機(jī)錯(cuò)誤事件,例如過(guò)電流、過(guò)溫、過(guò)壓或欠壓。請(qǐng)注意,故障是開(kāi)路漏極信號(hào)。在啟動(dòng)期間,當(dāng)門驅(qū)動(dòng)器準(zhǔn)備好接收PWM信號(hào)時(shí),故障將變高(內(nèi)部EN_gate變高)。

OCTW引腳指示與關(guān)機(jī)無(wú)關(guān)的過(guò)電流事件和過(guò)熱事件。

以下是所有保護(hù)功能及其報(bào)告結(jié)構(gòu)的摘要:

引腳控制功能

EN_GATE

EN_GATE low用于將柵極驅(qū)動(dòng)器、電荷泵、電流分流放大器和內(nèi)部調(diào)節(jié)塊置于低功耗模式以節(jié)省能源。在此狀態(tài)期間不支持SPI通信。只要PVDD仍然存在,器件將把MOSFET輸出級(jí)置于高阻抗模式。

當(dāng)EN_門引腳到高電平時(shí),它將經(jīng)歷一個(gè)通電序列,并啟用門驅(qū)動(dòng)器、電流放大器、電荷泵、內(nèi)部調(diào)節(jié)器等,并重置與門驅(qū)動(dòng)器塊相關(guān)的所有鎖定故障。它還將重置SPI表中的狀態(tài)寄存器。除非故障仍然存在,否則當(dāng)在錯(cuò)誤事件后切換EN_GATE時(shí),所有鎖定的故障都可以復(fù)位。

當(dāng)EN_門從高到低時(shí),它會(huì)立即關(guān)閉柵極驅(qū)動(dòng)塊,因此柵極輸出可以使外部fet處于高阻抗模式。然后它將等待10秒,然后完全關(guān)閉其余的街區(qū)。快速故障復(fù)位模式可以通過(guò)短時(shí)間(小于10μS)切換EN_GATE引腳來(lái)實(shí)現(xiàn)。這將防止設(shè)備關(guān)閉其他功能塊,如電荷泵和內(nèi)部調(diào)節(jié)器,并帶來(lái)更快和簡(jiǎn)單的故障恢復(fù)。SPI仍然可以在這種快速的門重設(shè)模式下工作。

重置所有故障的另一種方法是使用SPI命令(reset_GATE),它將只重置門驅(qū)動(dòng)器塊和所有SPI狀態(tài)寄存器,而不關(guān)閉其他功能塊。

一個(gè)例外是重置GVDD_-OV故障。快速門快速故障復(fù)位或SPI命令復(fù)位在GVDD\U OV故障下不起作用。復(fù)位GVDD_OV故障需要一個(gè)低電平保持時(shí)間超過(guò)10μS的完整EN_GATE。強(qiáng)烈建議在發(fā)生GVDD_OV時(shí)檢查系統(tǒng)和板。

EN_BUCK

降壓使能引腳,內(nèi)部上拉電流源。拉到1.2V以下禁用。浮動(dòng)以啟用。

故障診斷碼

死區(qū)時(shí)間可通過(guò)DTC引腳編程。在故障診斷碼(DTC)與接地之間應(yīng)連接一個(gè)電阻,以控制死區(qū)時(shí)間。死區(qū)時(shí)間控制范圍從50ns到500ns。短DTC針腳對(duì)地將提供最短的死區(qū)時(shí)間(50ns)。電阻范圍為0至150kΩ。死區(qū)時(shí)間在這個(gè)電阻范圍內(nèi)線性設(shè)定。

電流直通保護(hù)將始終在裝置中啟用,與死區(qū)時(shí)間設(shè)置和輸入模式設(shè)置無(wú)關(guān)。

VDD_SPI

VDD_SPI是SDO引腳的電源。它必須連接到MCU用于SPI操作的同一電源(3.3V或5V)。

在通電或斷電瞬態(tài)過(guò)程中,VDD_SPI引腳可能很快為零電壓。在此期間,系統(tǒng)中任何其他設(shè)備的SDO引腳不應(yīng)出現(xiàn)任何SDO信號(hào),因?yàn)檫@會(huì)導(dǎo)致DRV8301-Q1中的寄生二極管從SDO導(dǎo)至VDD U SPI引腳短路。在系統(tǒng)電源順序設(shè)計(jì)中應(yīng)考慮和防止這一點(diǎn)。

直流電

當(dāng)直流校準(zhǔn)被啟用時(shí),裝置將短路并聯(lián)放大器的輸入并斷開(kāi)與負(fù)載的連接,因此外部微控制器可以進(jìn)行直流偏移校準(zhǔn)。直流偏移校準(zhǔn)也可以用SPI命令完成。如果只使用SPI進(jìn)行直流校準(zhǔn),則直流電插頭可以連接到GND。

SPI引腳

SDO引腳必須是3態(tài)的,這樣一條數(shù)據(jù)總線就可以連接到多個(gè)SPI從設(shè)備。SCS引腳處于低激活狀態(tài)。當(dāng)SCS較高時(shí),SDO處于高阻抗模式。

啟停順序控制

在通電期間,所有門驅(qū)動(dòng)輸出保持在低水平。從高電平到低電平的門極放大器可以從高電平到低電平。如果不存在錯(cuò)誤,DRV8301-Q1準(zhǔn)備好接受PWM輸入。只要PVDD在功能范圍內(nèi),即使在門禁用模式下,柵極驅(qū)動(dòng)器也可以控制功率場(chǎng)效應(yīng)晶體管。

從SDO到VDD_SPI之間有一個(gè)內(nèi)部二極管,因此VDD_SPI需要始終以與其他SPI設(shè)備相同的功率電平供電(如果有來(lái)自其他設(shè)備的SDO信號(hào))。在SDO引腳上出現(xiàn)任何信號(hào)之前,VDD U SPI電源應(yīng)首先通電,在SDO引腳完成所有通信后關(guān)閉電源。

SPI通信

SPI接口

SPI接口用于設(shè)置設(shè)備配置、運(yùn)行參數(shù)和讀取診斷信息。DRV8301-Q1 SPI接口在從屬模式下工作。

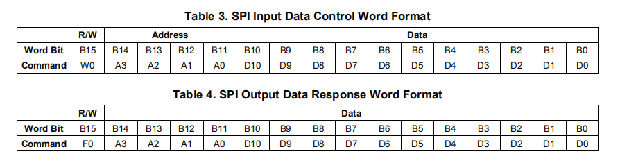

SPI輸入數(shù)據(jù)(SDI)字由16位字組成,11位數(shù)據(jù)和5位(MSB)命令。SPI輸出數(shù)據(jù)(SDO)字由16位字組成,11位寄存器數(shù)據(jù)、4位MSB地址數(shù)據(jù)和1個(gè)幀故障位(活動(dòng)1)。當(dāng)一個(gè)幀無(wú)效時(shí),幀故障位將設(shè)置為1,其余的SDO位將移出零。

有效幀必須滿足以下條件:

1.當(dāng)/SCS變低時(shí),時(shí)鐘必須很低。

2.我們應(yīng)該有16個(gè)完整的時(shí)鐘周期。

3.當(dāng)/SCS變高時(shí),時(shí)鐘必須低。

當(dāng)SCS被斷言為高電平時(shí),SCLK和SDI引腳上的任何信號(hào)都將被忽略,SDO被強(qiáng)制進(jìn)入高阻抗?fàn)顟B(tài)。當(dāng)SCS從高電平轉(zhuǎn)換到低電平時(shí),SDO被啟用,SPI響應(yīng)字根據(jù)前一時(shí)鐘周期SPI中的5位命令加載到移位寄存器中。

當(dāng)SCS轉(zhuǎn)換為低電平時(shí),SCLK引腳必須為低電平。當(dāng)SCS較低時(shí),在時(shí)鐘的每個(gè)上升沿,響應(yīng)位在SDO管腳上串行移出,MSB首先移出。

當(dāng)SCS較低時(shí),在時(shí)鐘的每個(gè)下降沿,新的控制位在SDI管腳上采樣。SPI命令位被解碼以確定寄存器地址和訪問(wèn)類型(讀或?qū)懀SB將首先在中移位。如果發(fā)送到SDI的字小于16位或大于16位,則視為幀錯(cuò)誤。如果是寫(xiě)命令,數(shù)據(jù)將被忽略。SDO(MSB)中的故障位將在下一個(gè)16位字周期中報(bào)告1。

在第16個(gè)時(shí)鐘周期之后或當(dāng)SCS從低轉(zhuǎn)換到高時(shí),在寫(xiě)訪問(wèn)類型的情況下,SPI接收移位寄存器數(shù)據(jù)被傳輸?shù)降刂放c解碼的SPI命令地址值匹配的鎖存器中。只要SCS保持低激活狀態(tài),位之間可以經(jīng)過(guò)任何時(shí)間。這允許使用兩個(gè)8位字。

對(duì)于SPI中的一個(gè)讀取命令(第N個(gè)周期),SP0將在下一個(gè)周期(N+1)中發(fā)送寄存器中的數(shù)據(jù),并在讀取命令中添加地址。

對(duì)于SPI中的寫(xiě)入命令,SPO將在下一個(gè)16位字周期(N+1)中發(fā)送狀態(tài)寄存器0x00h中的數(shù)據(jù)。在大多數(shù)情況下,當(dāng)有一個(gè)寫(xiě)命令時(shí),這個(gè)特性將使SPI通信效率最大化,但是仍然可以在不發(fā)送額外的讀命令的情況下返回故障狀態(tài)值。

SPI格式

SPI輸入數(shù)據(jù)控制字長(zhǎng)16位,包括:

•1讀或?qū)懳籛[15]

•4個(gè)地址位A[14:11]

•11個(gè)數(shù)據(jù)位D[10:0]

SPI輸出數(shù)據(jù)響應(yīng)字的長(zhǎng)度為16位,其內(nèi)容取決于上一個(gè)周期中給定的SPI命令(SPI控制字)。當(dāng)一個(gè)SPI控制字被移入時(shí),SPI響應(yīng)字(在相同的轉(zhuǎn)換時(shí)間內(nèi)被移出)是對(duì)上一個(gè)SPI命令(移入SPI控制字“N”和移出SPI響應(yīng)字“N-1”)的響應(yīng)。

因此,每個(gè)SPI控制/響應(yīng)對(duì)需要兩個(gè)完整的16位移位周期才能完成。

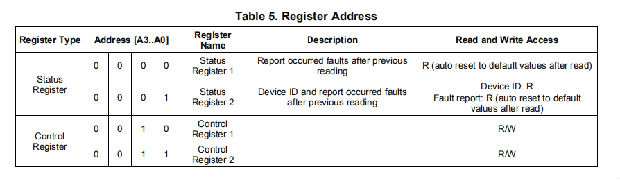

SPI控制和狀態(tài)寄存器

讀/寫(xiě)位

SDI字(W0)的MSB位是讀/寫(xiě)位。當(dāng)W0=0時(shí),輸入數(shù)據(jù)是一個(gè)寫(xiě)命令;當(dāng)W0=1時(shí),輸入數(shù)據(jù)是一個(gè)讀命令,寄存器值將在同一個(gè)字周期內(nèi)從SDO從D10發(fā)送到D0。

地址位

SPI數(shù)據(jù)位

狀態(tài)暫存器

•所有狀態(tài)寄存器位處于鎖定模式。讀取每個(gè)狀態(tài)寄存器將重置該寄存器中的位。讀取故障寄存器兩次以獲取更新的狀態(tài)條件。

•當(dāng)“低”電平保持時(shí)間超過(guò)10μS時(shí),EN_GATE切換將強(qiáng)制關(guān)閉和啟動(dòng)序列,并重置狀態(tài)寄存器中的所有值,包括GVDD_OV故障。

•低電平保持小于10uS的EN_GATE togging(快速故障復(fù)位)或GATE_reset high(在SPI中)將重置狀態(tài)寄存器中的所有值,gvd_OV fault仍將被鎖定為故障。

•當(dāng)發(fā)生任何故障導(dǎo)致停機(jī)(GVDD U UV、PVDD U UV、OTSD、OCSD、GVDD_OV)時(shí),故障為高故障,這與故障硬件引腳相反。

控制暫存器

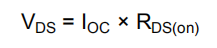

過(guò)流調(diào)整

當(dāng)外部MOSFET被打開(kāi)時(shí),輸出電流流過(guò)MOSFET,從而產(chǎn)生電壓降VDS。當(dāng)VDS超過(guò)預(yù)設(shè)值IOC時(shí),將啟用過(guò)電流保護(hù)事件。OC跳閘值可通過(guò)SPI命令編程。假設(shè)MOSFET的導(dǎo)通電阻為RDS(on),則Vds可計(jì)算為:

VDS是通過(guò)slux和SH_x引腳為低側(cè)MOSFET測(cè)量的。對(duì)于高側(cè)MOSFET,VDS是通過(guò)PVDD1(內(nèi)部)和SH_x測(cè)量的。因此,限制PVDD1電源上的紋波對(duì)于精確的高壓側(cè)電流傳感非常重要。

同樣重要的是要注意,對(duì)于OC跳閘點(diǎn),通道之間的公差可以高達(dá)20%。這是為了保護(hù),而不是用來(lái)調(diào)節(jié)電機(jī)相位的電流。

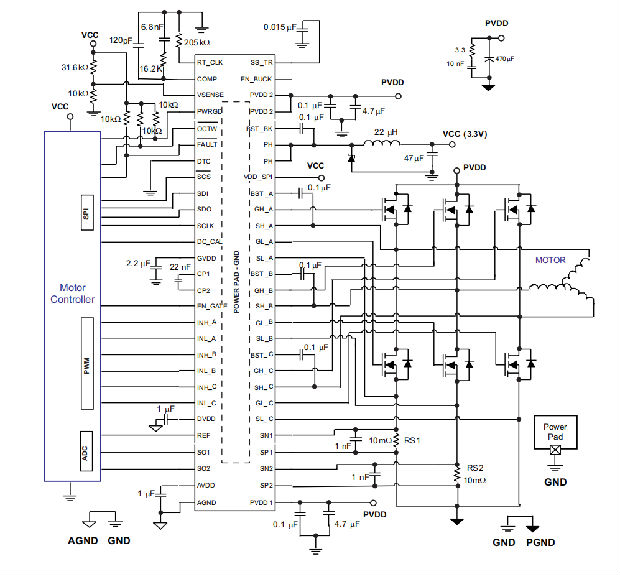

應(yīng)用示意圖示例

例子:

降壓:PVDD=3.5V–40V,Iout_max=1.5A,Vo=3.3V,F(xiàn)s=570 kHz。

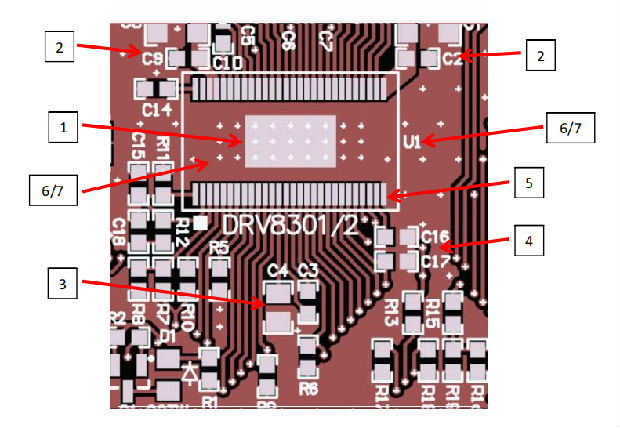

PCB布局建議

以下是為DRV8301-Q1設(shè)計(jì)PCB時(shí)使用的一些布局建議。

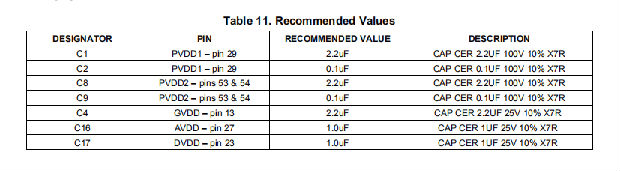

1.DRV8301-Q1通過(guò)電源板與GND進(jìn)行電氣連接。始終檢查以確保PowerPAD已正確焊接(參見(jiàn)PowerPAD應(yīng)用報(bào)告,SLMA002)。

2. C1/C2/C8/C9,PVDD去耦電容器應(yīng)靠近其相應(yīng)的管腳,并通過(guò)低阻抗路徑連接到設(shè)備GND(PowerPAD)。

3.C4,gvd電容器應(yīng)放置在靠近其相應(yīng)引腳的低阻抗路徑的設(shè)備GND(PowerPAD)。

4.C16/C17、AVDD和DVDD電容器應(yīng)放置在靠近其相應(yīng)引腳的位置,并采用低阻抗路徑連接至AGND引腳。最好在同一層建立這種連接。

5.AGND應(yīng)該通過(guò)低阻抗跟蹤/銅填充連接到設(shè)備GND(PowerPAD)。

6.添加縫合過(guò)孔,以減少?gòu)纳系较碌腉ND路徑的阻抗。

7.試著清理DRV8301-Q1周圍和下方的空間,以便更好地從電源板散熱。

安芯科創(chuàng)是一家國(guó)內(nèi)芯片代理和國(guó)外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國(guó)產(chǎn)降成本等解決方案,可承接項(xiàng)目開(kāi)發(fā),以及元器件一站式采購(gòu)服務(wù),類型有運(yùn)放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價(jià)格請(qǐng)咨詢?cè)诰€客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國(guó)民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國(guó)泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來(lái)源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號(hào):粵ICP備2023092210號(hào)-1