特征

•14位分辨率

•2.4-GSPS最大更新速率數(shù)模轉(zhuǎn)換器

•雙差分輸入端口

–偶數(shù)/奇數(shù)解復(fù)用數(shù)據(jù)

–每個(gè)端口最多1.2-GSPS,總共2.4-GSPS

–雙14位輸入+1個(gè)參考位

–DDR輸出時(shí)鐘

–與參考位同步的DLL優(yōu)化時(shí)鐘定時(shí)

–LVDS和超級(jí)運(yùn)輸™ 電壓電平兼容

–用于數(shù)據(jù)和參考位輸入的內(nèi)部100Ω終端

•可選擇2次插值和Fs/2混合

•差分可縮放電流輸出:5至30 mA

•片上1.2-V基準(zhǔn)

•3.3-V模擬電源操作

•功耗:2 W•252 Ball GDJ封裝

應(yīng)用

•測(cè)試和測(cè)量:任意波形發(fā)生器

•通信

說明

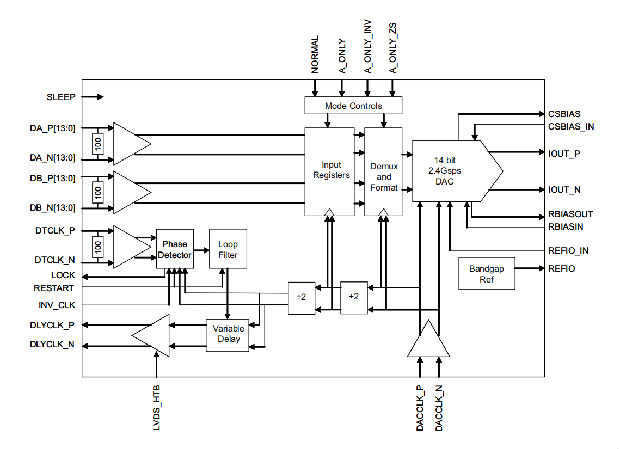

DAC5670是一個(gè)14位2.4-GSPS數(shù)模轉(zhuǎn)換器(DAC),具有雙解復(fù)用差分輸入端口。DAC5670以DAC采樣率計(jì)時(shí),兩個(gè)輸入端口以最大1.2 GSPS的速度運(yùn)行。一個(gè)附加的參考位輸入序列被用來調(diào)整到數(shù)據(jù)源的輸出時(shí)鐘延遲,通過延遲鎖定環(huán)(DLL)優(yōu)化相對(duì)于該參考位的內(nèi)部數(shù)據(jù)鎖存時(shí)鐘。或者,可以繞過DLL,并通過控制數(shù)據(jù)設(shè)置和保持DLYCLK的定時(shí)來管理定時(shí)接口。

DAC5670還可以在同一時(shí)鐘配置的一個(gè)輸入端口上接受高達(dá)1.2gsps的數(shù)據(jù)。在單端口模式下,通過重復(fù)輸入采樣(僅A U模式)、通過零填充進(jìn)行2次插值(僅A_ZS模式)或通過重復(fù)和反轉(zhuǎn)輸入樣本進(jìn)行2次插值(A_ONLY_INV),可以將輸入采樣率提高一倍,達(dá)到2.4 GSPS。

DAC5670使用單個(gè)3-V至3.6-V電源電壓工作。在最大工作條件下,功耗為2瓦。DAC5670提供20毫安的標(biāo)稱滿標(biāo)度差分電流輸出,支持單端和差分應(yīng)用。片上1.2V溫度補(bǔ)償帶隙基準(zhǔn)和控制放大器允許用戶將滿標(biāo)度輸出電流從標(biāo)稱20毫安調(diào)整到低至5毫安或高達(dá)30毫安。輸出電流可以直接供給負(fù)載,不需要額外的外部輸出緩沖器。該裝置是專為差動(dòng)變壓器耦合輸出和50Ω雙端接負(fù)載而設(shè)計(jì)的。

DAC5670提供252球GDJ包。該裝置的特點(diǎn)是可在-40°C至85°C的溫度范圍內(nèi)工作。

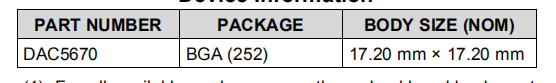

設(shè)備信息

(1)、有關(guān)所有可用的軟件包,請(qǐng)參閱數(shù)據(jù)表末尾的訂購附錄。

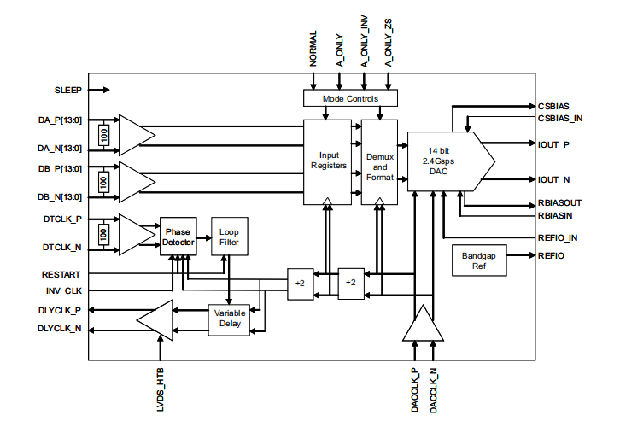

簡(jiǎn)化示意圖

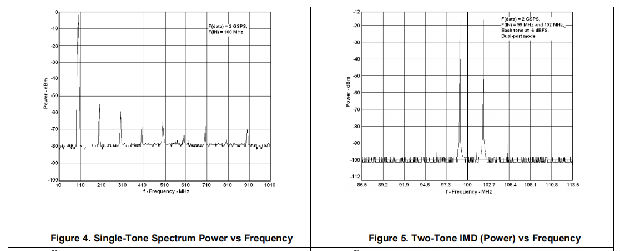

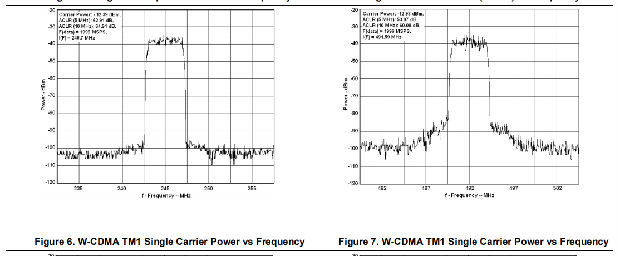

典型特征

詳細(xì)說明

概述

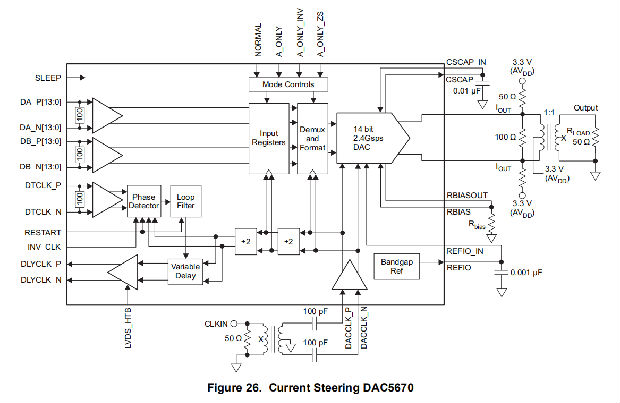

圖26顯示了當(dāng)前轉(zhuǎn)向DAC5670的簡(jiǎn)化框圖。DAC5670由NPN晶體管電流匯分段陣列組成,能夠提供高達(dá)30毫安的全刻度輸出電流。差分電流開關(guān)將每個(gè)電流匯的電流引向互補(bǔ)輸出節(jié)點(diǎn)IOUT_P或IOUT峎N之一。互補(bǔ)電流輸出可實(shí)現(xiàn)差分操作,消除共模噪聲源(數(shù)字饋通、片上和PCB噪聲)、直流偏移和偶數(shù)階失真分量,信號(hào)輸出功率加倍。

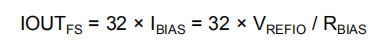

滿標(biāo)度輸出電流由一個(gè)外部電阻器(RBIAS)與片上帶隙基準(zhǔn)電壓源(1.2V)和控制放大器相結(jié)合來設(shè)置。通過電阻RBIAS的電流(IBIAS)在內(nèi)部鏡像,以提供等于32×IBIAS的滿標(biāo)度輸出電流。通過使用適當(dāng)?shù)钠秒娮柚担瑵M標(biāo)度電流可在30至5 mA之間調(diào)節(jié)。

功能框圖

特性描述

數(shù)字輸入

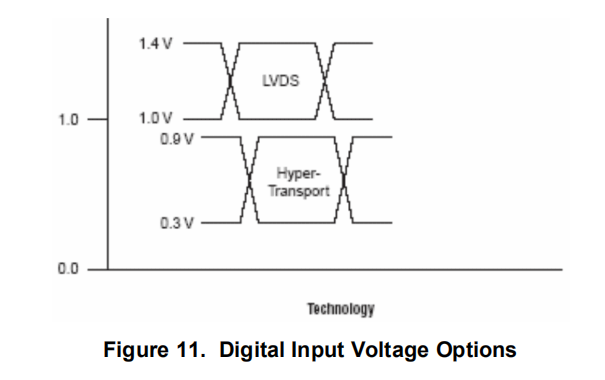

DAC5670差分?jǐn)?shù)字輸入與LVDS和超級(jí)傳輸電壓電平兼容。

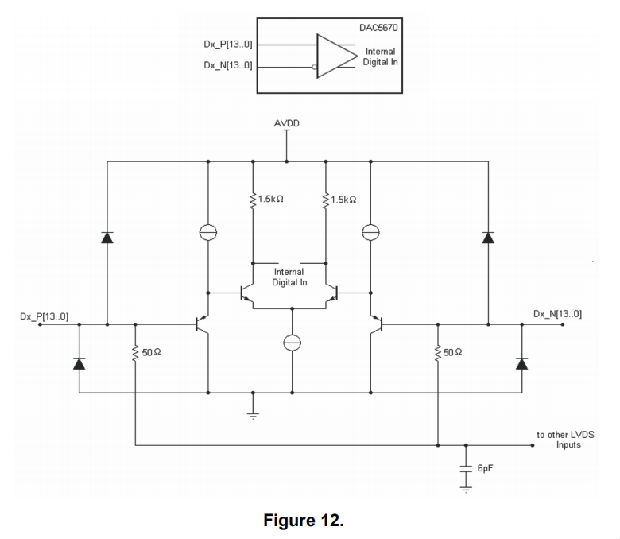

DAC5670使用低壓差分信號(hào)(LVDS和超級(jí)傳輸)作為總線輸入接口。LVDS和HyperTransport輸入模式具有低差分電壓擺幅的特點(diǎn)。LVDS和超級(jí)傳輸模式的差異特性允許在低電磁干擾(EMI)水平下進(jìn)行高速數(shù)據(jù)傳輸。圖12顯示了DAC5670的等效互補(bǔ)數(shù)字輸入接口,適用于引腳DA_P[13:0]、DA_N[13:0]、DB_P[13:0]和DB_N[13:0]。

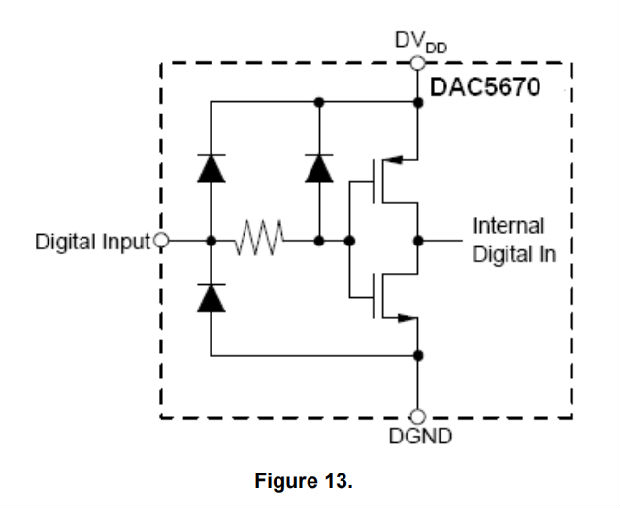

圖13顯示了DAC5670的等效CMOS/TTL兼容數(shù)字輸入的示意圖,適用于以下引腳:RESTART、LVDS_HTB、INV_CLK、SLEEP、NORMAL、a_ONLY、a_ONLY_INV和a_ONLY_ZS。

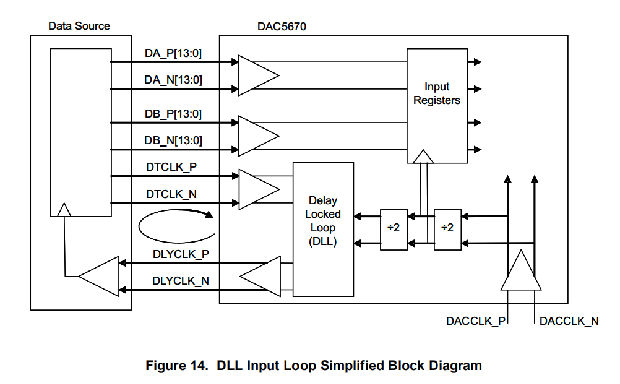

DLL使用

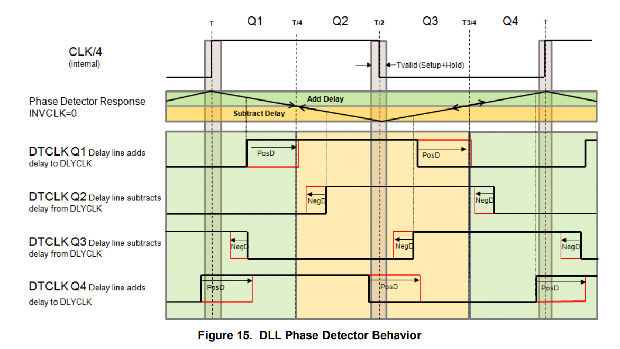

DAC5670以DAC采樣率計(jì)時(shí)。每個(gè)輸入端口的最大運(yùn)行速度為1.2gsps。DAC5670以輸入端口數(shù)據(jù)速率(DACCLK/4)的一半提供一個(gè)輸出時(shí)鐘(DLYLK),并監(jiān)視一個(gè)附加的參考位(DTCLK)。DTCLK作為反饋時(shí)鐘來調(diào)整接口時(shí)序。為了實(shí)現(xiàn)這一點(diǎn),DAC5670實(shí)現(xiàn)了一個(gè)DLL來幫助管理來自外部數(shù)據(jù)源的定時(shí)接口。與所有DLL一樣,DLL在延遲鏈長度、相位檢測(cè)器的實(shí)現(xiàn)和控制回路的帶寬方面的能力都有限制。DAC5670實(shí)現(xiàn)了基于正交的相位檢測(cè)器。這種方案允許動(dòng)態(tài)鏈接庫在達(dá)到正交時(shí)提供最大的設(shè)置或保持延遲裕度。當(dāng)內(nèi)部CLK/4與DTCLK相位相差90°時(shí),達(dá)到正交。此外,隨著操作頻率的降低,延遲線的固定長度限制了其改變延遲路徑以達(dá)到正交的能力(見圖15)。請(qǐng)注意,延遲線具有非對(duì)稱屬性。NegD范圍小于PosD范圍。從它的名義(重啟)位置,它可以延遲比它能減去的更多。

圖15顯示了相位檢測(cè)器和延遲線相對(duì)于DTCLK上升沿的初始位置的行為。有四個(gè)不同的象限來定義行為。每個(gè)象限表示DDR時(shí)鐘速率(2.4-GSPS情況下為600 MHz)除以4的周期。理想位置在象限1中具有DTCLK(因此數(shù)據(jù)位)的初始延遲。動(dòng)態(tài)鏈接庫的穩(wěn)定鎖定點(diǎn)在T/4,介于Q1和Q2之間。如果DTCLK的初始延遲在象限3或4,則可以斷言INV_ckpin以提高DLL獲得正交的能力。這個(gè)斷言將穩(wěn)定的求積點(diǎn)移到3T/4vs T/4的中心,如圖15所示。本質(zhì)上,增加延遲的區(qū)域變成減去延遲的區(qū)域,反之亦然。CLK/4的時(shí)鐘相位也會(huì)反轉(zhuǎn)。

在不適合使用DLL來管理定時(shí)接口的情況下,當(dāng)DLL保持在重新啟動(dòng)時(shí),可以使用相對(duì)于生成的DLYCLK輸出的DA和DB信號(hào)的固定設(shè)置和保持值。這是通過將RESTART斷言為logic high,并在使用DLL時(shí)使用外部定時(shí)接口的定時(shí)輸入條件來實(shí)現(xiàn)的。當(dāng)使用外部設(shè)置和保持定時(shí)時(shí),用戶不需要提供DTCLK。在這種情況下,DTCLK應(yīng)該偏向于有效的LVDS級(jí)別(參見圖3)。

設(shè)置/保持值是非傳統(tǒng)的,因?yàn)樗鼈儽硎緦?duì)生成時(shí)鐘的輸入的設(shè)置/保持(DLYCLK)。另外,設(shè)置/保持?jǐn)?shù)字表示可能比DACCLK或DACCLK/2周期更長的延遲。要計(jì)算到最近相鄰dlyck轉(zhuǎn)換的設(shè)置/保持值,用戶必須減去DACLCK/2周期的倍數(shù),直到設(shè)置小于DACCLK/2周期。可以從保持時(shí)間中減去相同的量。這些新的設(shè)置/保持值將取決于頻率。

時(shí)鐘輸入

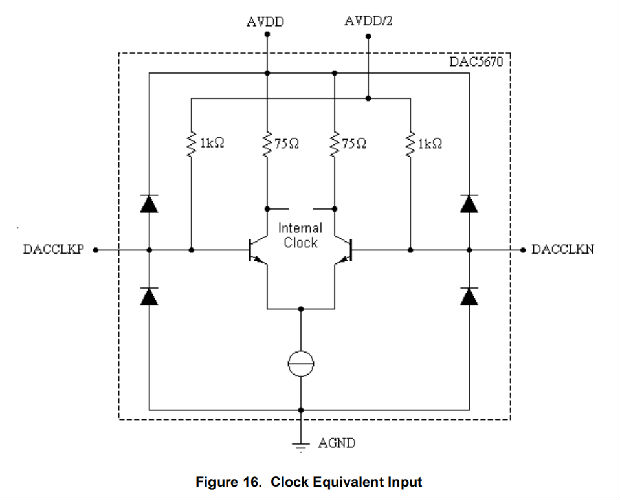

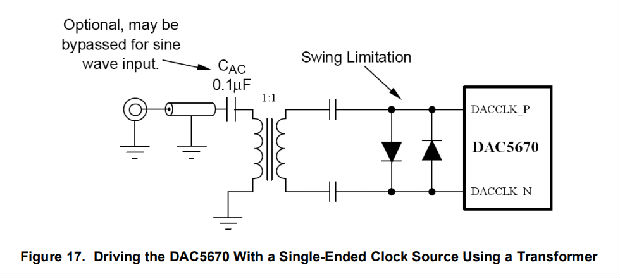

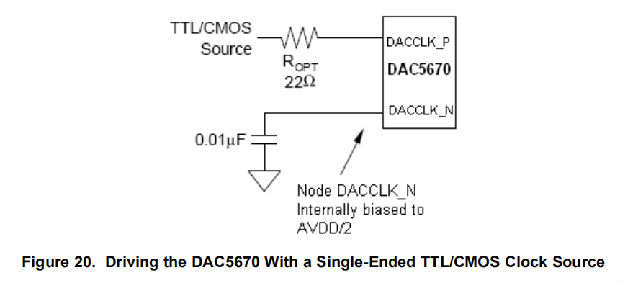

DAC5670具有與LVPECL兼容的差分時(shí)鐘輸入(DACCLKΜP、DACCLK_N)。圖16顯示了時(shí)鐘輸入緩沖器的等效示意圖。內(nèi)部偏置電阻將輸入共模電壓設(shè)置為AVDD/2,而輸入電阻通常為1kΩ。各種時(shí)鐘源可以與設(shè)備耦合,包括正弦波源(見圖17)。

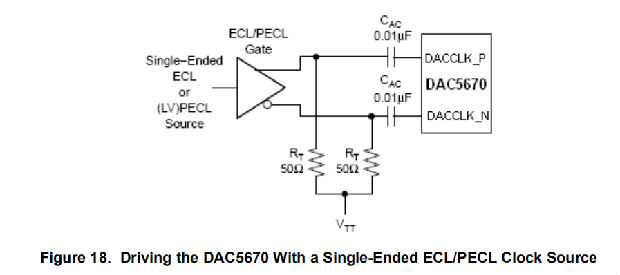

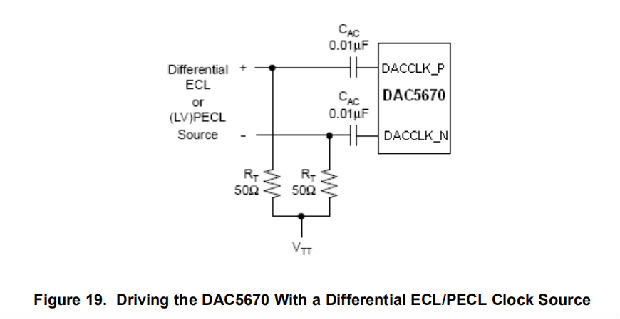

為了獲得最佳的交流性能DAC5670,用差動(dòng)LVPECL或正弦波源驅(qū)動(dòng)時(shí)鐘輸入,如圖18和圖19所示。在這里,電壓互感器的電位應(yīng)設(shè)置為驅(qū)動(dòng)器所需的端接電壓以及適當(dāng)?shù)亩私与娮瑁≧T)。DAC5670時(shí)鐘輸入也可以使用TTL/CMOS電平進(jìn)行單端驅(qū)動(dòng),以獲得較低的時(shí)鐘速率(參見圖20)。

DAC傳輸功能

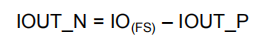

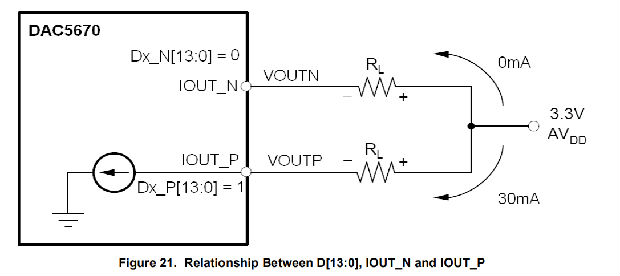

DAC5670具有電流匯輸出。電流通過IOUT_P和IOUT_N由Dx_P[13:0]和Dx_N[13:0]控制。為了便于使用,D[13:0]表示為Dx_P[13:0]及其補(bǔ)碼Dx_N[13:0]的邏輯位等價(jià)物。DAC5670支持直接二進(jìn)制編碼,D13作為MSB,D0作為LSB。當(dāng)所有D[13:0]輸入設(shè)為高時(shí),滿標(biāo)度電流流過IOUTP;當(dāng)所有D[13:0]輸入設(shè)為低時(shí),滿標(biāo)度電流流過IOUTN。IOUT_P和IOUT帴N之間的關(guān)系可表示為方程式1。

電流為全標(biāo)度輸出(5毫安)。因?yàn)檩敵黾?jí)是一個(gè)電流匯,電流只能從AVDD通過負(fù)載電阻RL流入IOUT峎N和IOUT_P引腳。

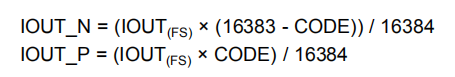

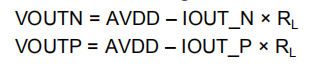

驅(qū)動(dòng)電阻負(fù)載的每個(gè)引腳中的輸出電流可以表示為圖21、方程式2和方程式3。

其中:

•CODE是DAC輸入字的十進(jìn)制表示

這轉(zhuǎn)化為IOUT_N和IOUT_P處的單端電壓,如方程式4和方程式5所示。

例如,假設(shè)D[13:0]=1且RL為50Ω,則引腳IOUT_N和IOUT_P之間的差分電壓可以表示為等式6到方程8,其中IO(FS)=20 mA。

如果D[13:0]=0,則IOUT_P=0 mA,IOUT_N=20 mA,差分電壓VDIFF=–1 V。

輸出電流和輸出電壓是互補(bǔ)的。與單獨(dú)測(cè)量每個(gè)輸出相比,差分測(cè)量的電壓將增加一倍。小心不要超過IOUT峈N和IOUT峎P引腳的合規(guī)電壓,以保持低信號(hào)失真。

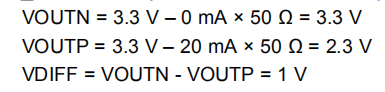

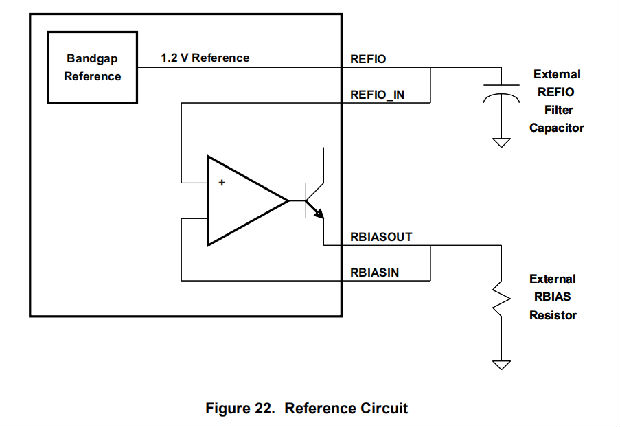

參考操作

DAC5670包括用于偏置滿標(biāo)度輸出電流的帶隙基準(zhǔn)和控制放大器。滿標(biāo)度輸出電流通過在引腳RBIASOUT和RBIASIN上施加一個(gè)外部電阻器RBIAS來設(shè)置。偏置電流IBIAS,通過電阻RBIAS,由片上帶隙基準(zhǔn)電壓和控制放大器定義。滿標(biāo)度輸出電流等于該偏置電流的32倍。因此,滿標(biāo)度輸出電流IOUTF可表示為:

其中:

•引腳REFIO和REFIO_IN處的VREFIO電壓

帶隙參考電壓提供1.2V的精確電壓。設(shè)計(jì)者應(yīng)將0.1μF的外部REFIO濾波器電容器連接到REFIO和REFIO_-IN引腳上進(jìn)行補(bǔ)償。

通過改變外部電阻RBIAS,滿標(biāo)度輸出電流可以從30毫安調(diào)整到5毫安。

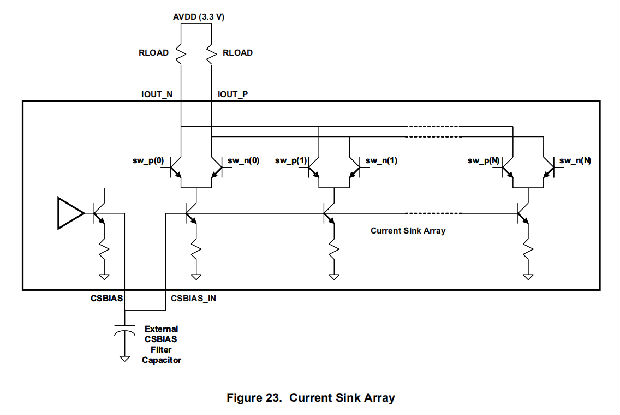

模擬電流輸出

圖23是帶有相應(yīng)開關(guān)的電流匯陣列輸出的簡(jiǎn)化示意圖。差分NPN開關(guān)將每個(gè)單獨(dú)NPN電流匯的電流引導(dǎo)至正輸出節(jié)點(diǎn)IOUT_P或其互補(bǔ)的負(fù)輸出節(jié)點(diǎn)IOUT_N。在DA_P[13:0]、DA_N[13:0]、DB_P[13:0]和DB_N[13:0]處顯示的輸入數(shù)據(jù)被解碼以控制sw_P(N)和sw_N(N)電流開關(guān)。

外部輸出電阻RLOAD連接到正極電源AVDD。

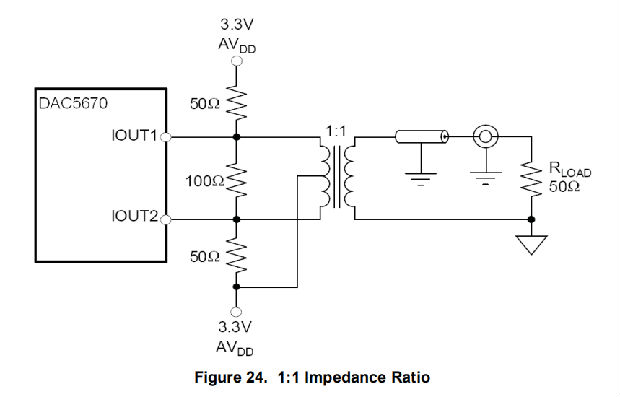

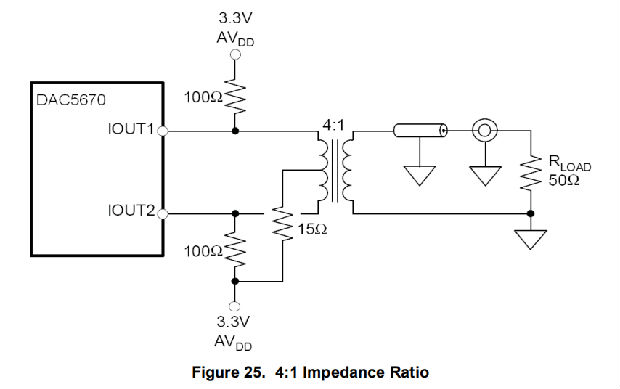

DAC5670可以很容易地配置為使用正確選擇的變壓器驅(qū)動(dòng)雙端接50Ω電纜。圖24和圖25分別顯示了1:1和4:1阻抗比配置。這些配置提供對(duì)共模噪聲源和偶數(shù)階失真分量的最大抑制,從而使DAC的輸出功率加倍。變壓器一次側(cè)的中心抽頭端接至AVDD,使IOUT帴N和IOUT帴P都能獲得直流電流。

睡眠模式

當(dāng)休眠引腳被斷言(高)時(shí),DAC5670進(jìn)入低功耗模式。

設(shè)備功能模式

輸入格式

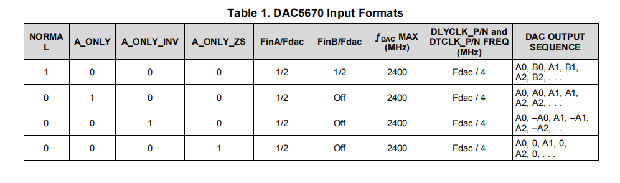

DAC5670有四種由四個(gè)互斥配置引腳選擇的輸入模式:正常、僅A U、A U ONLY U INV和A U ONLY U ZS。表1列出了每個(gè)配置的輸入模式、輸入采樣率、最大DAC采樣率(CLK輸入)和產(chǎn)生的DAC輸出序列。對(duì)于所有配置,DLYCLK_P/N輸出和DTCLK_P/N輸入都是dacclu P/N頻率除以4。

應(yīng)用與實(shí)施

注意

以下應(yīng)用章節(jié)中的信息不是TI組件規(guī)范的一部分,TI不保證其準(zhǔn)確性或完整性。TI的客戶負(fù)責(zé)確定組件的適用性。客戶應(yīng)驗(yàn)證和測(cè)試其設(shè)計(jì)實(shí)現(xiàn),以確認(rèn)系統(tǒng)功能。

申請(qǐng)信息

DAC5670是一個(gè)14位的DAC,最大輸入速率為2.4 GSPS。DAC5670也適合在較低的采樣率下工作,而無需使用DLL進(jìn)行輸入接口計(jì)時(shí)。

典型應(yīng)用

設(shè)計(jì)要求

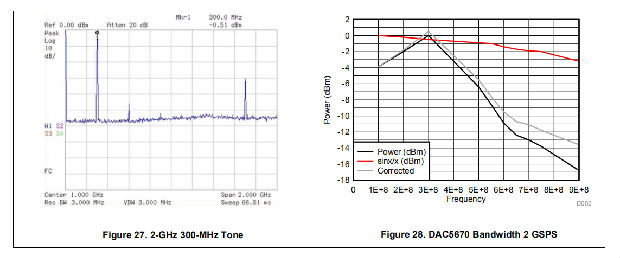

此示例使用2 GHz的DACCLK速率,信號(hào)輸出為300 MHz。

詳細(xì)設(shè)計(jì)程序

這個(gè)例子是以2-GHz的采樣率輸出300兆赫的音調(diào)。數(shù)據(jù)以1GHz雙數(shù)據(jù)速率應(yīng)用于A和B端口。滿標(biāo)度輸出電流設(shè)置為19.2 mA。

設(shè)備設(shè)置:

•低重啟

•LVDS U HTB(模式發(fā)生器源相關(guān))

•DLL鎖定所需的INV_CLK

•低睡

•正常高

•僅A_低

•僅A_INV低

•僅限于低

•dau P[0:13]、DA_N[0:13]、DB_P[0:13]、DB_N[0:13],源于模式發(fā)生器,產(chǎn)生300 MHz音調(diào),采樣深度65536

•RBIAS 2 kΩ接地

應(yīng)用曲線

電源建議

DAC5670使用單一的3.3V電源簡(jiǎn)化了設(shè)計(jì)要求。電源應(yīng)過濾掉可能存在的任何其他系統(tǒng)噪音。濾波應(yīng)特別注意輸出的相關(guān)頻率。

布局

布局指南

•DAC輸出端應(yīng)盡可能靠近輸出端。

•保持RBIA的路由短。

•去耦電容器應(yīng)盡可能靠近電源引腳。

•數(shù)字差分輸入必須為50Ω對(duì)地松散耦合,或100Ω差分緊密耦合。

•數(shù)字差分輸入必須長度匹配。

布局示例

安芯科創(chuàng)是一家國內(nèi)芯片代理和國外品牌分銷的綜合服務(wù)商,公司提供芯片ic選型、藍(lán)牙WIFI模組、進(jìn)口芯片替換國產(chǎn)降成本等解決方案,可承接項(xiàng)目開發(fā),以及元器件一站式采購服務(wù),類型有運(yùn)放芯片、電源芯片、MO芯片、藍(lán)牙芯片、MCU芯片、二極管、三極管、電阻、電容、連接器、電感、繼電器、晶振、藍(lán)牙模組、WI模組及各類模組等電子元器件銷售。(關(guān)于元器件價(jià)格請(qǐng)咨詢?cè)诰€客服黃經(jīng)理:15382911663)

代理分銷品牌有:ADI_亞德諾半導(dǎo)體/ALTBRA_阿爾特拉/BARROT_百瑞互聯(lián)/BORN_伯恩半導(dǎo)體/BROADCHIP_廣芯電子/COREBAI_芯佰微/DK_東科半導(dǎo)體/HDSC_華大半導(dǎo)體/holychip_芯圣/HUATECH_華泰/INFINEON_英飛凌/INTEL_英特爾/ISSI/LATTICE_萊迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_國民技術(shù)/NEXPERIA_安世半導(dǎo)體/NXP_恩智浦/Panasonic_松下電器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半導(dǎo)體/TD_TECHCODE美國泰德半導(dǎo)體/TI_德州儀器/VISHAY_威世/XILINX_賽靈思/芯唐微電子等等

免責(zé)聲明:部分圖文來源網(wǎng)絡(luò),文章內(nèi)容僅供參考,不構(gòu)成投資建議,若內(nèi)容有誤或涉及侵權(quán)可聯(lián)系刪除。

Copyright ? 2002-2023 深圳市安芯科創(chuàng)科技有限公司 版權(quán)所有 備案號(hào):粵ICP備2023092210號(hào)-1